全文HTML

--> --> -->目前, 二维层状材料已被认为是制备高性能忆阻器最具潜力的一类候选阻变材料, 如MoS2[2-5], GaSe[6,7], h-BN[8], In2S3[9], Graphene[10], TiO2[11,12]和WO3[13-15]等. 在这些阻变材料中, 以MoS2为阻变材料的忆阻器不仅表现出极高的开关比和稳定性, 而且还展现了良好的非易失存储特性[16-18]. 二维半导体材料MoS2由于较高载流子迁移率、合适的带隙、良好的热稳定性, 以及与CMOS (互补金属氧化物半导体)工艺的良好兼容, 现已证明在场效应晶体管方面具有突出的优势. 如在室温环境下开关比超过108, 载流子迁移率达到700 cm2·V–1·S–1, 以及超低亚阈值摆幅[19-21]. 由于二维层状MoS2材料具有良好的电学和光学性质, 所以其既可用于忆阻器的阻变材料, 又可用于晶体管的沟道材料. 2018年, Sangwan等[2]首次在Si衬底上制备出单层MoS2记忆晶体管, 该器件有大的开关比、高的循环耐久性和长期的状态保持能力, 并且在单个阻态下有4个数量级的栅极可调性. 2020年, Lee 等[5]在之前实验的基础上制备了双栅控制的单层MoS2记忆晶体管阵列, 实现了人工神经突触的模拟, 设计的双栅控制结构有助于记忆晶体管在高度规模化的交叉集成电路中集成. 2019年, 四川师范大学的Yang [6]等采用机械剥离的GaSe制备了三端背栅结构的GaSe记忆晶体管, 并且利用Ag作为电极实现了器件非易失性的阻态开关转变(开关比达到5.3 × 105). 2019年, Yin 等[3]利用机械剥离法制备三层MoS2的记忆晶体管. 在电场调控下, 该器件的开关比可实现极宽的调谐范围(100—105); 在光场控制下, 通过增加光功率, MoS2记忆晶体管阻变材料的电学性能会有极大的提升; 当光场和电场同时控制时, 器件的开关比可进一步得到提升.

尽管单层或少层MoS2记忆晶体管在电场和光场调制下表现出良好的传输特性和阻变开关行为, 但可控制备单层或少层MoS2较为困难, 并且单层或少层薄膜会影响MoS2对光的吸收. 相比单层或少层MoS2, 多层MoS2具有较高的迁移率和驱动电流, 以及适中的禁带宽度(1.2—1.6 eV)[22,23], 而且多层MoS2的本征迁移率不随厚度发生变化[24], 可减少不同器件间的差异. 目前, 还鲜有文献报道光波长对记忆晶体管阻变特性的影响. 因此, 本文研究多层MoS2记忆晶体管在不同栅电压、光波长及其协同调控下的阻变开关特性和阻变机理. 研究发现, 多层MoS2记忆晶体管在电场和光场调控下表现出优异的阻变特性, 且具有更低的功耗和多种的调控方式.

图 1 多层MoS2记忆晶体管的结构示意图

图 1 多层MoS2记忆晶体管的结构示意图Figure1. Schematic diagram of multilayer MoS2 memtransistor

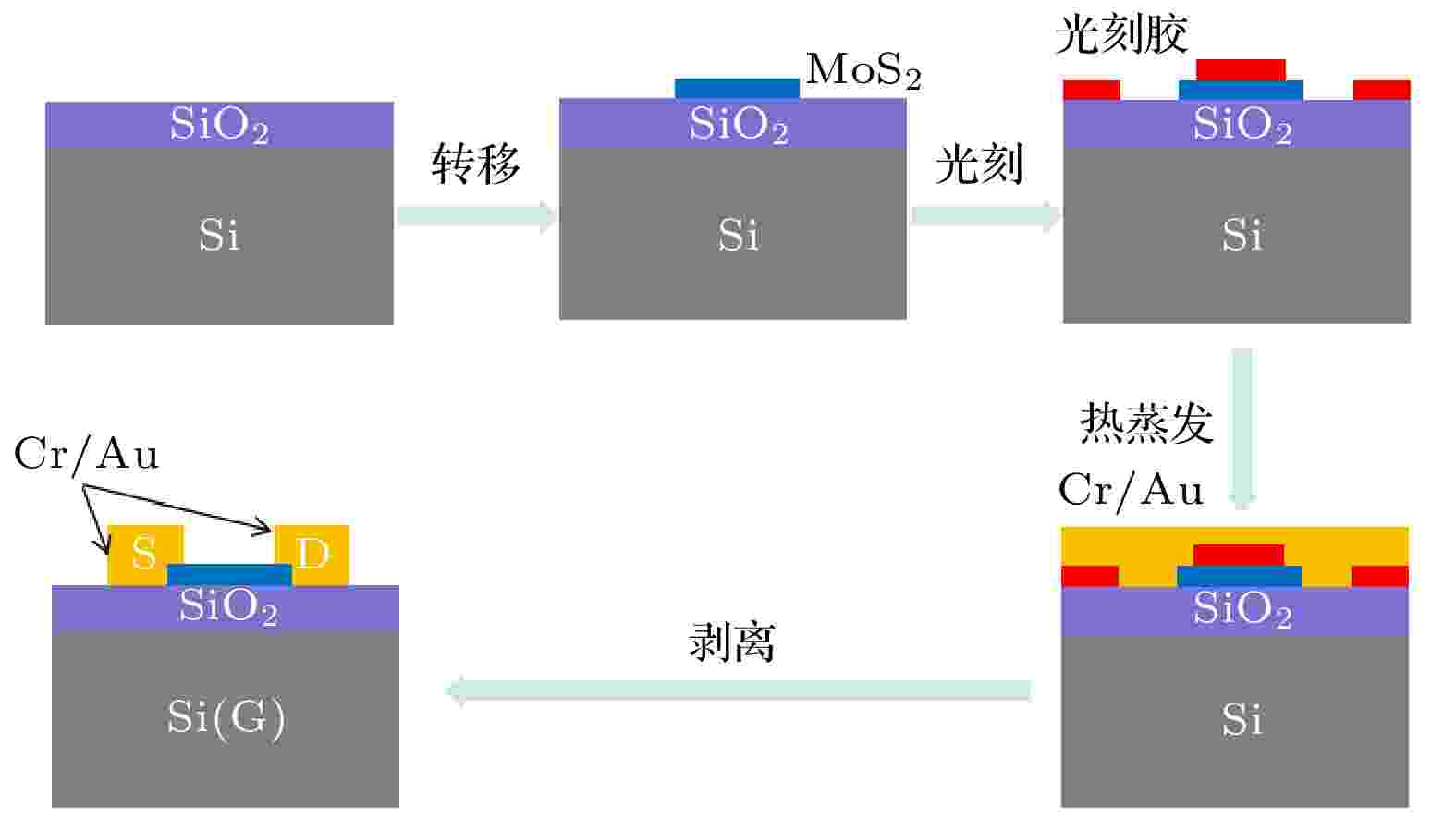

图 2 多层MoS2记忆晶体管的制备过程示意图

图 2 多层MoS2记忆晶体管的制备过程示意图Figure2. Diagram of the preparation processes of multilayer MoS2 memtransistor.

微机械剥离的多层MoS2的表面形貌由美国维易科精密仪器有限公司生产的DI Nanoscope Ⅳ原子力显微镜测试. 拉曼光谱由法国HORIBA Scientific公司生产的LabRAM HR Evolution光谱仪测量. 多层MoS2记忆晶体管的电学特性采用美国Keithley公司生产的4200A-SCS参数分析仪测试. 实验所用光源为中国中科微能(北京)科技有限公司生产的CME-TLS-X300F. 所有的测试均在室温、空气、电磁屏蔽环境下进行.

3.1.多层MoS2的形貌与表征分析

图3(a)是采用原子力显微镜(AFM)对剥离后的MoS2纳米片的表面形貌和厚度的表征. 从图3(a)可以看出, 多层MoS2厚度约为7 nm, 且表面平整均匀, 表明微机械剥离转移的MoS2具有良好的表面形貌[25]. 图3(b)是多层MoS2的拉曼光谱, 激光波长为532 nm. 图中显示MoS2的A1g模和

图 3 (a) 多层MoS2的AFM图像; (b) 多层MoS2的拉曼光谱

图 3 (a) 多层MoS2的AFM图像; (b) 多层MoS2的拉曼光谱Figure3. (a) AFM image of multilayer MoS2 ; (b) Raman spectrum of multilayer MoS2.

2

3.2.器件的电场调控及阻变开关机制

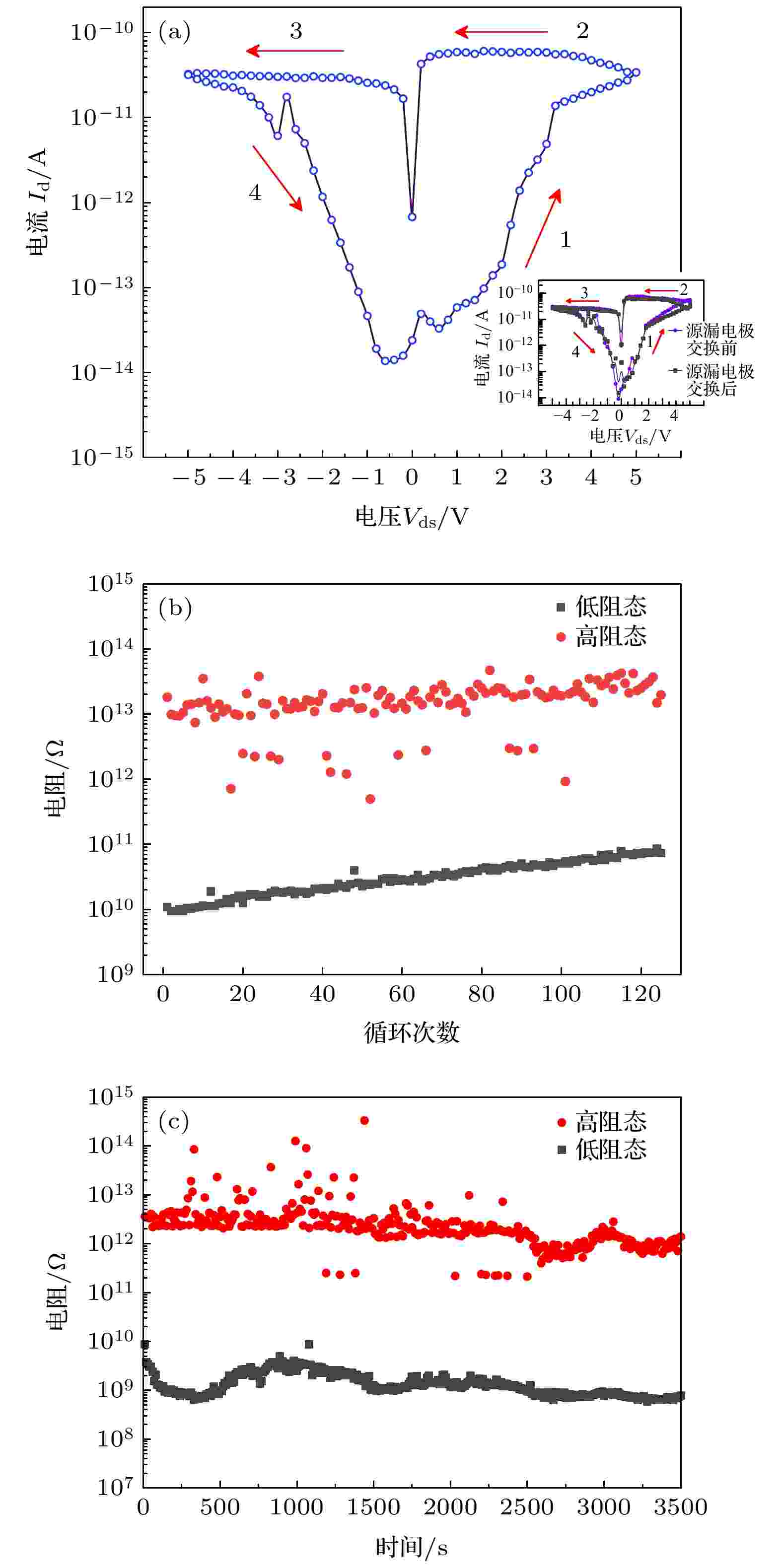

图4(a)是MoS2记忆晶体管栅压为0 V时, 施加5 V 至 –5 V漏源电压双向扫描的Id-Vds特性曲线, 图中箭头方向表示扫描电压顺序. 从图4(a)可以看出, 器件表现出明显的阻变特性, 而且在漏源正向电压下测得的 Id-Vds 特性曲线更好. 图4(a) 中插图显示器件源、漏电极交换测试的Id-Vds特性曲线, 两条曲线差异极小, 说明交换源、漏电极测试不会对器件的阻变性能产生影响. 当扫描电压顺序为0 V→+5 V时, 记忆晶体管的初始阻态因源漏电极与MoS2之间形成的肖特基势垒很高[3], 接触电阻很大, 表现为高阻态(HRS). 施加正向源漏电压时, 由于MoS2材料中存在的S空位以及在转移和光刻过程中引入一些杂质缺陷, 电子会被俘获填充到这些缺陷中直至饱和[4,27], 器件电阻保持HRS不变. 随着扫描电压的增大, 会导致源漏电极/n-MoS2界面处肖特基势垒高度逐渐降低, 且由电流产生的焦耳热会导致更多的电子穿过界面势垒[3], 器件电流急剧增大, 在设置电压Vset = 5 V时器件阻态从HRS转变为低阻态(LRS). 之后, 在+5 V→0 V 的扫描过程中, 器件的阻态一直保持LRS, 并且随扫描电压的降低器件的电流变化缓慢, 表明器件的阻变特性是非易失性的, 在Vds = 0.6 V器件的高低阻态开关比达到最大值(约103). 当0 V→–5 V反向电压扫描时, 记忆晶体管维持LRS不变, 当反向扫描电压增加到–5 V时, 导致器件的阻态从LRS重置为HRS. 在–5 V→0 V 的扫描过程中, 器件的阻态一直保持HRS. 由此可见, 制备的多层MoS2记忆晶体管表现出良好的非易失性双极性阻变特性, 与文献[2]报道的器件具有类似的阻变行为. 从图4(a)还可以看出, 相比于漏源电压负向扫描, 在正向压扫描时器件的电流开关比更大, 阻变特性更好. 图 4 在0 V栅压时多层MoS2记忆晶体管的阻变特性 (a) 5 V至–5 V源漏电压扫描下器件Id-Vds曲线(插图: 器件在源极和漏极交换测试前后的Ids-Vds曲线); (b) 连续125个循环中器件在Vds = 0.6 V时高低阻态的阻值变化; (c)器件在室温下高低阻态保持特性图

图 4 在0 V栅压时多层MoS2记忆晶体管的阻变特性 (a) 5 V至–5 V源漏电压扫描下器件Id-Vds曲线(插图: 器件在源极和漏极交换测试前后的Ids-Vds曲线); (b) 连续125个循环中器件在Vds = 0.6 V时高低阻态的阻值变化; (c)器件在室温下高低阻态保持特性图Figure4. Resistance characteristics of multilayer MoS2 memtransistor at Vg = 0 V: (a) Id-Vds characteristic of the device at cyclic sweeping of the Vds from 5 to –5 V (Inset: the Ids-Vds curves of the device before and after the source-drain electrode is exchanged); (b) the resistances of the device in high and low resistance states at Vds = 0.6 V during 125 cycles; (c) switching retention characteristics of the device at room temperature.

为了研究多层MoS2记忆晶体管的稳定性, 对器件进行了125次周期循环漏源电压扫描测试. 图4(b)给出了Vds 扫描电压在5 V至 –5 V范围内, 器件在125个周期循环测试中Vds = 0.6 V时高低阻态的电阻值. 从图4(b)可以看出, 随着循环次数的增加, 高低电阻值略微有上升趋势, 但总体保持稳定. 在经过125个周期循环后, 器件的电阻开关比仍然保持在103左右. 图4(c)为MoS2记忆晶体管在室温下高低阻态的保持特性(器件电阻的读取电压为0.6 V), HRS和LRS阻值随时间保持稳定, 但与图4(a)相比, 器件在放置一段时间后, 保持特性测试的高低阻态的阻值均有轻微降低, 可能是未封装的器件在空气环境下放置一段时间后其内部部分材料性能退化引起的. 在3500 s的时间内, 器件开关比始终还维持在103左右, 表明该记忆晶体管在连续工作的模式下具有良好的稳定性和耐久性.

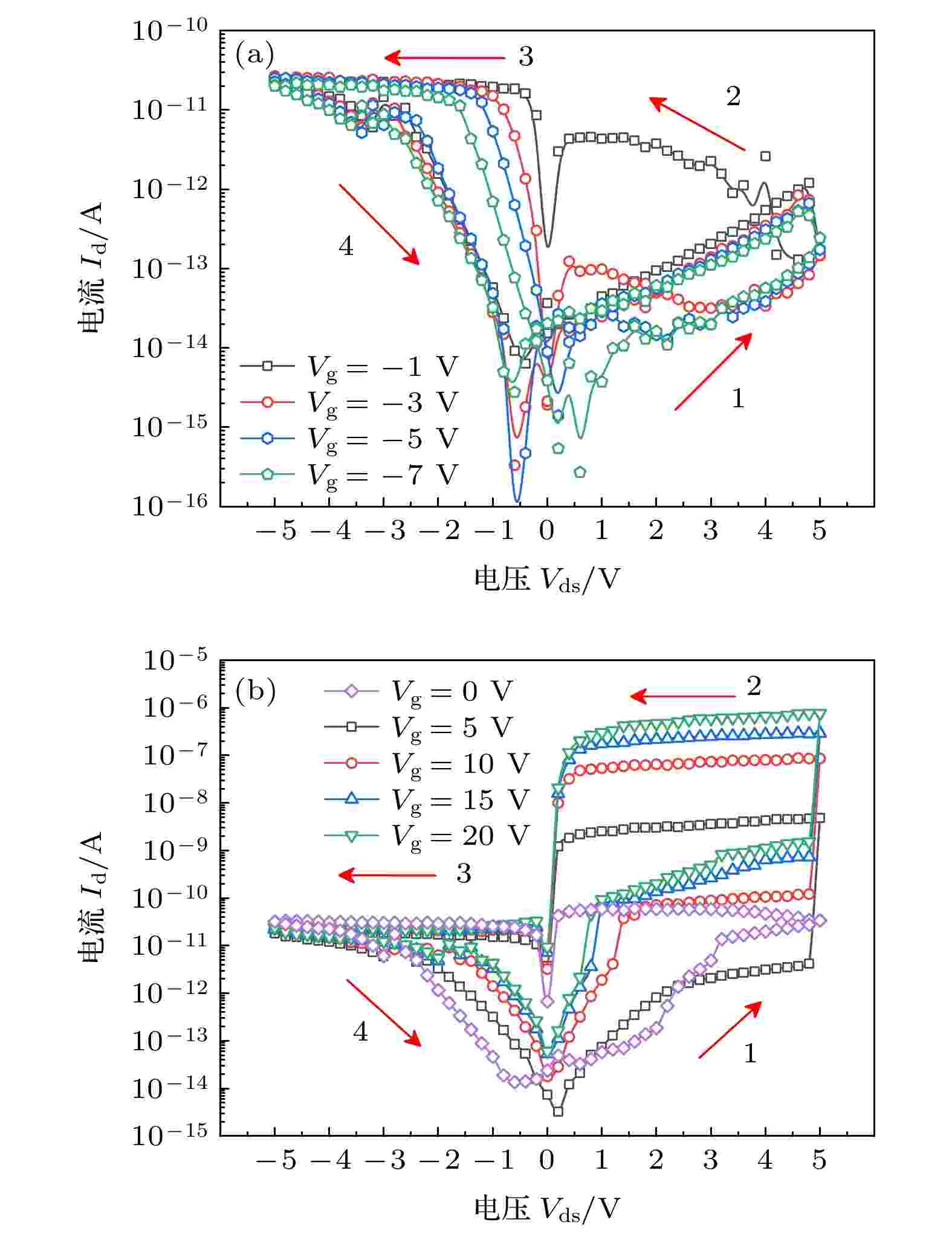

图5(a)是负栅压调控下MoS2记忆晶体管的Id-Vds特性曲线, 图中箭头方向为施加5 V 至 –5 V漏源电压双向扫描方向, 器件表现出非易失性双极性阻变行为. 相对于零栅压(如图4(a)), Id-Vds曲线整体会向低电流方向移动, 反映了高低阻态的阻值随负栅极电压的增加而增加, 其原因在于负栅压会导致源漏电极/n-MoS2界面处肖特基势垒高度的增加[2,3], 大大降低了MoS2沟道内的电子浓度, 从而导致HRS和LRS的电阻增加. 当Vds在0 V→+5 V→0 V扫描, Vg= –3, –5, –7 V时, 器件的LRS电流降低至10–14 A量级, 导致开关比随负栅极电压的增加严重降低, 在Vds = 0.6 V时开关比甚至接近1. 随着负栅压的增加, 当漏源电压0 V→–5 V→0 V反向扫描时, LRS的Id逐渐降低, HRS的Id几乎趋于相同变化, 导致器件在Vds为负值时的开关比逐渐减小.

图 5 不同栅压下多层MoS2记忆晶体管的阻变特性 (a) 栅压Vg = –1, –3, –5, –7 V时的Id-Vds曲线; (b) 栅压Vg = 0, 5, 10, 15, 20 V时的Id-Vds曲线

图 5 不同栅压下多层MoS2记忆晶体管的阻变特性 (a) 栅压Vg = –1, –3, –5, –7 V时的Id-Vds曲线; (b) 栅压Vg = 0, 5, 10, 15, 20 V时的Id-Vds曲线Figure5. Resistance characteristics of multilayer MoS2 memtransistor under different gate voltages: (a) Id-Vds characteristics of the device at Vg = –1, –3, –5, –7 V; (b) Id-Vds characteristics of the device at Vg = 0, 5, 10, 15, 20 V.

图5(b)是正栅压调控下MoS2记忆晶体管的阻变特性. 相对于负栅压(如图5(a)), 随着正栅压的增加, 当漏源电压0 V→–5 V→0 V反向扫描时, LRS的Id几乎不变化, HRS的Id逐渐增加. 随着正栅压的增加, 器件在Vds为负值时的开关比逐渐减小. 而当Vds在0 V→+5 V→0 V扫描时, 器件的HRS和LRS的Id都相应增加, 其原因在于正栅压会抑制源漏电极/n-MoS2界面处的肖特基势垒, 引起MoS2沟道内的电子浓度大大提高. 当正栅压不太高(Vg ≤ 7 V)时, 正栅压对器件的LRS影响更大, LRS的Id相对HRS的Id上升得更显著[2,3], 导致器件的电阻开关比随正栅压的增加而增加. 当正栅压较大(Vg ≥ 10 V)时, 随着正栅压的增加, HRS的Id上升得也很显著, 甚至会超过LRS的Id上升幅度, 导致器件的电阻开关比随正栅压的增加反而会缓慢减小.

表1列出了栅压从0 V增加到20 V时器件在Vds = 0.6 V时HRS和LRS的阻值和开关比. 当栅压Vg从0 V增加至7 V, HRS电阻由1.82 × 1013 Ω变化至7.40 × 1012 Ω, LRS电阻由1.08 × 1010 Ω变化至4.74 × 107 Ω, 相应开关比由103增加至105. 继续增大正栅压, HRS和LRS的阻值进一步降低, 器件的开关比缓慢减小, 但基本保持在105数量级. 这表明在多层MoS2记忆晶体管的背栅施加正栅压时, 会引起MoS2沟道内电子浓度的提升, 导致器件在LRS和HRS的电阻降低, 但不同正栅压对于HRS和LRS的影响程度不同. 当Vg = 0—7 V时, HRS对栅压不敏感, 其阻值变化很小, 而LRS的阻值会随Vg 的增加而显著减小, 从而引起开关比的极大提升, 当Vg = 7 V时开关比最大达1.56 × 105; 当Vg > 7 V时, 电阻开关比缓慢减小, 基本保持在105 量级. 由于记忆晶体管的阻变材料是多层MoS2, 相比于单层MoS2而言, 多层MoS2不仅有着更低的禁带宽度和较高的载流子浓度, 而且界面质量对于器件的影响也相对较小. 因此, 多层MoS2记忆晶体管仅需+5 V的设置电压和–5 V的重置电压, 便可完成HRS与LRS之间的相互转变; 在正向栅压调控时, 较低的调控电压可使器件沟道内的载流子浓度极大提高, 导致开关比的提升超过100倍(在Vg = 7 V时开关比达1.56 × 105). 相比文献[2]报道的单层MoS2记忆晶体管, 设置/重置电压±80 V, Vg = 40 V时开关比才约达102, 本文所制备的多层MoS2记忆晶体管不仅具有低的设置/重置电压, 还表现出栅极电压对器件电阻开关比的宽范围(100 —105)调控.

| 栅压 Vg/V | 0 | 5 | 7 | 10 | 15 | 20 |

| HRS阻值/Ω | 1.82×1013 | 2.85×1013 | 7.40×1012 | 1.87×1012 | 4.46×1011 | 2.72×1011 |

| LRS阻值/Ω | 1.08×1010 | 2.78×108 | 4.74×107 | 1.25×107 | 4.42×106 | 2.95×106 |

| 开关比 | 1.69×103 | 1.03×105 | 1.56×105 | 1.50×105 | 1.01×105 | 0.92×105 |

表1不同正栅压下器件的性能参数比较

Table1.Performance parameters of the device at different forward gate voltages.

2

3.3.器件的光场和电场协同调控

图6(a)是背栅电压为0 V时, 不同波长的光(各波长功率均为1. 2 mW)照射下多层MoS2记忆晶体管的Id-Vds特性曲线, Vds扫描顺序为0 V→+5 V→0 V→–5 V→0 V. 当波长为200 nm光照射时, 器件的HRS和LRS的阻态转变表现出了很明显的双极性阻变行为, 但与无光照时(如图4(a)所示)相比, 循环扫描回滞减小显著; 波长为400和600 nm光照射时, HRS和LRS的阻态转变与无光照时相比有较大差异. 当Vds由0 V→+5 V扫描时器件逐渐从HRS切换到LRS, 并在向0 V回扫时保持LRS, 但在Vds由0 V→–5 V扫描时, 器件切换到HRS, 随着反向电压增大到–5 V时, 又切换到LRS, 随后在–5 V→0 V回扫时器件保持LRS. 这表明400 和 600 nm光照射时, 器件的阻变行为由双极性转变成单极性. 从图6(a)还可以看出, 此波长的光照射时, 器件的电阻开关比很小. 当入射光的波长由800 nm增加到1200 nm时, 器件的阻变行为又从单极性转变成双极性, 且开关比又逐渐增加. 图 6 光场调控多层MoS2记忆晶体管的阻变特性 (a) 不同波长光照射时器件的Id-Vds曲线; (b) 不同波长光照射时器件的高低阻态阻值及开关比的变化

图 6 光场调控多层MoS2记忆晶体管的阻变特性 (a) 不同波长光照射时器件的Id-Vds曲线; (b) 不同波长光照射时器件的高低阻态阻值及开关比的变化Figure6. Resistance characteristics of multilayer MoS2 memtransistor under the control of the light field: (a) Id-Vds characteristics of the device under different wavelength illumination; (b) the resistances of the device in high and low resistance states and the corresponding ON/OFF radio under different wavelength illumination.

图6(b)是不同波长光照射下(各波长功率均为1.2 mW), 漏源电压Vds = 0.6 V时器件的高低阻态阻值及开关比的变化. 可以看出在λ ≤ 600 nm时器件HRS和LRS的阻值相比无光照时(高/低电阻为1.83 × 1012 Ω / 2.05 × 1010 Ω)均有一定幅度的降低, 尤其是在入射波长为400 和 600 nm时, HRS和LRS的阻值降低至106 Ω左右. 器件阻变行为受光场调控的影响, 主要归因于光电导效应(PCE)[28]. 多层MoS2具有适中的带隙(1.2—1.6 eV )和对紫外光、可见光有较强的吸收, 导致光照射到多层MoS2时产生大量的自由载流子被金属电极/MoS2的界面缺陷俘获, 从而极大地降低了肖特基势垒的高度. 在PCE作用下器件的HRS和LRS阻值迅速降低, 导致开关比急剧减小. 当入射波长大于800 nm时, HRS和LRS的阻值逐渐增加. 当入射波长增大至1200 nm时, 器件的高低阻态与无光照时相当, 开关比增至103. 其原因在于MoS2阻变层对红外波段的光吸收随着波长的增大而逐渐减弱, 导致阻变层电导率的逐渐减小; 而且随着光波长的增加, 光子的能量降低, 导致光子激发的电子-空穴对随之减少, 从而引起高低阻态的电阻逐渐增大, 但与LRS阻变相比, 器件在HRS时的阻值增加更快. 因而, 在红外光波照射时, 随着光波长的增加, 器件的电阻开关比增加.

图7是光场和电场协同调控MoS2记忆晶体管的阻变特性. 入射光的波长分别为200, 400和800 nm, 入射功率均为1.2 mW. 从图7可以看出, 当入射光波长为200 nm时, 多层MoS2对其光吸收较强, 导致沟道内光生载流子的浓度迅速升高, 从而在器件的高低阻态产生较高电流, 引起开关比的严重减小; 此外, HRS和LRS对不同正栅压的响应程度不同, 在正栅压下, MoS2沟道内的电子浓度增加, 且源漏电极处肖特基势垒被抑制. 当栅压在0—15 V时, 栅压对HRS影响很微弱, 其阻值几乎保持不变. 但栅压对LRS影响很显著, 其阻值从4. 9 × 108 Ω降低至3.1×106 Ω. 因此, 开关比随正向栅压的增大而增大, 当栅压增至15 V时开关比接近103; 当继续增加栅压至20 V时, 沟道内载流子浓度趋于饱和, 栅压对HRS和LRS的调控能力减弱, 器件开关比基本保持稳定; 当加负栅压时, 随着负栅压的增加, 沟道载流子浓度持续减小, HRS和LRS阻值增大, 器件的开关比降低(< 2.6). 当入射光波长为400 nm时, 由于MoS2对光的强烈吸收, 导致沟道内光生载流子浓度很高, 从而在正负栅压下HRS和LRS的电流都很大, 器件的开关比变得很小(< 2.20). 当入射光波长增大至800 nm时, 由于MoS2对长波光的吸收逐渐减弱, 沟道载流子浓度逐渐降低, 导致高/低电阻升高至4.12 × 1012 Ω / 8.24 × 109 Ω. 在负栅压调控下, 此时光照对器件的影响极小, 且负栅压逐渐增大会引起源漏电极/n-MoS2界面处肖特基势垒高度的增加, 导致HRS和LRS电阻略有增加. 但在正栅压的调控下, 器件的LRS阻值(相比于零栅压时)急剧减小, 而HRS对栅压不敏感. 因此, 在20 V的正栅压下开关比达4.8 × 104. 相比仅正栅压调控, 器件的开关比虽略有下降, 但可实现光波长对器件的阻变特性调控, 增加了器件的调控手段.

图 7 波长为200 , 400和800 nm光照射时, 器件高低阻态的阻值随栅压的变化(a)和电阻开关比随栅压的变化(b)

图 7 波长为200 , 400和800 nm光照射时, 器件高低阻态的阻值随栅压的变化(a)和电阻开关比随栅压的变化(b)Figure7. For incident light with 200, 400 and 800 nm wavelengths, (a) the resistances of the device versus Vg in high and low resistance states and (b) the ON/OFF radio versus Vg.

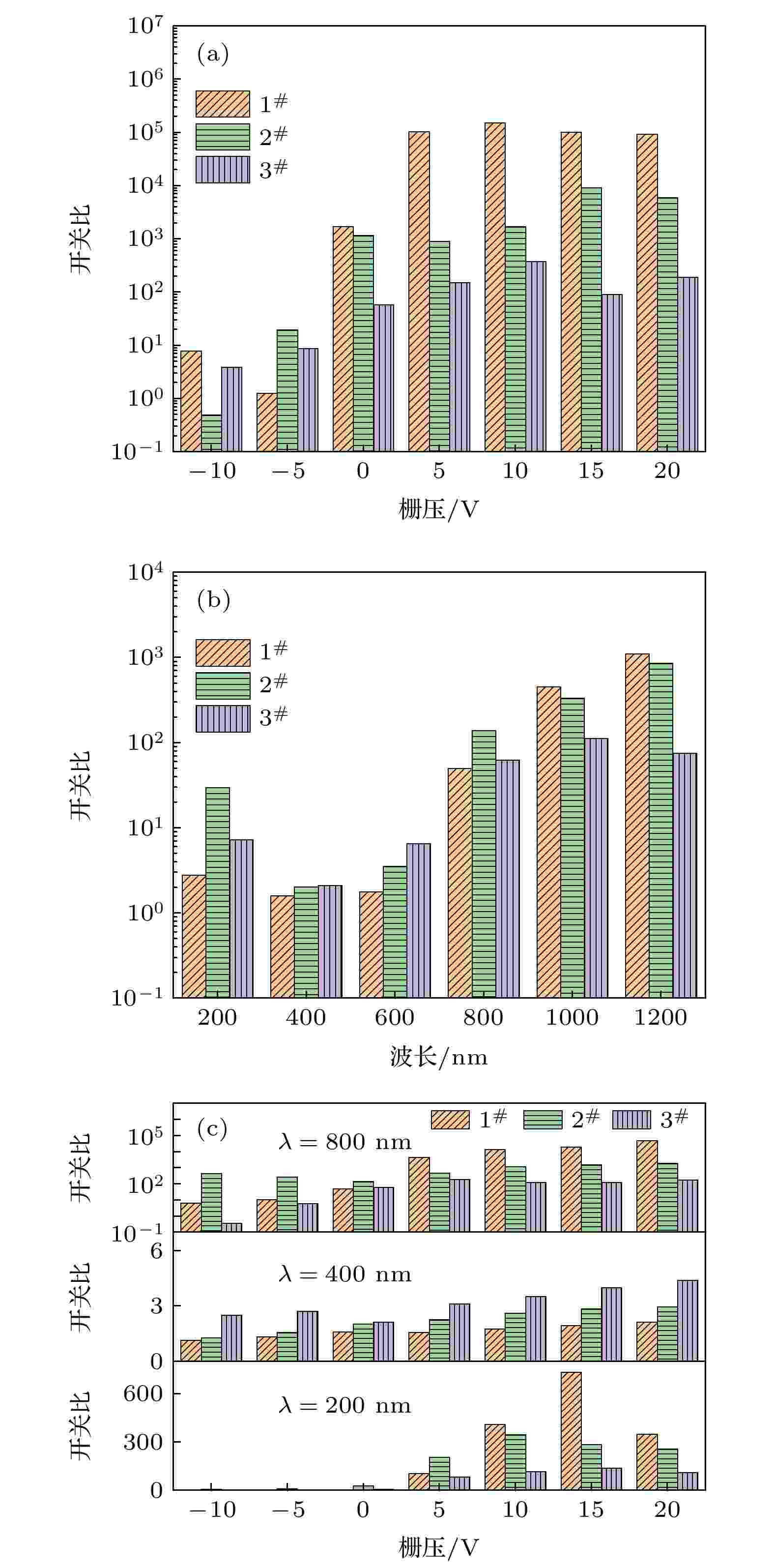

最后, 为了分析器件之间的性能差异, 在相同工艺下制备了2#和3#器件, 并与1#器件(图1—图7的测试器件)进行比较. 由图8(a)可知, 所有器件在Vg > 0 V时开关比均有一定提升; 在Vg < 0 V时开关比随负栅压呈急剧降低趋势. 这种变化趋势与图5(a)和图5(b)中基本一致, 均是正负栅压对源漏电极/n-MoS2界面处肖特基势垒高度的调制而引起的. 图8(b)显示了在不同波长光照下器件开关比的变化(光照功率保持在1.2 mW), 研究表明光照的波长对器件的阻变行为有强烈的调控能力, 可实现开关比在较宽范围内变化. 图8(c)则给出了3个器件在光场和电场协同调控下的阻变特性, 入射光的波长分别为200, 400和800 nm, 功率均为1.2 mW. 可以发现在不同波长和栅压组合调控下器件的开关比均可实现大范围调节, 且光场和电场组合调控对3个器件的影响趋势基本一致. 综合图8结果可知, 不同器件之间开关比的差异, 可以归因于微机械剥离转移得到的多层MoS2厚度和宽度有细微偏差, 以及在转移、光刻中引入的杂质缺陷具有不确定性等. 以上分析表明, 多层MoS2记忆晶体管具有良好的均一性, 并且在电场、光场以及组合调控时3个器件阻变性能的变化趋势基本一致.

图 8 不同器件之间的性能对比 (a) 器件在不同栅压下开关比的变化; (b) 器件在不同波长下开关比的变化; (c) 器件在200, 400 和800 nm光照射时, 开关比随栅压的变化

图 8 不同器件之间的性能对比 (a) 器件在不同栅压下开关比的变化; (b) 器件在不同波长下开关比的变化; (c) 器件在200, 400 和800 nm光照射时, 开关比随栅压的变化Figure8. Performance comparison between different devices: (a) Switching ratio of the devices under different gate voltages; (b) switching ratio of devices at different wavelengths; (c) switching ratio varies with gate voltages at illumination wavelengths of 200, 400 and 800 nm.