全文HTML

--> --> -->目前, 研究IGZO TFT背板静电放电(electrostatic discharge, ESD)问题的文献不多. 仅有的报道主要针对单个IGZO TFT器件进行TLP (transmission line pulse)或者HBM (human body model)测试分析, 找出ESD影响因素并提出ESD鲁棒性高的器件结构与保护结构[11-15]. IGZO TFT器件发生ESD破坏的一个路径是源漏极金属与栅极金属之间形成漏电通道. 这种漏电通道同样存在于数据线跨过扫描线的交叉位置. 所以, IGZO TFT器件的抗ESD击穿能力需要与层间Cu互连交叉处的抗ESD击穿能力进行匹配设计, 才能实现高鲁棒性的IGZO TFT背板.

IGZO TFT背板的数据线Cu互连与扫描线Cu互连之间隔着SiNx/SiO2绝缘层. 从扫描线到数据线的层间Mo/Cu:SiNx/SiO2:Mo/Cu结构中, 扫描线Cu金属扩散进入SiNx/SiO2绝缘层, 同时数据线Cu金属扩散进入SiO2绝缘层, 会引起数据线和扫描线交叉处的抗ESD能力下降. 相比Mo/Al/Mo:SiNx:Mo/Al/Mo结构的a-Si TFT背板, IGZO TFT背板的线上抗ESD击穿电压下降了将近一个数量级别. IGZO TFT背板ESD破坏的位置, 常见于数据线跨过扫描线的爬坡处. 本文通过上下层Cu互连的金属扩散原理建立层间Cu互连的ESD破坏模型, 并针对性地提出实现高鲁棒性IGZO TFT背板的方法. 这些方法的对策有效性试验, 验证了本文提出的层间Cu互连ESD破坏模型的合理性.

2.1.数据线爬坡处Cu金属扩散仿真

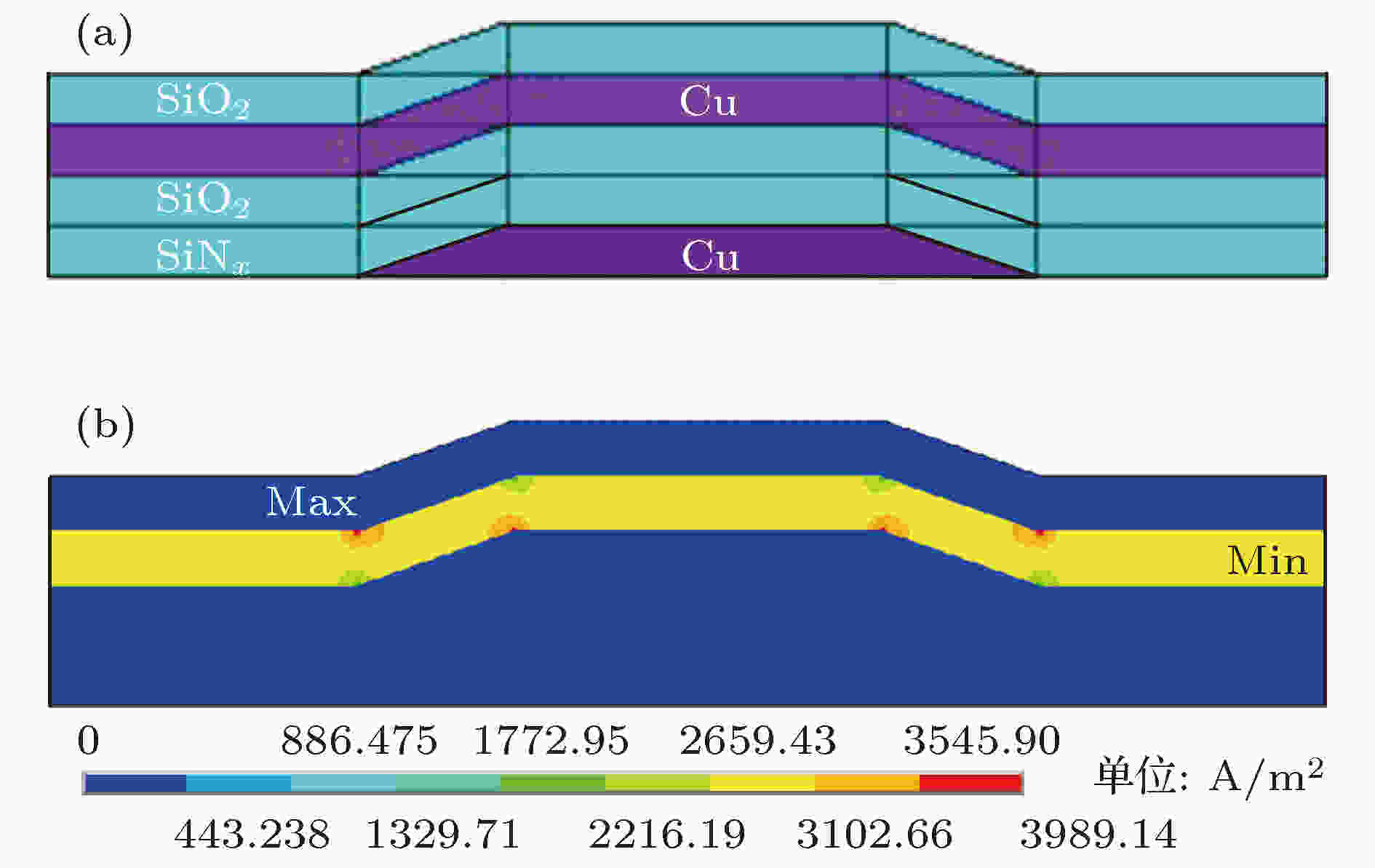

随着大尺寸显示面板像素分辨率的不断提高, 数据线Cu互连的宽度逐渐减小, 逼近光刻精度的限值. Cu互连宽度越细, 承受的电流密度越高. 同时, 显示面板分辨率越高, Cu互连的功耗越大, Cu互连上的工作温度越高. 在这些因素的共同作用下, 容易引起Cu金属迁移, 形成微空洞、微裂纹等损伤. Cu互连带电后会产生由热扩散主导的电迁移现象[16]. 在Cu互连的局部缺陷处, 需要考虑电迁移的风险. 特别在数据线跨过扫描线的爬坡位置, Cu金属容易发生过刻蚀现象, 导致Cu互连的截面积减少, 电流密度增加. 同时, 数据线跨过扫描线的上坡转折位置与下坡转折位置, 容易形成晶格缺陷, 导致电流密度增加.数据线Cu互连的电流密度最大情况一般出现在数据线输入端的第一行像素. 建立如图1(a)所示的第一行像素点的二维结构模型: 数据线Mo/Cu叠层的宽度为3.4 μm, 厚度为350 ?/3500 ?; Cu互连的上侧和下侧都是SiO2层. Cu和SiO2的具体属性参数如表1所列.

图 1 像素点Cu互连电流密度的ANSYS仿真 (a) 二维仿真模型; (b) 二维仿真结果

图 1 像素点Cu互连电流密度的ANSYS仿真 (a) 二维仿真模型; (b) 二维仿真结果Figure1. ANSYS simulation of current density of Cu interconnect in a pixel: (a) Two-dimensional simulation model; (b) two-dimensional simulation results.

| 材料 | 弹性模量/Pa | 泊松比 | 热导率/W·mK–1 | 热膨胀系数/ppm·K–1 | 电阻率/Ω·m | 质量密度/kg·m–3 |

| SiO2 | 69 × 109 | 0.17 | 7.6 | 0.54 × 10–6 | — | 2200 |

| Cu | 119 × 109 | 0.326 | 398 | 17.5 × 10–6 | 1.7 × 10–8 | 8900 |

表1仿真模型中不同材料的属性参数

Table1.Attribute parameters of different materials in simulation model.

第一行像素对应的数据线Cu互连传输通道, 电阻不到1 Ω, 通道上的电流大小由IGZO TFT的开态电流决定. 所以, Cu互连载荷加载方式以0.001 A的开态电流上限定义右端通入的电流, 同时左端定义0 V电压. 采用ANSYS进行稳态电流传导二维仿真, 所以选择单元类型为plane67. 从图1(b)所示的仿真结果可以看出, 电流在数据线Cu互连爬坡的拐角处出现拥挤, 最大电流密度为3989.14 A/m2. 数据线Cu互连拐角处的通量散度较大, 使得拐角处的Cu表面扩散速度远高于平坦区域的Cu互连内部扩散速度. 从仿真结果看, 平坦区域的Cu互连电流密度在2659 A/m2, Cu互连的电迁移风险较低.

线宽只有几个微米的数据线跨过扫描线, 需要一个上坡和一个下坡. 因为数据线Cu互连在拐角处的通量散度较大, 使得拐角处Cu金属容易扩散进入到周围的SiO2绝缘层中.

2

2.2.层间有效介质层降低机理

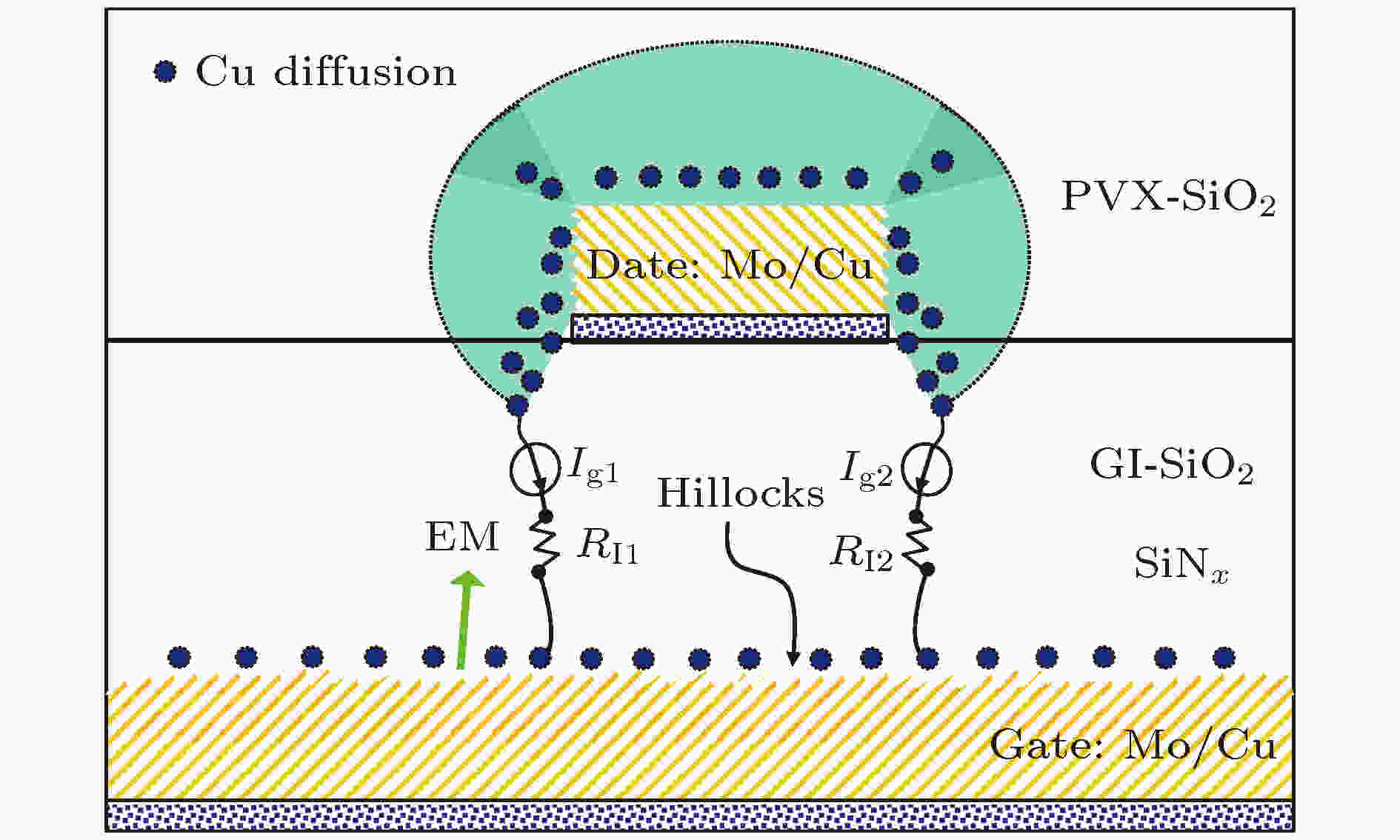

如图2所示, 数据线左右两侧的Cu金属被刻蚀后, 界面的平坦性被破坏, 界面损伤加重, 粗糙度增加, 使得Cu:SiO2界面的黏附性降低. 数据线Cu互连在刻蚀出图案后, 还要在上方用PECVD依次生长SiO2薄膜和SiNx薄膜, 用来保护IGZO有源层. 用作保护层的PVX-SiO2, 成膜温度是250 ℃, 退火温度是300 ℃. 在高温作用下, 数据线两侧的Cu金属会加速扩散到周围的PVX-SiO2和GI-SiO2层[17]. 图2的数据线截面对应数据线上坡或者下坡的转折位置. 这里的通量散度最大, Cu金属表面损伤最严重. 图 2 Cu扩散引起层间绝缘层有效厚度下降的机理

图 2 Cu扩散引起层间绝缘层有效厚度下降的机理Figure2. Mechanism of Cu diffusion induced decrease in effective thickness of insulation layer.

同时, 扫描线Cu:SiNx/SiO2界面的Cu表面hillocks凸起位置, 是Cu离子向SiNx/SiO2层扩散的拥挤点[18]. 扫描线Cu金属进入SiNx的扩散系数比进入SiO2的小. 扫描线Cu金属扩散进入SiNx层和数据线Cu金属扩散进入SiO2层同时作用, 使得扫描线与数据线之间的有效绝缘层厚度deff降低. 实际施加在绝缘层上的电场强度F增加.

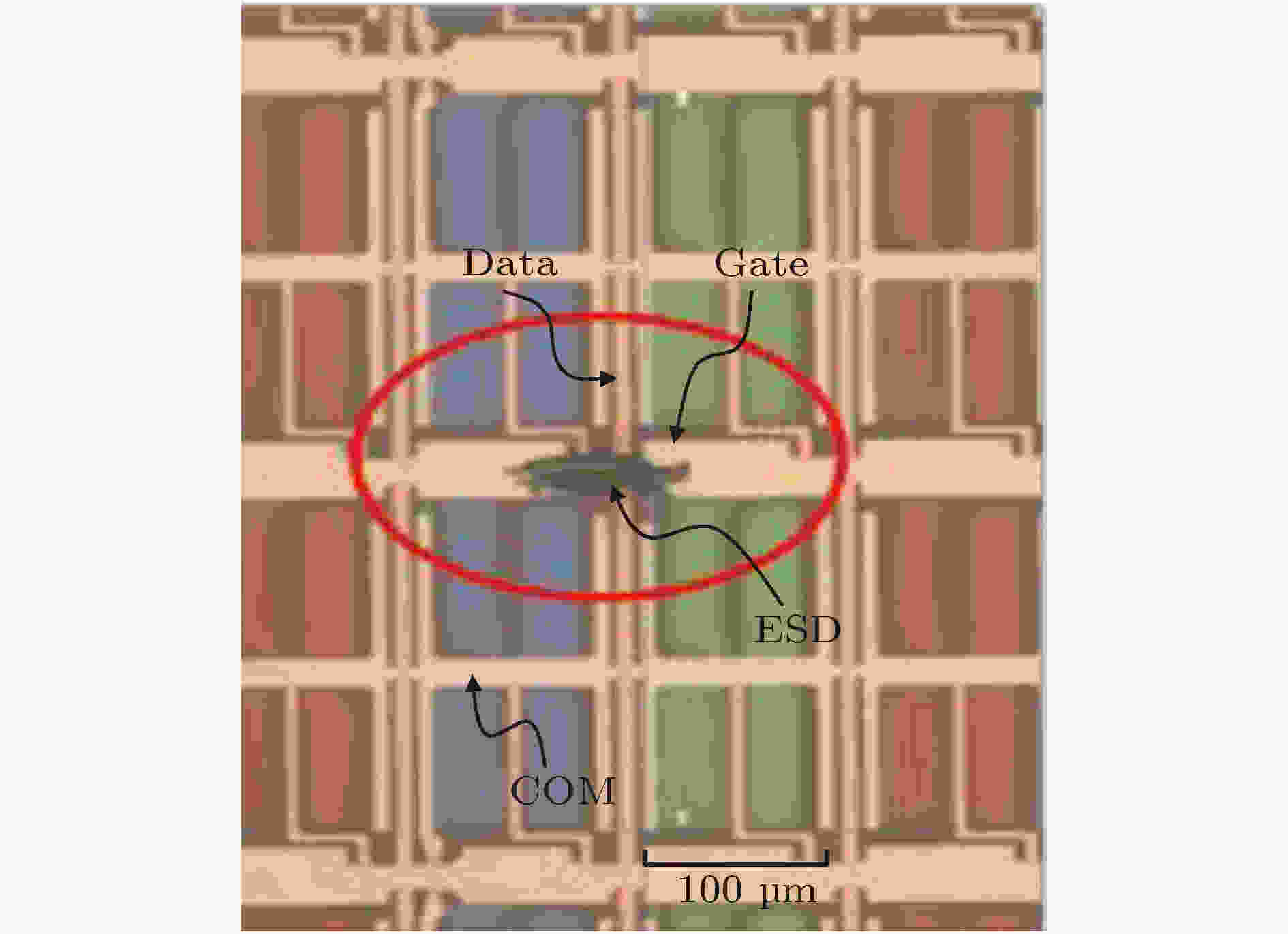

随着层间有效绝缘层厚度的减小, 电子很容易越过降低后的势垒, 在栅极绝缘层的陷阱态中进行跳跃导电, 甚至注入形成场致发射. 如果场致发射电流Ig1和Ig2接近限制电流, SiNx/SiO2栅极绝缘层的阻抗RI1和RI2将从高阻态变为低阻态, 丧失绝缘性能, 导致TFT器件失效[19]. 一种极端的表现是数据线和扫描线之间的压降V(t)达到几十伏特后, 由于电极反应产生大量的Cu离子, 分别向SiNx层和SiO2层进一步扩散. 因为Cu离子带正电, 在外加电压作用下的Cu离子向低电压一端快速扩散. Cu离子向SiNx层和SiO2层进一步扩散, 最后在扫描线和数据线之间形成细长的晶须, 使得数据线和扫描线之间短路[20]. 在短路的细长晶须上形成密集电流, 导致SiNx/SiO2绝缘层击穿烧毁, 如图3所示.

图 3 数据线与扫描线层间Cu互连的ESD破坏现象

图 3 数据线与扫描线层间Cu互连的ESD破坏现象Figure3. ESD damage of interlayer Cu interconnects between data line and gate line.

2

3.1.ESD保护电路的基本架构

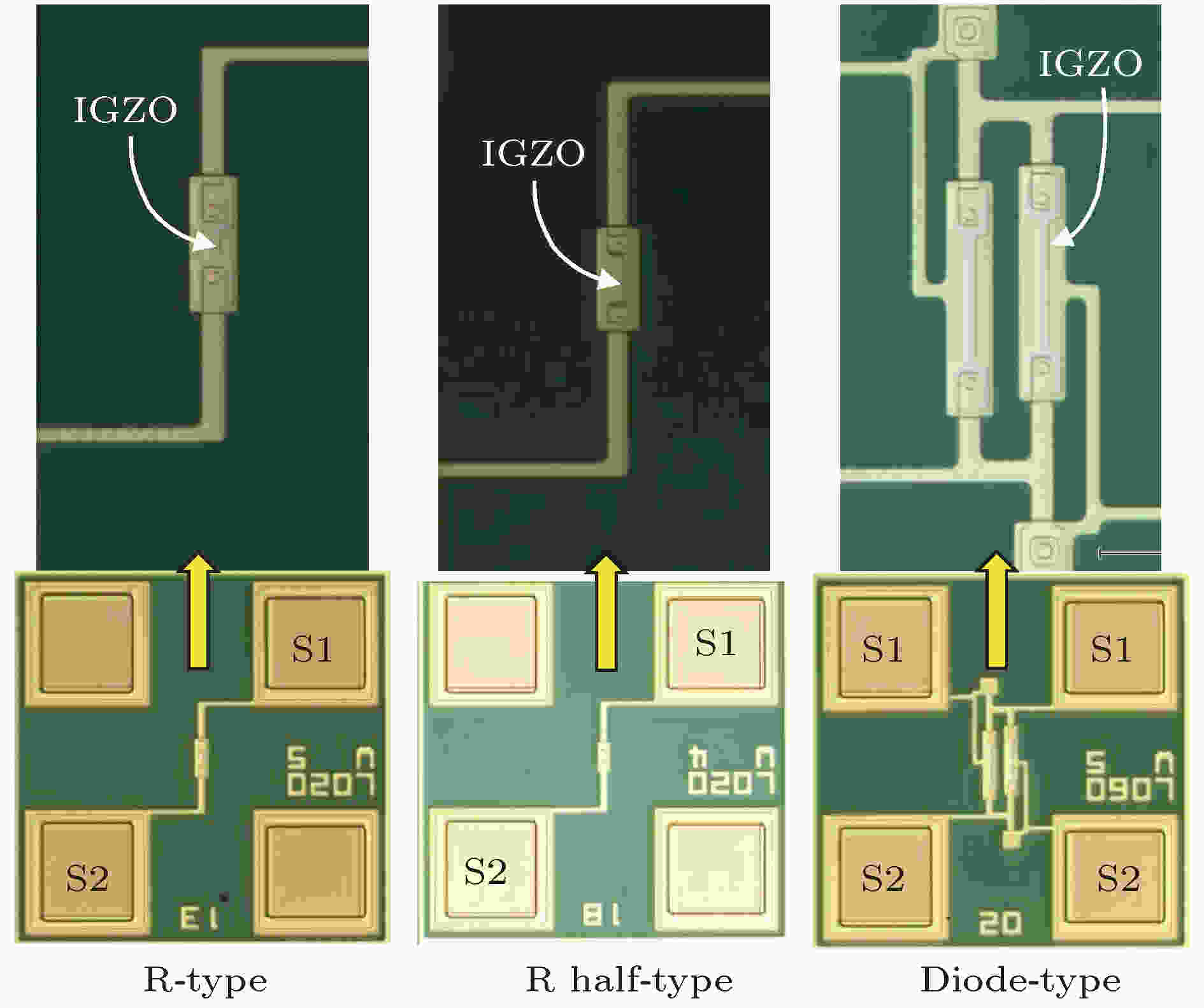

因为Cu金属扩散, IGZO TFT背板的ESD保护电路设计有别于传统的a-Si TFT工艺, 需要根据Mo/Cu:SiNx/SiO2:Mo/Cu的实际抗压能力, 设计对应的ESD保护电路. 图4给出了三种常用的ESD保护电路架构, 分别是R型保护架构、R half型保护架构和Diode型保护架构. R型和R half型保护架构的源漏极连接沟道有源层, 栅极悬置. 源极或者漏极出现瞬时高电压时, 器件就等效为电阻进行放电. Diode型保护架构是一对背对背连接的R型保护电路. 图 4 三种ESD保护架构的版图

图 4 三种ESD保护架构的版图Figure4. Layout of three ESD protection architectures.

基于IGZO TFT工艺的三种ESD保护电路, 在ESD器件两端施加0—200 V电压, 分别测量其电流, 对比三者的耐压能力. 耐压值高于栅极绝缘层的击穿电压才能起到较好的ESD防护作用.

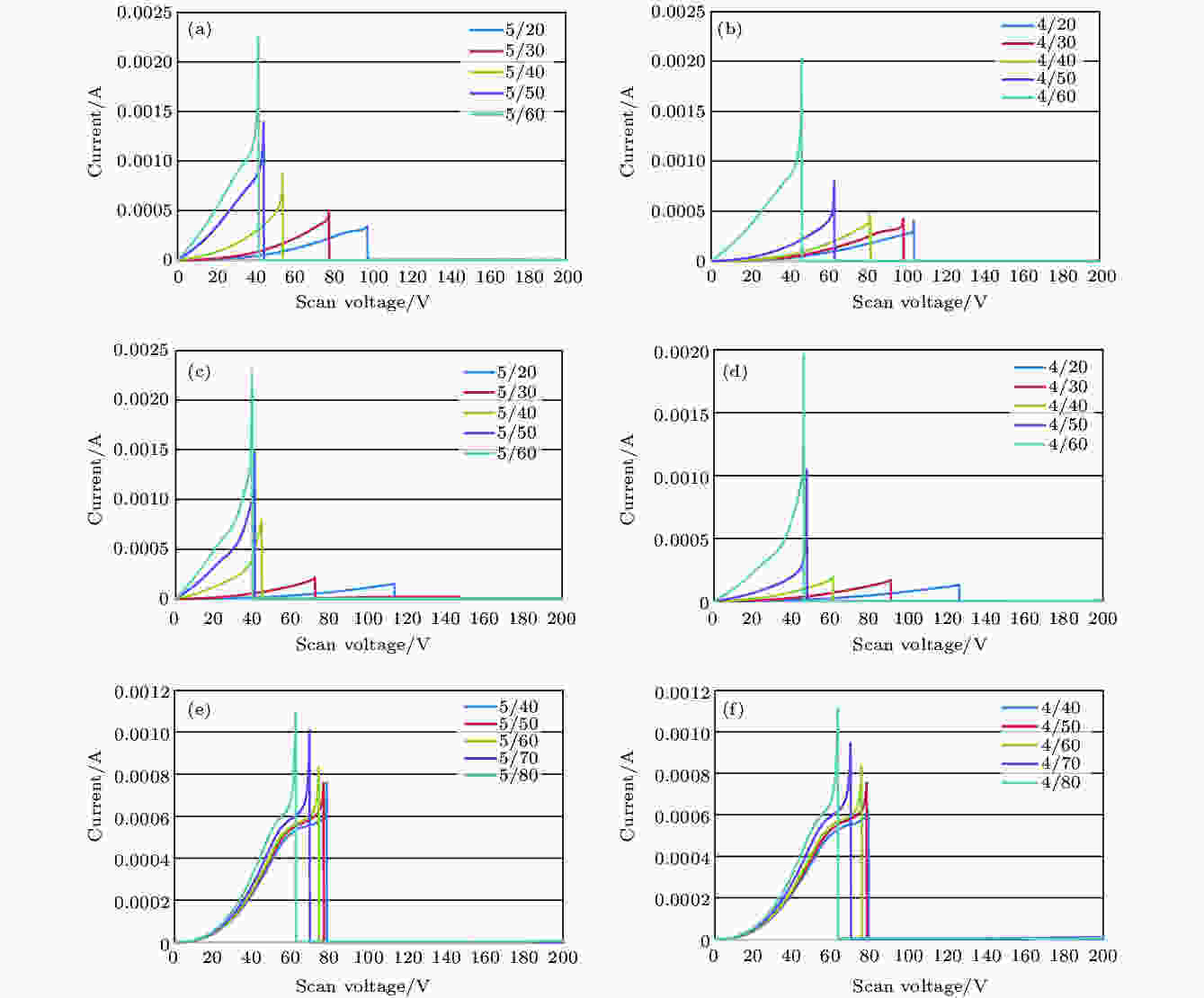

图5(a)和图5(b)分别是R型架构的ESD保护电路, 在器件的TFT沟道宽度W分别为5和4 μm时, 沟道长度L从20到60 μm对应的I-V曲线. 图5(c)和图5(d)分别是R half型架构的ESD保护电路, 在器件的TFT沟道宽度W分别为5和4 μm时, 沟道长度L从20到60 μm对应的I-V曲线. 根据测试结果, R half型与R型的I-V曲线规律基本相同. 随着器件的TFT沟道长度L的增加, ESD保护电路最大耐压能力由50 V增加至120 V, 大约是R型架构的1.5倍, 同时电流减小. 沟道宽度W越小, TFT的最大耐压值越大. 图5(e)和图5(f)分别是Diode型架构的ESD保护电路, 在器件的TFT沟道宽度W为5和4 μm时, 沟道长度L从40到80 μm对应的I-V曲线. 随着器件的TFT沟道长度L的增加, TFT最大耐压能力由60 V增加至80 V, 同时电流减小. 但是, TFT的耐压能力随沟道宽度W的变化并不明显. 与R型相比, Diode型架构的耐压能力较差, 但是电流较大.

图 5 三种类型ESD保护电路的I-V曲线 (a) W = 5 μm, R型; (b) W = 4 μm, R型; (c) W = 5 μm, R half型; (d) W = 4 μm, R half型; (e) W = 5 μm, Diode型; (f) W = 4 μm, Diode型

图 5 三种类型ESD保护电路的I-V曲线 (a) W = 5 μm, R型; (b) W = 4 μm, R型; (c) W = 5 μm, R half型; (d) W = 4 μm, R half型; (e) W = 5 μm, Diode型; (f) W = 4 μm, Diode型Figure5. Layout of three ESD protection architectures: (a) R-type I-V curves at W = 5 μm; (b) R-type I-V curves at W = 4 μm; (c) R half-type I-V curves at W = 5 μm; (d) R half-type I-V curves at W = 4 μm; (e) Diode-type I-V curves at W = 5 μm; (f) Diode-type I-V curves at W = 4 μm.

通过实验对比, 三种类型的ESD保护电路耐压能力都随沟道长度增加而增大, 与R型ESD相比, R half型ESD设计耐压能力更强; Diode型ESD器件的耐压能力较弱, 但是其在高电压下电流较大, 当三种器件的耐压值均高于栅极绝缘层击穿电压时, Diode型ESD保护电路的放电更快, 抗ESD能力更好.

2

3.2.IGZO TFT背板的抗ESD能力分析

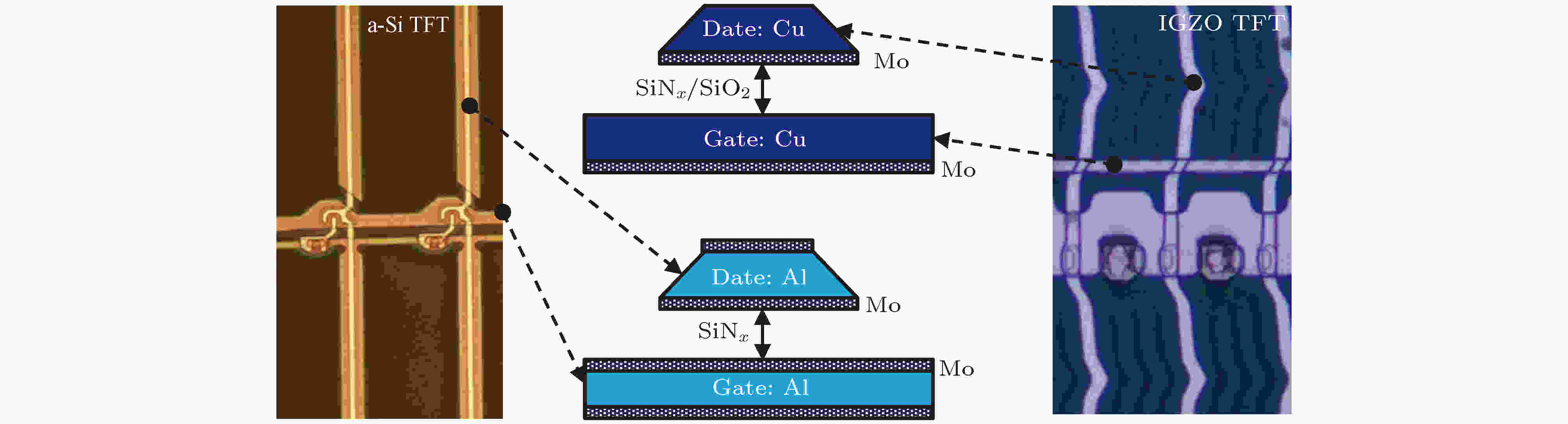

如图6所示, 传统a-Si TFT背板一般采用Mo/Al/Mo:SiNx:Mo/Al/Mo结构, 上下Mo阻挡层可以有效防止Al互连电迁移. TFT栅极绝缘层和背板的绝缘保护层都用致密性更高的SiNx薄膜, 可以降低金属在绝缘层中的扩散速度. a-Si TFT背板在阵列工艺的机台上, 静电电压达到1500 V都不会出现Al互连的ESD破坏现象. 但是, IGZO TFT背板的静电电压达到400 V左右可能出现Cu互连的ESD破坏现象. 图 6 数据线与扫描线层间结构比较

图 6 数据线与扫描线层间结构比较Figure6. Structural comparison between data line and scanning line.

直接对IGZO TFT背板Mo/Cu:SiNx/SiO2:Mo/Cu交叉处的数据线Cu互连和扫描线Cu互连施加一组持续增加的电压, 发现Mo/Cu:SiNx/SiO2:Mo/Cu结构的耐压极限在50—60 V之间. 同样对传统a-Si TFT背板Mo/Al/Mo:SiNx:Mo/Al/Mo结构的数据线Al互连和扫描线Al互连施加一组持续增加的电压, 发现Mo/Al/Mo:SiNx: Mo/Al/Mo结构的耐压极限在90—110 V之间.

所以, IGZO TFT背板的Mo/Cu:SiNx/SiO2:Mo/Cu结构与传统a-Si TFT背板的Mo:SiNx:Mo结构相比, 玻璃基板级的抗ESD能力下降近一个数量级, 互连级的抗ESD能力下降近60%. Cu互连的抗电迁移能力比Al强, 所以Cu互连一般省略上侧的阻挡层. 但是, Cu原子晶界扩散和界面扩散的激活能分别只有1.2 eV和0.7—1.0 eV, 小于Al的扩散激活能1.48 eV[21,22]. 所以, Cu会扩散进入SiNx/SiO2[7]. 这种扩散现象是造成IGZO TFT背板抗ESD能力下降的根本原因.

2

3.3.ESD保护电路的匹配设计

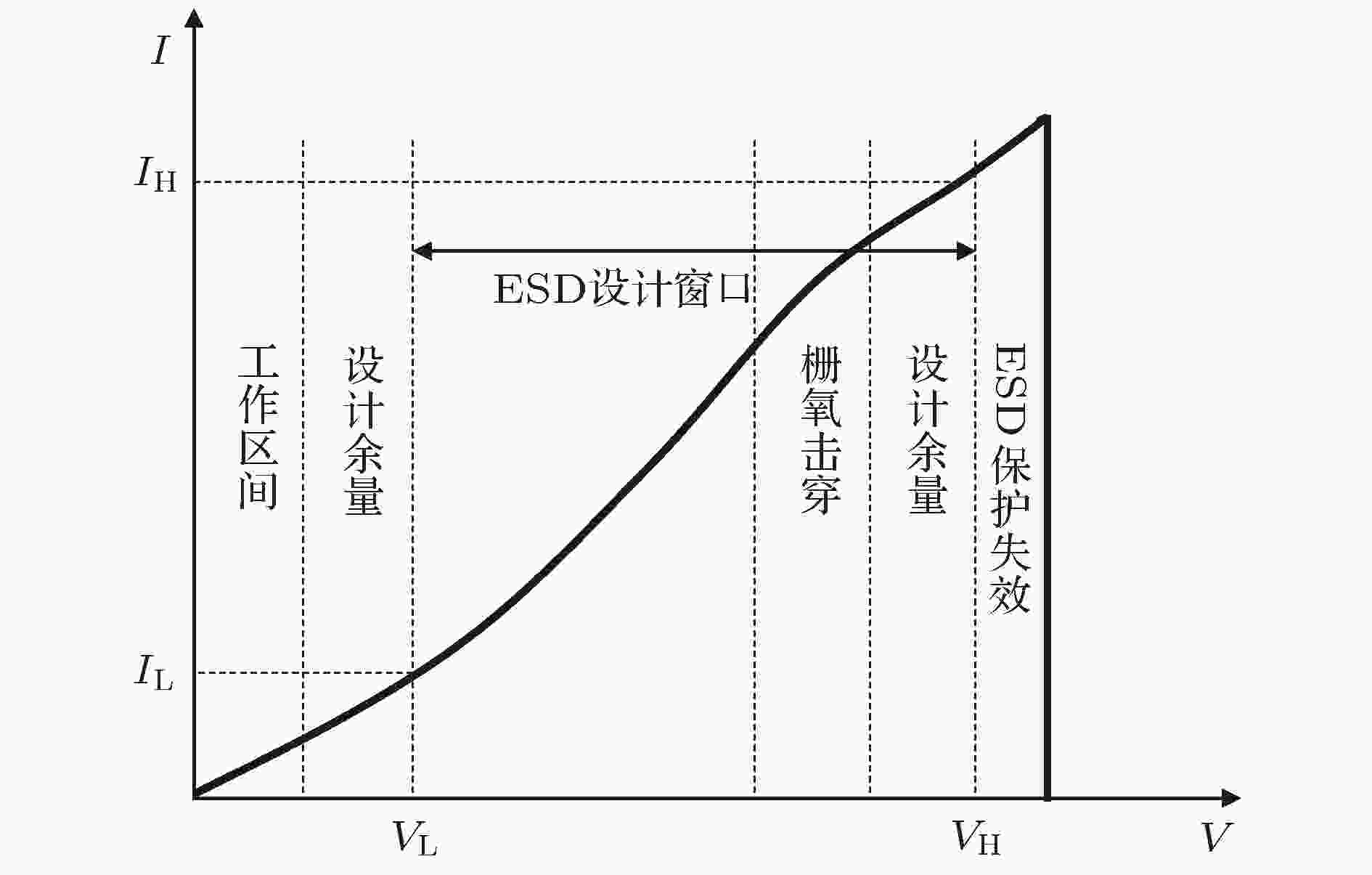

本文在Cu金属成膜与Cu金属界面处理等工艺优化的基础上, 提出高鲁棒性IGZO TFT背板的Cu互连周边ESD保护方法. 显示区周边ESD保护电路的设计要求数据线和扫描线层间Cu互连发生ESD击穿之前, 在互连线上积累的静电从ESD保护电路上先泄放掉. ESD保护电路设计需要按照严格的设计窗口来设计, 如图7所示. 其中, 触发电压VL为工作电压加上设计余量电压, 截止电压VH为栅极绝缘层击穿电压加上设计余量电压. 图 7 ESD保护电路设计窗口

图 7 ESD保护电路设计窗口Figure7. Design window of ESD protection circuit.

根据图7所示的ESD保护电路设计窗口, ESD设计窗口在VL到VH之间. VH大于Mo/Cu:SiNx/SiO2:Mo/Cu结构的耐压极限, VL大于器件工作电压. IL对应VL电压时的电流, IL的经验值低于10–4 A. IL不能太大, 以免影响器件的工作电压. IH对应电压为VH时的电流, 需要至少大于10–8 A, 电流越大其抗静电能力越好, 以保证积累的静电迅速导出.

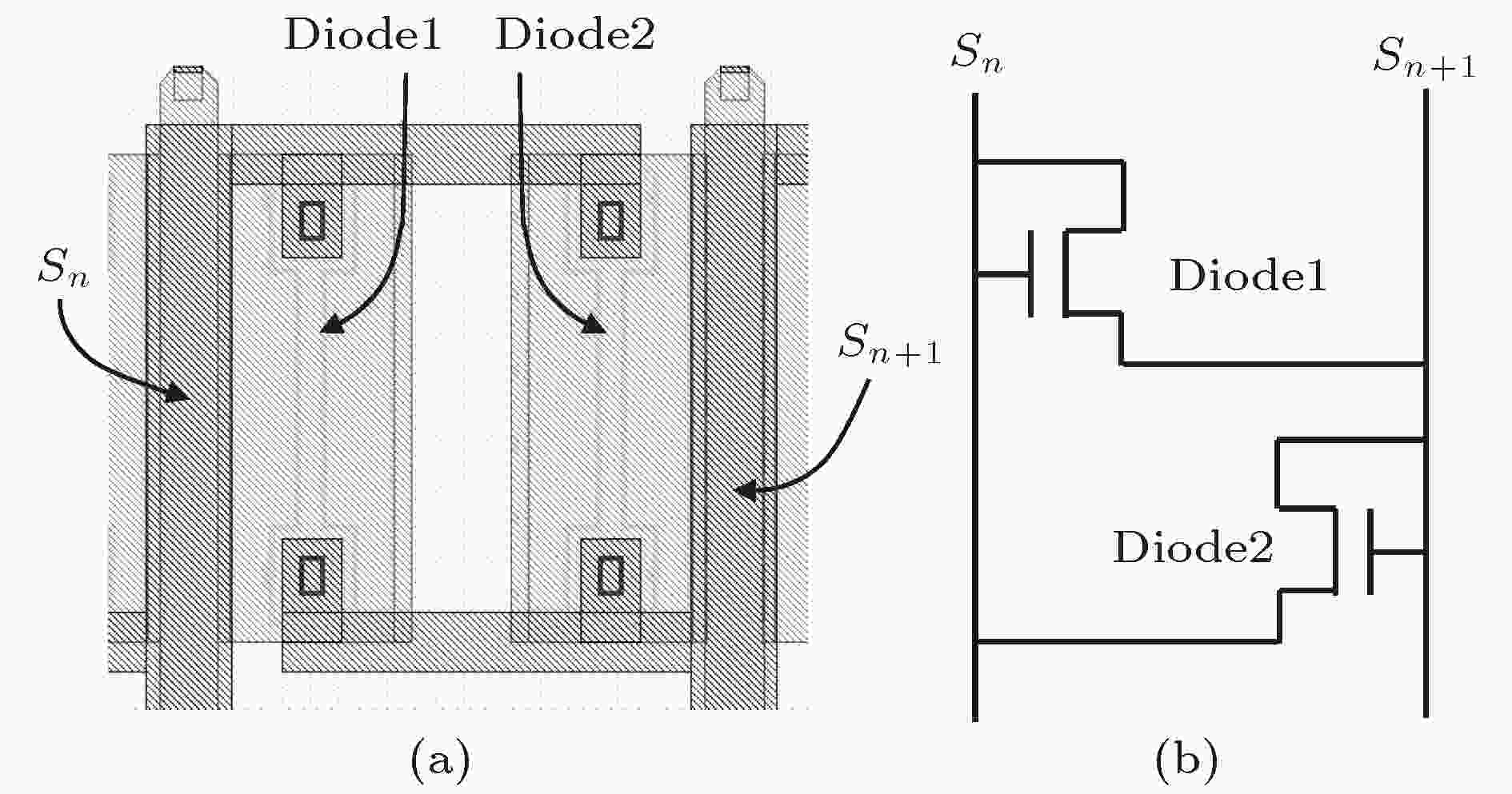

在三种类型的ESD器件中, R型保护架构的器件虽然IL较小, 但是IH较低, 其放电能力不及Diode型保护架构, 一般用于高压器件之间的放电. LCD阵列基板的数据线工作电压范围为0—20 V, 属于低压范围. 综合考虑放电能力及版图空间, 一般选择Diode型保护架构作为Cu互连周边ESD保护器件. 根据VL的电压值设计ESD保护电路的TFT器件开态阻抗, 即设计器件沟道的宽长比W/L. 在(1)式中, 电子迁移率μ, 单位介质电容Cox, 器件电压Vgs, Vth和Vds是已知参数, I在IL—IH中间取值, 一般取值不大于10–4 A, 可求出W/L比值.

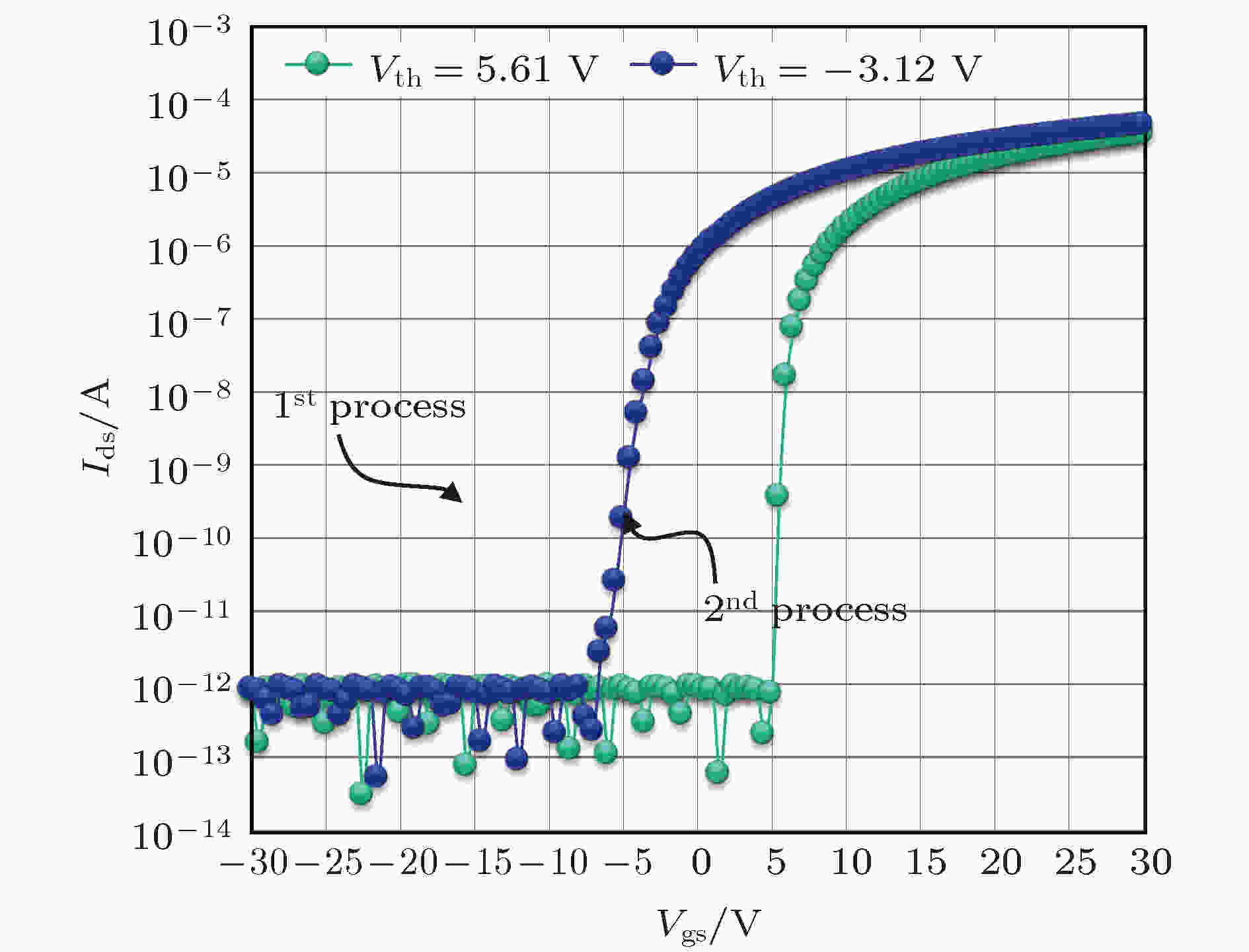

图 8 不同生产工艺下的IGZO TFT的Ids-Vgs曲线

图 8 不同生产工艺下的IGZO TFT的Ids-Vgs曲线Figure8. Ids-Vgs curves of IGZO TFT devices with different production technologies.

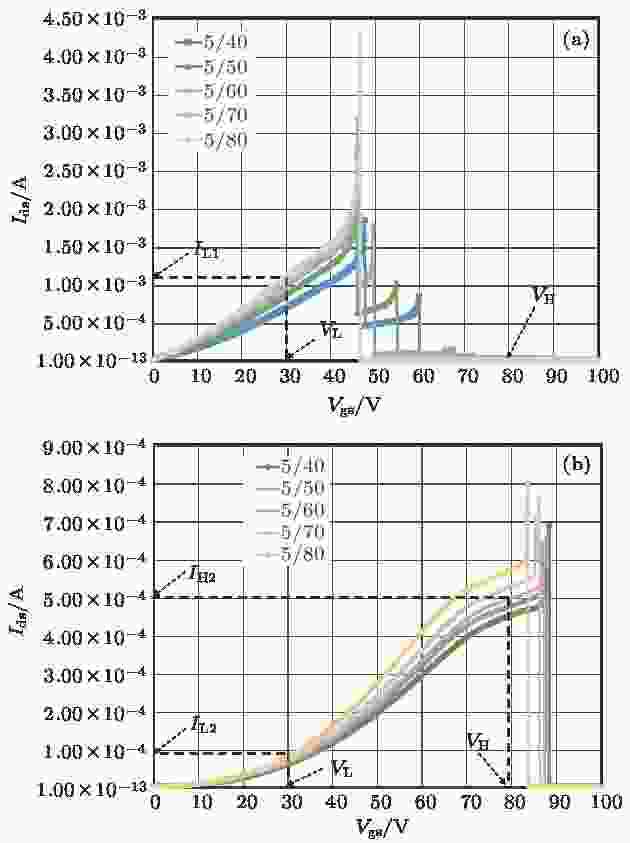

在两种不同的生产工艺中, 使用同样的Diode型ESD保护电路器件, 其电压扫描结果如图9所示. 根据数据线工作电压和栅极绝缘层的耐压值, 设置VL和VH的观察值分别为30 V和80 V. 在第一种生产工艺中, 由于Vth偏小, 沟道导电性能较强, IL1电流小于10–3 A, Cu互连之间会出现信号干扰问题, 面板无法正常显示. 在VH位置, Diode型保护电路器件因为电流过大, 出现烧毁无法保护层间栅绝缘层的击穿. 在第二种生产工艺中, 沟道导电性恢复至合理水平, IL2 ≤ 10–4 A. 此时, 可以忽略数据线Cu互连之间因为Diode型保护电路器件的漏电流干扰, 面板可以正常显示. IH2 ≥ 10–4 A, 可以保证静电电荷在积累到栅绝缘层的击穿电压前被释放掉, 层间Cu互连的ESD保护效果较好.

图 9 不同生产工艺条件下的Diode型ESD电压扫描结果 (a) 第一种生产工艺条件; (b) 第二种生产工艺条件

图 9 不同生产工艺条件下的Diode型ESD电压扫描结果 (a) 第一种生产工艺条件; (b) 第二种生产工艺条件Figure9. Voltage scanning results of Diode ESD protection circuit under different production technologies: (a) The first production process conditions; (b) the second production process conditions.

图 10 数据线之间的Diode型ESD保护电路 (a) 版图; (b) 原理图

图 10 数据线之间的Diode型ESD保护电路 (a) 版图; (b) 原理图Figure10. Diode-type ESD protection circuit between data lines: (a) Layout; (b) schematic diagram.

本文提出的ESD保护电路设计思想, 有效提高了IGZO TFT背板的层间Cu互连抗ESD破坏的效果. 采用传统a-Si TFT背板的周边ESD保护电路, 因为ESD破坏导致的数据线和扫描线层间Cu互连短路不良率较高. 数据线和扫描线之间发生ESD, 会导致栅绝缘层被击穿, 上下两层金属线发生导通, 形成十字交叉线显示不良. 通过测量特定IGZO TFT工艺的层间Cu互连耐压水平, 进行周边ESD保护电路的匹配设计, 层间Cu互连短路不良基本消除.

感谢工业和信息化部第五研究所电子元器件可靠性物理及其应用技术重点实验室在Cu互连电流密度仿真上给予的帮助.