全文HTML

--> --> -->早期半导体量子点量子计算研究主要集中在III/V族材料体系, 包括GaAs量子点[7-9]、InAs纳米线[10]以及InSb纳米线[11]. 该体系主要利用电子自旋进行比特编码, 目前已经实现了电子自旋的操控[7]和读出[12]. 实现量子计算机的一个重要前提是要求量子比特具有长的量子退相干时间, 但是III/V族材料存在核自旋引起的超精细相互作用, 例如GaAs/AlGaAs异质结栅控量子点中每个电子会受到约106个核自旋的影响[7], 导致退相干时间较短. 目前GaAs/AlGaAs异质结栅控量子点的退相干时间约为60 ns, InAs和InSb纳米线量子点的退相干时间仅为10 ns, 这就极大地限制了III/V族材料在半导体量子点量子计算领域的应用.

得益于IV族Si, Ge材料与成熟硅工艺兼容且可以通过同位素纯化获得无核自旋的28Si和72Ge, 近年来IV族材料量子点量子计算的研究得到了迅速发展. IV族材料体系主要包括 Si 金属氧化物半导体(MOS)[13]、Si/SiGe异质结[14]、Si纳米线[15,16]、单原子掺杂的Si材料[17]、Ge/SiGe异质结[18]以及Ge量子线[19,20]等. 在Si材料中主要利用电子的自旋进行比特的编码, 目前已经实现了单比特[21,22]、两比特[23]和三比特Greenberger-Horne-Zeilinger态[24]的操控以及两比特之间的远距离通信[25]. 基于Si/SiGe异质结[26]和天然Si MOS量子点[27]的电子自旋量子比特退相干时间达到了约2 μs. 使用了同位素纯化28Si材料(29Si含量小于800 × 10–6)的量子比特, 由于大幅降低了核自旋的影响, 其退相干时间可达到120 μs[28]. 此外, 2020年, 来自新南威尔士大学的Dzurak小组[29]和代尔夫特理工大学的Veldhorst小组[30]几乎同时在28Si中实现了能在大于1 K温度下运行的“高温”量子比特, 克服了实现通用量子计算机最困难的障碍之一. 基于单原子掺杂的Si材料制备的量子比特主要利用核自旋进行比特编码, 由于其在退相干时间以及可扩展性等方面存在巨大优势而被广泛关注[31-33], 例如在P掺杂的同位素28Si材料中, P原子核自旋的退相干时间可超过30 s[34], 其单比特门操控保真度可达到99.99%[35], 也在P掺杂的自然Si材料中实现了两比特交换门, 其单电子自旋读出保真度可达到94%[36]. 在Ge材料中主要利用空穴自旋进行比特的编码, 目前在Ge量子线中实现了空穴量子比特[20], 其退相干时间约为130 ns; 也实现了拉比频率高达540 MHz的超快操控速度量子比特[37]. 在Ge/SiGe异质结空穴气中实现了两比特逻辑门[38]和四比特量子处理器[18].

半导体量子点量子计算的快速发展得益于材料制备技术的不断发展. 近年的重要进展包括二维Ge/SiGe平面异质结迁移率达到106 cm2/(V·s)[39,40], 一维Ge/Si量子线新生长模式的发现[41]以及晶圆级可控生长[42]等. 本文将分别详细介绍Si和Ge量子计算材料的研究进展. 其中, Si材料主要介绍Si纳米线、Si/SiGe异质结, Ge材料主要介绍Ge/SiGe异质结、Si/Ge核/壳纳米线以及Ge棚屋型量子线.

2.1.Si纳米线

一维Si纳米线主要通过自上而下的纳米加工技术和自下而上的化学气相沉积(CVD)方法生长. 纳米加工技术一般是通过刻蚀绝缘体上硅(SOI)衬底上的Si薄膜(薄膜厚度小于50 nm)得到一维Si纳米线[43], 可以利用多晶硅作为栅电极在纳米线方向形成势垒, 可在Si纳米线中形成单量子点, 观测到库仑振荡现象[16,44,45], 也可以在Si纳米线中形成双量子点结构, 观察到泡利自旋阻塞现象[46]. CVD法主要利用气-液-固生长机制(其原理在后文有详细描述), 可制备直径为6—20 nm且长度为1—30 μm的Si纳米线[47], 也可对纳米线进行n型和p型掺杂, 例如Lieber研究小组[15]就制备出了轴向调制掺杂的Si纳米线, 在1.5 K下观察到了单电子隧穿效应.2

2.2.Si/SiGe异质结

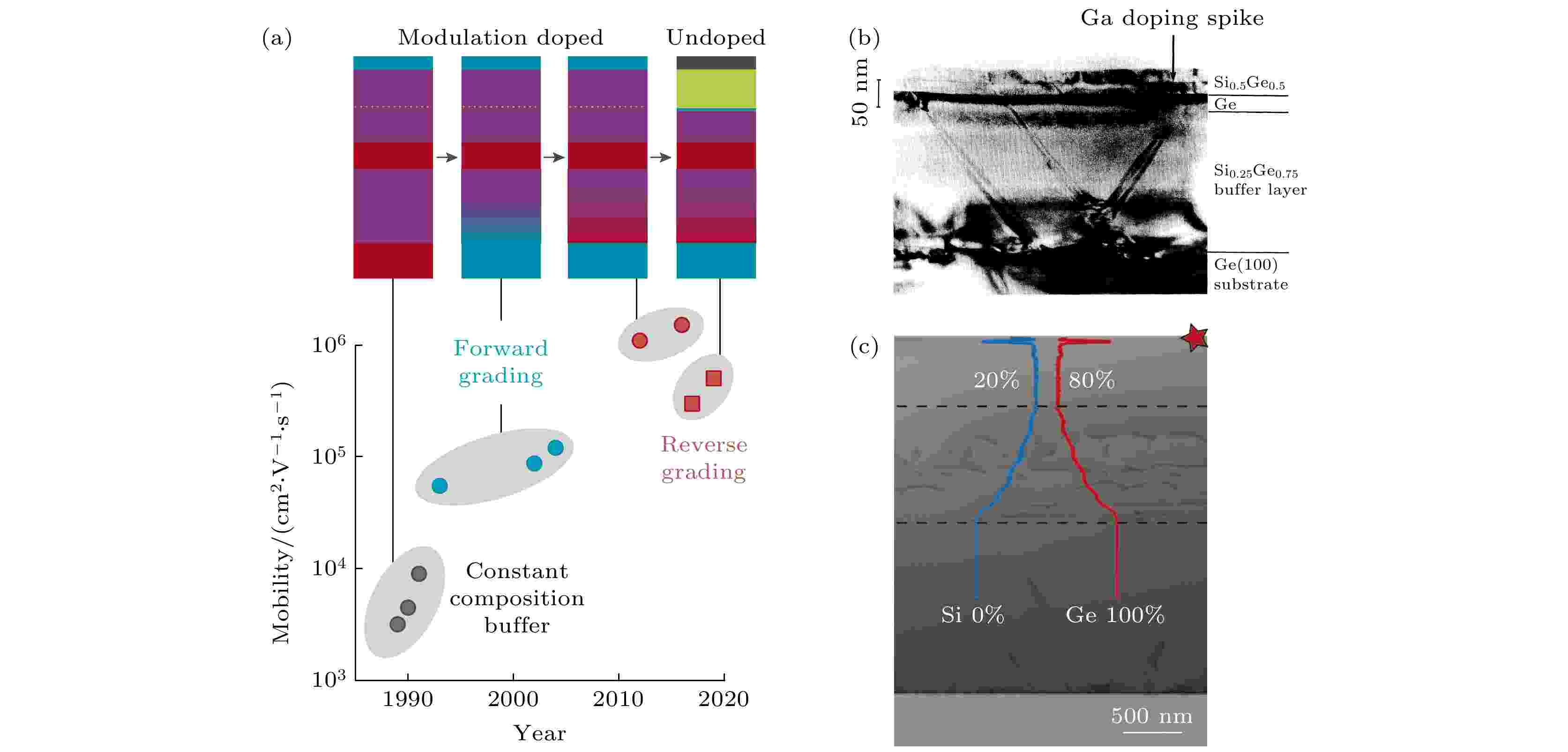

二维电子气的实现主要有Si MOS和Si/SiGe 两种结构. 通常实验上通过测量低温霍尔迁移率来判断二维电子气质量的优劣. 影响迁移率高低的材料界面质量、均匀性, 以及内部背景杂质和缺陷等因素对量子点器件的性能会造成影响. 一般而言, 相同结构情况下更高的迁移率表明载流子受到的散射少, 二维电子气系统更“纯净”, 量子点受到的背景噪音少; 均匀性高更有助于后续的量子点器件集成. 对于Si MOS 结构, 通过高温热氧化的方式在Si (001)表面形成高质量的SiO2层, 在界面区域限制电子形成二维电子气. 目前该结构的电子迁移率可达到1 × 104—4 × 104 cm2/(V·s)[48,49].Si/SiGe异质结材料研究方面, 根据掺杂与否, 分为掺杂型Si/SiGe异质结和非掺杂型Si/SiGe异质结. 随着对Si/SiGe异质结材料研究的深入, 考虑载流子散射因素, 研究工作经历了多个阶段(图1(a)), 早期的设计从固定SiGe薄膜中Ge含量的方式到组分缓渐变的生长方法来优化SiGe缓冲层的质量, Fitzgerald研究小组和Schaffler等同一时期通过分子束外延技术获得的薄膜峰值迁移率达到1.7 × 105 cm2/(V·s)[50,51]; 通过优化应变硅层厚度和Si/SiGe界面来降低位错和界面粗糙度对电子的散射, 峰值迁移率达到8×105 cm2/(V·s)[52]; 此后, 通过移除掺杂层、优化间隔层厚度和采用SiO取代Al2O3降低远端电荷散射, 二维电子气低温迁移率达到了2.4 × 106 cm2/(V·s)[53]. 下面详细介绍基于Si/SiGe异质结的二维电子气的研究进展.

图 1 (a) Si/SiGe异质结二维电子气低温霍尔峰值迁移率的发展, 其中实心圆圈和实心方块分别代表掺杂型结构和非掺杂型结构; 黑色、红色和蓝色分别代表SiGe缓冲层固定锗含量、Si/SiGe超晶格和组分渐变等3种不同生长方法; 插图是SiGe/Si/SiGe 异质结结构和能带结构对准示意图; (b)穿透位错密度对电子迁移率的影响[64]; (c)应变硅层厚度对电子低温峰值迁移率的影响[64]; (d) SiGe间隔层厚度对电子迁移率的影响[68]

图 1 (a) Si/SiGe异质结二维电子气低温霍尔峰值迁移率的发展, 其中实心圆圈和实心方块分别代表掺杂型结构和非掺杂型结构; 黑色、红色和蓝色分别代表SiGe缓冲层固定锗含量、Si/SiGe超晶格和组分渐变等3种不同生长方法; 插图是SiGe/Si/SiGe 异质结结构和能带结构对准示意图; (b)穿透位错密度对电子迁移率的影响[64]; (c)应变硅层厚度对电子低温峰值迁移率的影响[64]; (d) SiGe间隔层厚度对电子迁移率的影响[68]Figure1. (a) Mobility of Si two-dimensional electron gas with time. Solid squares and circles refer to undoped structure and doped structure, respectively. The black, red and blue color refer to three different growth methods (constant Ge composition, Si/SiGe superlattice and the graded Ge composition). Inset images show the SiGe/Si/SiGe heterostructures and the schematic band-edge profile. (b) Effect of threading dislocations on electron mobility[64]. (c) Effect of Si-channel thickness on electron mobility[64]. (d) Effect of the spacer layer thickness on electron mobility[68].

1985年Abstreiter等[54]首先利用分子束外延技术基于掺杂型Si/SiGe异质结实现了II型能带配置, Si处于张应变, 在此硅量子阱中限制电子形成二维电子气. 基于Shubnikov-de Hass振荡和回旋共振实验证明应变硅中六重简并的导带底分裂成垂直表面的两重简并态Δ2和平行表面的四重简并态Δ4, 增大应变会增强Δ2和Δ4的分裂. Δ2能谷平行于表面方向, 电子有效质量为

为了提高SiGe缓冲层质量, 后续不同研究组提出了两种方法. IBM实验室利用超高真空化学气相沉积(UHV-CVD)生长技术外延生长Si/SiGe超晶格的方案[57,58], 将穿透位错密度降低到107 cm–2, 二维电子气低温迁移率提高到8.5 × 104 cm2/(V·s)[58]. 另一种方法是锗组分渐变的方法. AT&T贝尔实验室采用分子束外延生长厚的锗组分渐变层[59,60], 逐渐增加Ge的含量到0.3, 电子束感应电流表征结果显示Si0.7Ge0.3缓冲层穿透位错密度降低到106 cm–2, 4.2 K时二维电子气迁移率提升到0.96 × 105—1.26 × 105 cm2/(V·s). 经过生长条件的进一步优化, Ge组分渐变速率不大于每微米10%, Fitzgerald研究小组和Schaffler等同时通过分子束外延技术将二维电子气迁移率的记录提升到约1.7 × 105 cm2/(V·s)[50,51]. 采用Ge组分渐变方法得到的二维电子气迁移率之所以更高, 主要得益于高质量的SiGe缓冲层可以有效降低穿透位错密度. 此外, 实验显示生长过程中采用高温且组分缓渐变的方法, 能增大已经产生的失配位错滑移速率以释放晶体内部积累的应变能, 同时可以避免因渐变过快而产生新的失配位错[61].

1994年, Ismail等[62]优化应变硅量子阱的厚度, 避免在量子阱层产生新的失配位错, 同时减少缓冲层穿透位错在量子阱层的滑移, 防止在Si/SiGe缓冲层的界面形成失配位错的排列, 将掺杂型Si/SiGe异质结二维电子气的迁移率记录提高到4 × 105 cm2/(V·s), 背栅结构器件在0.4 K时的迁移率达到5.3 × 105 cm2/(V·s). 同年, Ismail等[63]将顶栅结构器件记录提高至5.2 × 105 cm2/(V·s). 1996年, Ismail[64]总结了穿透位错和量子阱厚度对迁移率的影响, 见图1(b)和图1(c), 表明了厚的渐变层对于获得低穿透位错密度的缓冲层和合适量子阱厚度的重要性. 1998年, 日本的Sugii等[52]采用固相外延的方式实现了二维电子气峰值迁移率在15 K时达到8 × 105 cm2/(V·s), 高分辨透射电子显微镜表征显示样品具有非常陡峭的Si/SiGe界面.

2005年Lai等[65]的研究结果显示原子层沉积生长的Al2O3作为二维电子气材料的介电层, 可有效减少器件中的低频电荷噪声[43], 通过变化栅偏压可有效调控二维电子气浓度. 2009年, Lu等[66]对非掺杂型结构进行优化, 利用超高真空化学气相沉积, 通过Ge组分缓渐变的方式生长Si0.8Ge0.2的渐变层后生长1 μm的固定Ge组分的恒量层, 得到高质量的Si0.8Ge0.2薄膜, 然后生长15 nm 硅量子阱, 65 nm 硅锗间隔层和1 nm 硅盖层. 在载流子浓度为2.5 × 1010 cm–2时, 0.3 K下二维电子气迁移率达到1.6 × 106 cm2/(V·s). 2012年, Tsui研究小组[67]通过降低SiGe缓冲层中锗的含量到0.14, 在间隔层达到526 nm时, 0.3 K下二维电子气迁移率峰值达到2 × 106 cm2/(V·s). 2015年, Laroche等[68]比较了不同间隔层厚度对电子气迁移率的影响, 分析了不同结构的散射机制(图1(d)), 结果表明可获得的最低载流子浓度随着间隔层厚度的减少而增大, 且比较适合纳米器件的间隔层厚度为25—50 nm, 可避免“remote scattering”的影响. 2015年, 俄罗斯研究小组Melnikov等[53]利用热蒸发的SiO取代原子层沉积生长的Al2O3, 获得了质量更好的氧化物/半导体界面, 将二维电子气低温迁移率提高到目前最高值2.4 × 106 cm2/(V·s). 为研究背景杂质散射, 2015年, Petta研究小组[69]比较了26种不同结构的Si/SiGe异质结, 利用二次离子质谱测定结构中的氧含量, 发现背景氧含量和峰值迁移率之间呈现强的相关性. 表明在Si/SiGe生长过程中, 背景中可能引入的杂质是影响迁移率的关键. 值得注意的是, 虽然二维电子气迁移率达到百万量级, 实际上的百万量级的霍尔器件结构中, 锗的含量低于0.2, 同时间隔层厚度大于60 nm, 不利于表面栅极对电子气的调控. 常见的半导体量子点量子比特器件所用的锗含量一般为0.25—0.3, 间隔层厚度一般在30—50 nm.

对于Si/SiGe材料体系, 界面粗糙度不仅影响材料的迁移率, 界面存在的高密度原子台阶还会影响谷-轨道耦合, 抑制谷劈裂[70-72]. 早期从Hall bar 器件中提取的谷劈裂能量为μeV量级[73-76], 器件尺寸缩小至QPCs (quantum point contacts)[77]和量子点器件[78-80]时, 谷劈裂能量可达到1 meV 量级. 对于自旋量子比特, 需要大的谷劈裂能, 可在高磁场下调控量子点器件. 材料上需要采用无斜切的衬底, 避免高密度的原子台阶产生, 甚至预期制备无原子台阶的Si/SiGe界面.

量子点量子比特性质的提高不仅取决于材料结构的优化, 还有材料自身的影响. 在前期研究基础上, 将自然的Si材料替换成同位素提纯的28Si材料, 降低核自旋对电子自旋的噪音, 可以大幅提高比特退相干时间. 2014年和2015年, Veldhorst 等[23,28]基于28Si MOS 结构, 利用电子自旋共振操控实现量子比特退相干时间达到120 μs, 相干时间达到28 ms. 普通的Si MOS 结构中退相干时间的最高记录值为2020年基于电偶极自旋共振操控实现的18.1 μs[81]. 2018年, 日本Tarucha研究小组[21]基于28Si/SiGe异质结量子点, 使电子自旋比特退相干时间达到了20 μs, 保真度超过99.9%. 2020年, 德国Struck 等[82]同样基于28Si/SiGe异质结材料, 使电子自旋比特退相干时间达到了21 μs. 普通的Si/SiGe异质结材料中电子自旋比特退相干时间最高记录值是2016年Tarucha 课题组[27]实现的1.8 μs. 截止到目前, 对于Si MOS结构和Si/SiGe两种结构, 基于同位素提纯材料的器件相对未提纯材料的器件均提高了量子比特的退相干时间记录值[83].

此外, Ge材料在量子计算领域也因其独特的优势而倍受关注[84]. 一方面, Ge具有高的空穴迁移率和小的有效质量[85], 为实现高质量的量子点提供了基础. 另一方面, 它具有大的g因子以及强的自旋-轨道耦合相互作用[86,87], 且g因子可调[88], 可以对自旋进行快速的全电学操控. 而且, Ge材料利用空穴自旋进行比特的编码, 与电子相比, 空穴的p轨道与原子核的轨道交叠较小[89], 由核自旋引起的超精细相互作用低, 也可以实现无核自旋的同位素纯化的72Ge, 使得Ge空穴自旋量子比特可以具有长的退相干时间. 在器件制备方面, Ge能够与当前的Si工艺兼容; 并且几乎所有的金属在与Ge接触时, 都能够使费米能级钉扎在价带处附近, 因此都能够与Ge形成良好的欧姆接触[90]; 同时, 在Ge上也能够生长高质量且具有高介电常数的介电层, 有利于高性能器件制备及集成. 基于以上诸多优点, Ge成为了实现半导体量子点量子计算的理想材料. 近年来, 从二维的Ge/SiGe异质结薄膜到一维的Ge纳米线制备技术都在不断发展, 并取得了一系列重要突破.

2

3.1.Ge/SiGe异质结

Ge/SiGe异质结中, 压应变的锗和弛豫的硅锗层, 形成I型能带, Ge量子阱中限制了空穴, 应变使价带顶轻重空穴发生分裂, 导致空穴有效质量减少, 增强了Ge中空穴的迁移率. 如图2(a)所示, Ge/SiGe异质结材料的发展主要经历了4个阶段[84]. 前3个阶段主要是研究掺杂型结构, 后续研究集中在非掺杂型结构. Ge/SiGe异质结所用SiGe缓冲层经历了锗衬底上固定Ge含量的生长方法, Si衬底上Ge组分缓渐变增大和Si衬底上先生长Ge薄膜再通过Ge组分减少的逆组分渐变方法3个阶段. 图 2 (a)不同时期的Ge/SiGe异质结二维空穴气低温霍尔峰值迁移率, 其中实心圆圈和实心方块分别代表掺杂型结构和非掺杂型结构; 黑色、蓝色和红色分别代表SiGe缓冲层固定锗含量、组分正渐变和组分逆渐变等3种不同生长方法[84]; (b) Ge衬底上固定锗组分生长SiGe缓冲层的截面TEM, 可看到在缓冲层及量子阱层产生大量堆垛层错[92]; (c) Si衬底上锗组分逆渐变方法生长的Ge/SiGe空穴气结构的截面TEM图[102], 位错主要分布在逆渐变缓冲层

图 2 (a)不同时期的Ge/SiGe异质结二维空穴气低温霍尔峰值迁移率, 其中实心圆圈和实心方块分别代表掺杂型结构和非掺杂型结构; 黑色、蓝色和红色分别代表SiGe缓冲层固定锗含量、组分正渐变和组分逆渐变等3种不同生长方法[84]; (b) Ge衬底上固定锗组分生长SiGe缓冲层的截面TEM, 可看到在缓冲层及量子阱层产生大量堆垛层错[92]; (c) Si衬底上锗组分逆渐变方法生长的Ge/SiGe空穴气结构的截面TEM图[102], 位错主要分布在逆渐变缓冲层Figure2. (a) Improvement of two-dimensional hole gas low temperature Hall mobility of Ge/SiGe heterostructure with time. Solid squares and circles refer to undoped structure and doped structure. The black, blue and red color refer to three different growth methods (the constant Ge composition, forward grading and the reverse grading) [84]. (b) Cross-sectional TEM of SiGe buffer layer with constant Ge composition on Ge substrate, plenty of stacking faults inside the constant Ge composition buffer layer and Ge quantum well[92]. (c) Cross-sectional TEM of two-dimensional hole gas obtained by reverse grading method[102]. Dislocations are mainly localized inside the reverse grading buffer layer.

1988年, Wagner和Janocko[91]利用分子束外延技术在Ge衬底上生长固定Ge组分的Si0.5Ge0.5缓冲层, 再构造掺杂型的Si0.5Ge0.5/Ge异质结形成二维空穴气, 4.2 K时空穴迁移率为3200 cm2/(V·s). 1990年, Murakami 等[92]同样基于分子束外延在Ge衬底上生长200—500 nm固定Ge含量的Si0.25Ge0.75缓冲层, 然后外延Ge/Si0.25Ge0.75异质结, 77 K时, 二维空穴气迁移率达到4500 cm2/(V·s). 1991年, Murakami 等[93]基于相同结构, 将二维空穴气低温迁移率优化到9000 cm2/(V·s). 然而, 该时期基于Ge衬底上固定Ge含量的生长方法获得的SiGe缓冲层存在大量缺陷, 如图2(b) 所示, 截面透射电子显微镜(TEM)表征可以看到明显堆垛层错面缺陷的存在[92]. 缓冲层中大量的缺陷贯穿到Ge量子阱中, 使得基于该生长方法实现的二维空穴气迁移率没有突破104 cm2/(V·s)量级.

为了提高SiGe缓冲层的质量, 各研究小组采用在Si衬底上组分渐变的方法生长高Ge含量的SiGe缓冲层. 贝尔实验室Xie等[94]利用分子束外延在Si衬底上渐变生长外延弛豫的Si0.4Ge0.6薄膜, 基于该薄膜生长调制掺杂的Ge空穴气结构, 4.2 K时迁移率可以达到5.5 × 104 cm2/(V·s). 2002年, 意大利von Kanel研究小组[95]利用等离子体增强化学气相沉积按照10%/μm的渐变速率生长7 μm的渐变层和1 μm的Si0.3Ge0.7薄膜, 利用腐蚀坑密度的方法评估该薄膜的穿透位错密度约为2 × 106 cm–2. 基于此弛豫的SiGe缓冲层得到的二维空穴气在4.2 K时迁移率达到了8.7 × 104 cm2/(V·s). 2004年, von Kanel课题组[96]进一步降低缓冲层渐变速率至7%/μm, 得到的二维空穴气在2 K时迁移率达到1.2 × 105 cm2/(V·s).

2008年, 英国Shah 等[97]提出了逆组分渐变的方法生长高质量的SiGe缓冲层. 利用减压化学气相沉积(RPCVD)生长技术, 首先通过低温加高温两步法在Si上外延生长穿透位错密度低于5 × 107 cm–2的Ge薄膜, 然后逐渐减少Ge的含量到0.8, 最后生长固定Ge含量的Si0.2Ge0.8层. 化学刻蚀法表明该薄膜穿透位错密度为106 cm–2, 表面均方根粗糙度为2.6 nm, 最优值为1.9 nm, 优于正渐变方法得到的SiGe薄膜表面粗糙度[98]. 基于该类型的SiGe缓冲层, 2012年, 该小组制备的调制掺杂型二维空穴气迁移率在12 K达到1.1 × 106 cm2/(V·s) [39], 2016年, 他们进一步将调制掺杂型二维空穴气迁移率提高到1.5 × 106 cm2/(V·s) [40].

随着对应变Ge量子阱中空穴量子比特研究的深入, 实验发现掺杂型结构虽然可以达到百万级别的迁移率, 但是掺杂层容易导致漏电流、寄生通道和电荷噪声[14,99,100], 因此, 后期对空穴量子比特的研究主要集中在非掺杂型结构上. 2016年, 中国台湾Laroche 等[101]利用快速热化学气相沉积采用逆组分渐变法生长的非掺杂型应变Ge量子阱结构, 在空穴浓度为1011 cm–2量级时, 峰值迁移率达到3 × 105 cm2/(V·s). 2019年, Sammak等[102]基于组分逆渐变法生长SiGe缓冲层, 利用RPCVD生长的非掺杂型应变锗量子阱结构, 二维空穴迁移率达到了5 × 105 cm2/(V·s), 空穴浓度为1.2 × 1011 cm–2. 在空穴浓度比较低时, 迁移率得到提高的原因主要在于SiGe缓冲层质量的优化. 如图2(c)所示, Si和Ge之间的失配位错主要分布在Ge/Si界面区域, 后续渐变的生长方法使得产生的失配位错在渐变层中滑移, 释放了晶体内部积累的应变能, 同时滑移过程增加了失配位错相互作用并湮灭的概率, 最终提高了SiGe缓冲层的质量[102]. 对于Ge/SiGe异质结二维空穴气, 目前还没有同位素纯化材料的相关报道.

2

3.2.Ge纳米线

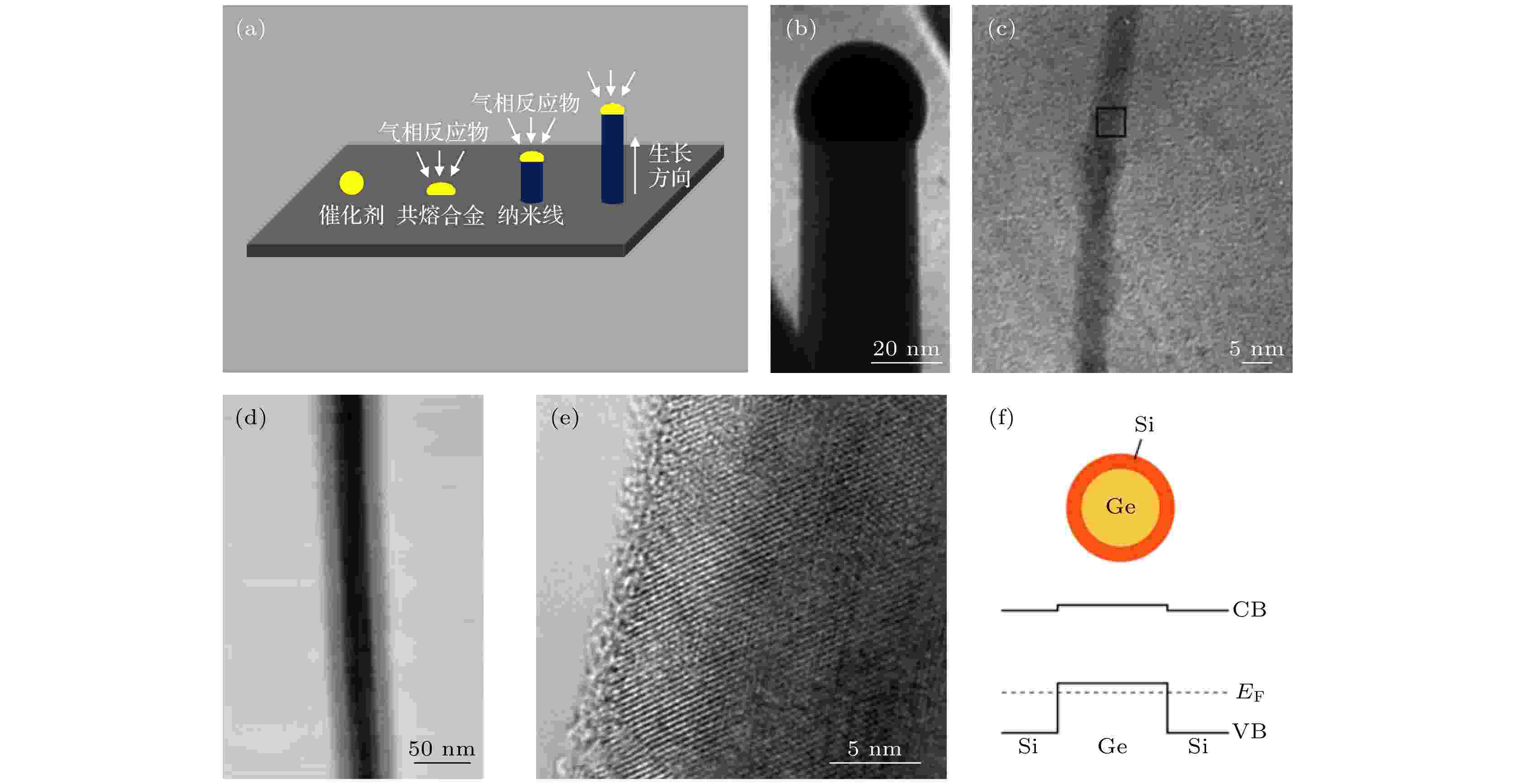

一维Ge纳米线的制备技术近年来迅速发展, 已经实现了从非面内生长的Ge/Si核/壳纳米线到Si衬底上面内无需催化剂生长的棚屋型Ge量子线, 最后到Si衬底上面内可定位生长的棚屋型Ge量子线的可控制备.Ge/Si核/壳纳米线主要利用气-液-固(VLS)生长机制[103], 采用CVD法制备, 图3(a)为其生长过程示意图, 这种方法是利用金属颗粒作为催化剂, 通入气相反应物, 在一定温度下气相反应物与金属颗粒形成共熔合金, 当共熔合金处于过饱和状态时, 会析出晶体形成纳米线. 纳米线的横截面为圆形, 与衬底成一定角度的方向生长, 金属颗粒一直处于纳米线的顶端且会逐渐减小[104], 其透射电子显微镜(TEM)图如图3(b)所示. 由于金属颗粒的直径决定了纳米线的直径, 而最初金属颗粒受到制备工艺的限制, 直径一般在100 nm以上. 1998年, Morales 和Lieber[47]采用激光烧蚀技术降低了金属颗粒的直径, 实现了直径最小达5 nm的Ge纳米线的制备, 如图3(c)所示. 2002年, Lieber研究小组[105]又基于上述生长方法实现了Ge/Si核/壳纳米线的制备. 如图3(d)所示, Ge核的直径为26 nm, 通过图3(e)的高分辨TEM图可知, Si壳和Ge核全部为单晶结构, 其横截面示意图以及能级结构如图3(f)所示, Si壳和Ge核的价带能级差为0.5 eV, Ge空穴气被限制在Ge核内, 空穴迁移率约为1000 cm2/(V·s)[19]. 理论和实验研究表明, Ge/Si核/壳纳米线具有可调节的强自旋-轨道耦合相互作用[86,106], 朗德g因子约为2[107], 基于Ge/Si核/壳纳米线制备的双量子点器件也表现出良好的特性, 实现了电场对两个量子点隧穿耦合强度的调控[108], 自旋弛豫时间可达0.6 ms[109], 退相干时间可达180 ns[110].

图 3 (a) VLS方法生长纳米线的示意图; (b) VLS方法生长的Ge纳米线的TEM图[104]; (c)结合激光烧蚀技术和VLS生长方法制备的直径为(5 ± 0.6) nm的Ge纳米线的TEM图[47]; (d) Ge/Si核/壳纳米线的TEM图, 其中黑色部分为Ge核, 浅灰色部分为Si壳[105]; (e) Ge/Si核/壳纳米线的高分辨TEM图, 表明Si壳为单晶结构[105]; (f) Ge/Si核/壳纳米线的横截面示意图以及能带偏移示意图[19]

图 3 (a) VLS方法生长纳米线的示意图; (b) VLS方法生长的Ge纳米线的TEM图[104]; (c)结合激光烧蚀技术和VLS生长方法制备的直径为(5 ± 0.6) nm的Ge纳米线的TEM图[47]; (d) Ge/Si核/壳纳米线的TEM图, 其中黑色部分为Ge核, 浅灰色部分为Si壳[105]; (e) Ge/Si核/壳纳米线的高分辨TEM图, 表明Si壳为单晶结构[105]; (f) Ge/Si核/壳纳米线的横截面示意图以及能带偏移示意图[19]Figure3. (a) Schematic diagram of nanowires grown by VLS method; (b) TEM image of Ge nanowire grown by VLS method[104]; (c) TEM image of Ge nanowires with diameter of (5 ± 0.6) nm prepared by laser ablation method and VLS method[47]; (d) TEM image of Ge/Si core/shell nanowire with black Ge core and light gray Si shell[105]; (e) high resolution TEM image of Ge/Si core/shell nanowire showing a crystalline Si shell[105]; (f) schematic diagram of cross-section image and energy band offset of Ge/Si core/shell nanowire[19].

虽然Ge/Si核/壳纳米线得到了广泛研究, 但是它仍存在着两个困难. 首先, 纳米线沿着非面内的方向生长, 需要将纳米线转移到Si或SOI等衬底上进行器件制备[111], 增加了器件加工的难度, 且很难大规模集成; 其次, VLS生长需采用金属颗粒作为催化剂, 纳米线中存在金属污染, 影响器件的电学性质[112]. 以上不利因素制约了Ge/Si核/壳纳米线在半导体量子计算领域的进一步发展.

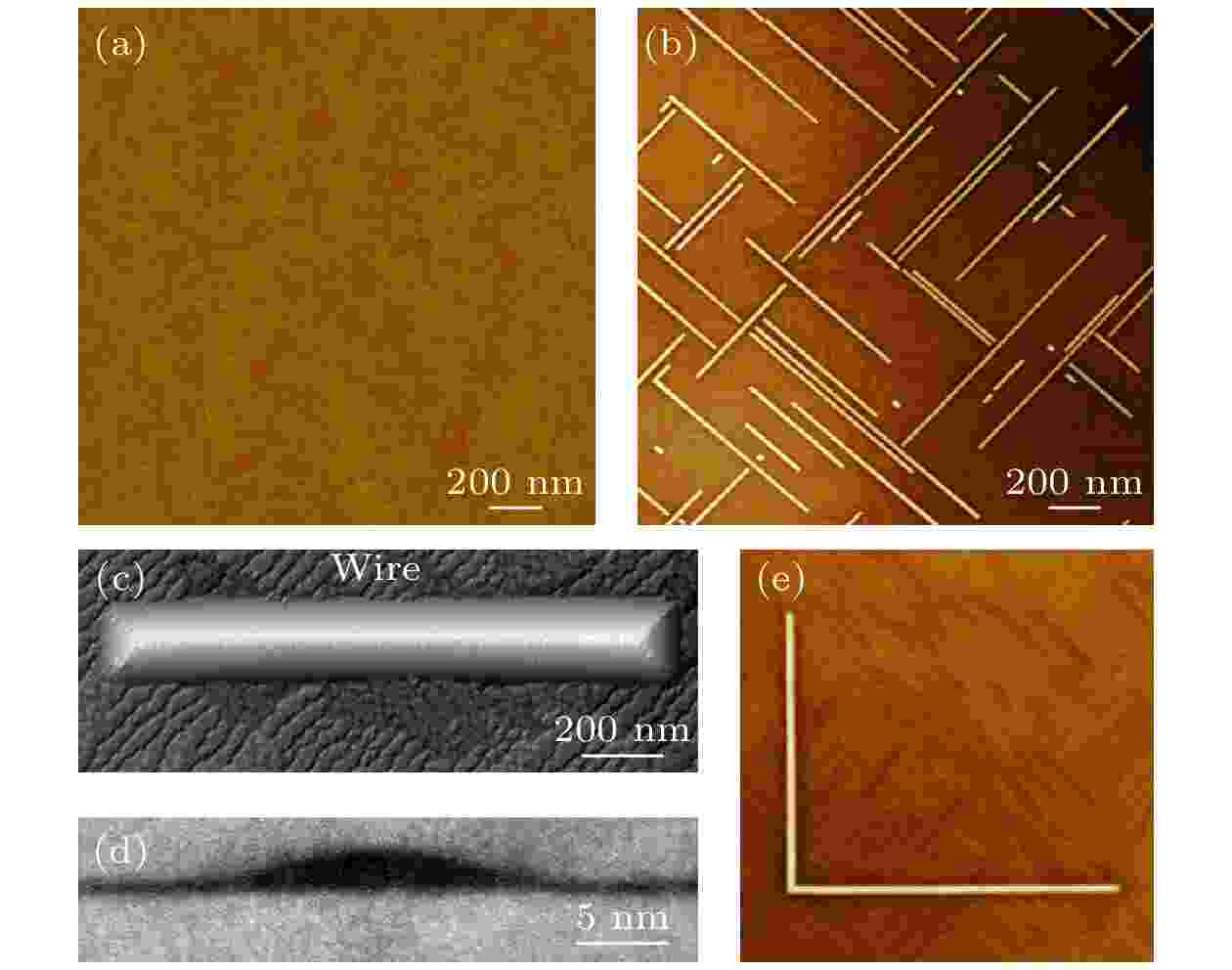

棚屋型Ge量子线是利用层状加岛状生长的Stranki-Krastanow生长模式[113], 采用分子束外延生长方法在Si衬底上获得的面内Ge量子线. 早在1990年, Mo等[114]就在Si(001)衬底上观察到了长度小于100 nm的棚屋型Ge岛, 而后Tersoff和Tromp[115]预测这种棚屋型Ge岛可能延长成为Ge量子线. 2012年, Zhang等[41]在Si(001)衬底上通过沉积纯Ge层以及退火的方法, 实现了长度可达2 μm的Ge量子线的外延生长. 他们采用分子束外延生长方法, 在570 ℃条件下以0.06 ?/s的速率沉积4.4个原子层厚度的Ge浸润层, 沉积厚度稍小于570 ℃时形成三维棚屋型Ge岛的临界厚度, 如图4(a)的原子力显微镜(AFM)图所示, 衬底表面没有形成任何三维结构. 然后将温度降低到560 ℃并原位退火, 获得如图4(b)所示的面内生长的自组装Ge量子线. Ge量子线的表面由4个{105}晶面组成, 取向沿平面内两个

图 4 (a) Si衬底上沉积4.4个Ge原子层后的表面AFM图; (b) Si衬底上沉积Ge层以及退火之后形成的Ge量子线的表面AFM图[41]; (c)和(d)分别是单根Ge量子线的扫描隧道显微镜图[116] 以及横截面TEM图[41]; (e) Si衬底上L形Ge量子线结构

图 4 (a) Si衬底上沉积4.4个Ge原子层后的表面AFM图; (b) Si衬底上沉积Ge层以及退火之后形成的Ge量子线的表面AFM图[41]; (c)和(d)分别是单根Ge量子线的扫描隧道显微镜图[116] 以及横截面TEM图[41]; (e) Si衬底上L形Ge量子线结构Figure4. (a) AFM image of Ge wetting layer after the growth of 4.4 monolayer Ge on Si substrate; (b) AFM image of Ge hut wire on Si substrate after the growth of Ge layer with subsequently annealing[41]; (c), (d) scanning tunneling microscope image[116] and cross-sectional TEM image of a Ge hut wire[41]; (e) L-shaped Ge hut wires on Si substrate.

Si(001)衬底上的棚屋型Ge量子线是无催化剂且面内生长的自组装量子线, 与Ge/Si核/壳纳米线相比, 避免了金属催化剂导致的金属污染以及纳米线的非面内生长导致的转移问题, 且纳米线直接生长在Si衬底上, 与当前的硅工艺兼容, 为后续器件制备带来了便利. 棚屋型Ge量子线的横截面为三角形, 与横截面为圆形的Ge/Si核/壳纳米线中轻重空穴混合不同, 棚屋型Ge量子线中的空穴几乎全部为重空穴[88], 轻空穴的含量小于1%, 而轻重空穴分离有助于退相干时间的延长[117]. 此外, 棚屋型Ge量子线具有大的g因子以及强的自旋-轨道耦合相互作用[87,118], 空穴的自旋-轨道耦合长度约为40—100 nm, 其g因子可达4.34, 且g因子依赖于外加磁场的方向, 具有很强的各向异性[88], 外加磁场垂直于量子线时的g因子与平行于量子线时的g因子比值可达18. 目前, 已经在棚屋型Ge量子线中实现了国际上首个Ge空穴量子比特[20], 退相干时间可达130 ns. 国内中国科学技术大学郭国平研究小组[118]在Ge量子线量子比特器件方面做了系统而深入的研究, 在这种Ge量子线上实现了双量子点的可控调节, 且在这种量子线中实现了单量子点以及双量子点与超导微波谐振腔的耦合[119,120], 能够采用超导微波谐振腔探测量子点中的空穴状态, 为实现远距离的量子点之间的通信以及进一步实现器件的集成和扩展奠定了重要基础. 郭国平研究小组[121]还首次在Ge空穴量子点中实现了g因子张量和自旋轨道耦合场方向的测量与调控, 对于硅锗体系更好地实现自旋量子比特的操控有重要的指导意义. 此外, 他们还实现了目前操控速度最快的量子比特, 其拉比振荡的频率约为540 MHz[37].

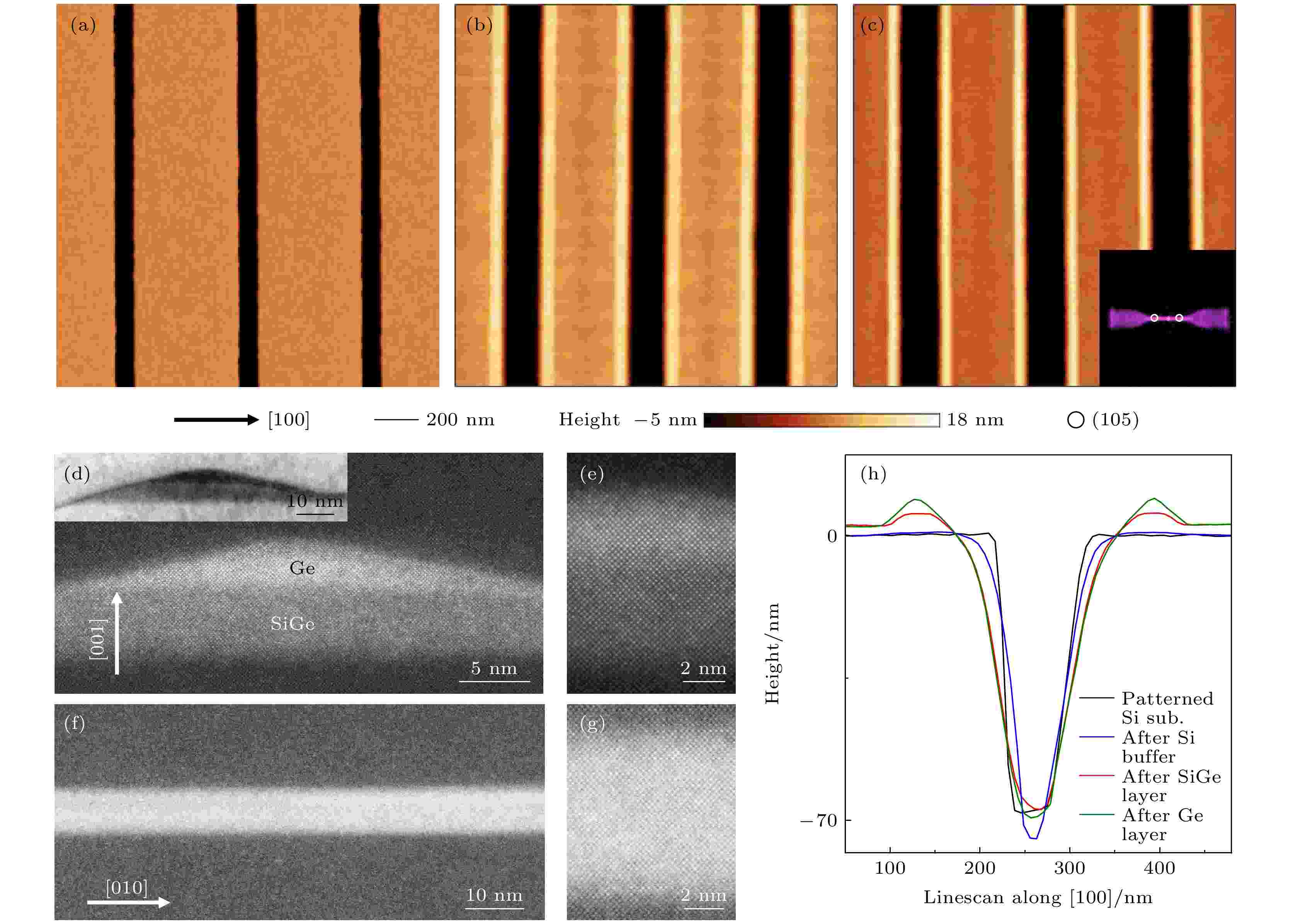

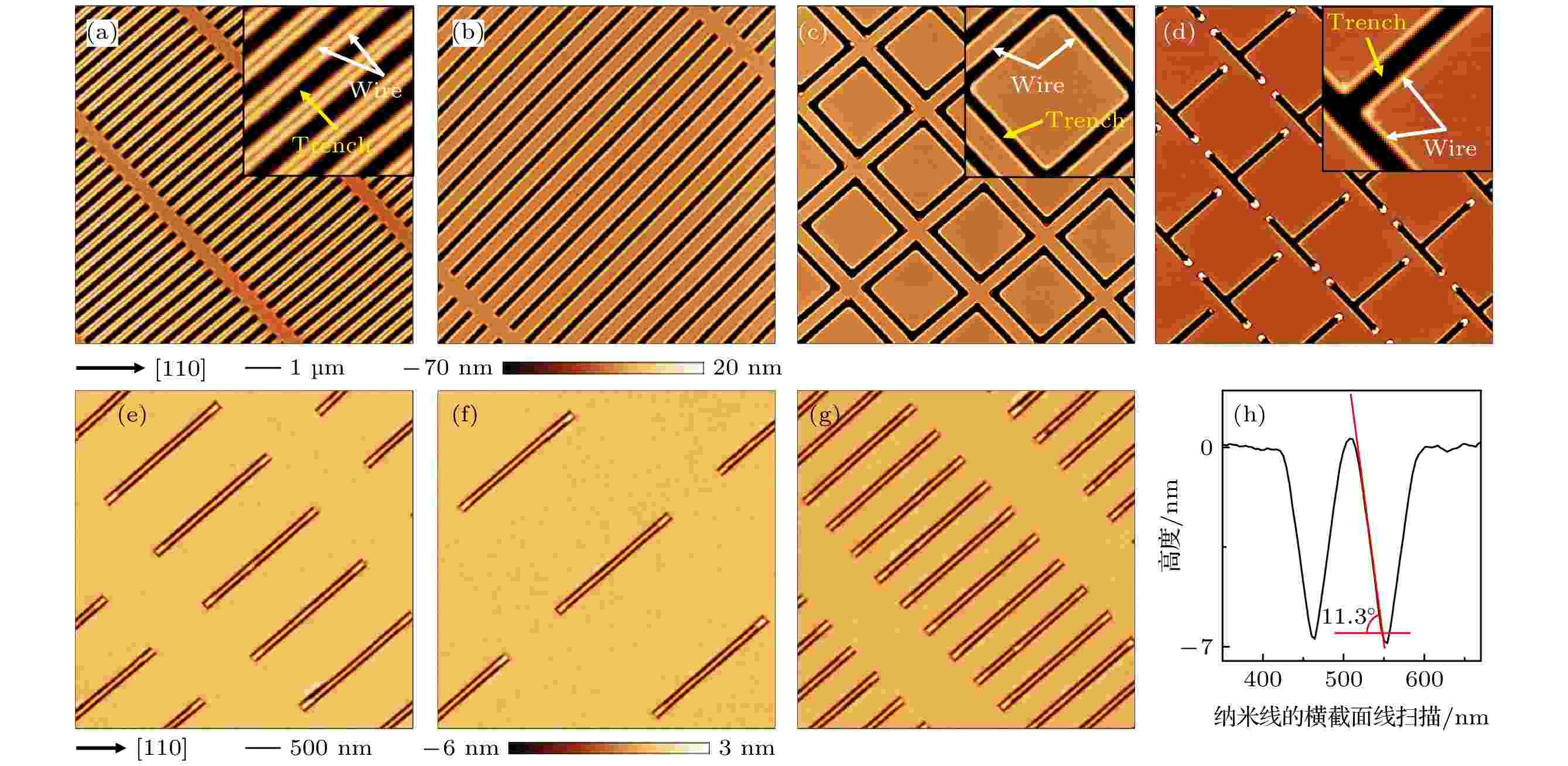

然而, 以上棚屋型Ge量子线位置在Si (001)表面上是随机分布的, 不利于量子器件的精确寻址和大规模集成. 结合微纳加工和分子束外延生长方法, Gao等[42]在Si (001)衬底上实现了棚屋型Ge量子线的面内精确定位生长. 该方法首先是利用电子束曝光和反应离子刻蚀技术在Si (001)衬底上刻蚀出周期性的凹槽图形结构, 凹槽的深度约为70 nm, 如图5(a)所示, 其中黑色部分为凹槽结构, 由于面内棚屋型Ge量子线沿

图 5 (a)具有凹槽结构的Si (001)图形衬底的表面AFM图[42]; (b)生长Si0.75Ge0.25层后形成一维SiGe条带结构的表面AFM图[42]; (c) SiGe条带上形成Ge量子线的表面AFM图, 插图为量子线的晶面分析图, Ge量子线的两个侧面均为{105}晶面[42]; (d)和(e)分别为Ge量子线的横截面STEM图及放大的STEM图[42], 插图为Ge量子线的横截面全貌图; (f)和(g)分别为Ge量子线沿线方向的高分辨STEM图以及放大的STEM图[42]; (h) Ge量子线各个生长阶段的AFM线扫描图[42]

图 5 (a)具有凹槽结构的Si (001)图形衬底的表面AFM图[42]; (b)生长Si0.75Ge0.25层后形成一维SiGe条带结构的表面AFM图[42]; (c) SiGe条带上形成Ge量子线的表面AFM图, 插图为量子线的晶面分析图, Ge量子线的两个侧面均为{105}晶面[42]; (d)和(e)分别为Ge量子线的横截面STEM图及放大的STEM图[42], 插图为Ge量子线的横截面全貌图; (f)和(g)分别为Ge量子线沿线方向的高分辨STEM图以及放大的STEM图[42]; (h) Ge量子线各个生长阶段的AFM线扫描图[42]Figure5. (a) AFM image of trench-patterned Si (001) substrate[42]; (b) AFM image of SiGe mound after the growth of Si0.75Ge0.25 layer[42]; (c) AFM image of Ge hut wire on Si0.75Ge0.25 mound after the Ge layer deposition with subsequently annealing, where inset image shows the {105} side faceted Ge hut wires[42]; (d), (e) cross-sectional STEM image and magnified STEM image of a Ge hut wire, respectively[42], where inset is the overall view of a hut wire; (f), (g) STEM image and magnified STEM image along a Ge hut wire, respectively[42]; (h) AFM line-scans showing the growth process of a Ge hut wire[42].

棚屋型Ge量子线的位置、周期、长度和形状完全依赖于凹槽的位置、周期、长度和形状. 通过控制凹槽的周期实现了如图6(a)所示的紧邻平行的Ge量子线. 通过控制凹槽长度获得了长度为10 μm的Ge量子线(图6(b)), 原则上, Ge量子线的长度可以任意长. 此外, 通过控制凹槽的形状还实现了闭合结构的口字形(图6(c))以及L形(图6(d)) Ge量子结构. 凹槽的深度和侧壁倾角对量子线的形成和位置也有重要影响[124], 当凹槽的深度较浅, 例如深度为6 nm, 宽度为60 nm时, 如果沉积低Ge含量SiGe层并原位退火处理, SiGe会优先向凹槽内部扩散, 在槽内形成有序的GeSi量子线[125] (图6(e)). 槽内GeSi量子线同样具有{105} 晶面, 其横截面为三角形, 高度约为8 nm (图6(h)), 且同样可以通过调节凹槽的周期和位置来控制量子线的周期和位置(图6(f)和图6(g)). 槽内GeSi量子线中Ge的含量仅30%左右, 通过采用应力诱导的多层生长方法, 本课题组已经成功实现了槽内Ge量子线的有序生长.

图 6 (a)—(d)在Si (001)衬底上凹槽边缘生长的紧邻平行排列的Ge量子线、长度为10 μm的Ge量子线、口字形和L形Ge量子线的AFM图[42]; (e)—(g) Si (001)衬底上凹槽内部生长的Ge0.33Si0.67量子线的表面AFM图, 周期分别为1 μm, 2 μm及500 nm[125]; (h)凹槽内部生长的单根Ge0.33Si0.67量子线的线扫描图, GeSi量子线的侧壁倾角为11.3°, 侧壁为{105}晶面[125]

图 6 (a)—(d)在Si (001)衬底上凹槽边缘生长的紧邻平行排列的Ge量子线、长度为10 μm的Ge量子线、口字形和L形Ge量子线的AFM图[42]; (e)—(g) Si (001)衬底上凹槽内部生长的Ge0.33Si0.67量子线的表面AFM图, 周期分别为1 μm, 2 μm及500 nm[125]; (h)凹槽内部生长的单根Ge0.33Si0.67量子线的线扫描图, GeSi量子线的侧壁倾角为11.3°, 侧壁为{105}晶面[125]Figure6. (a)?(d) AFM images of closely spaced parallel Ge hut wires, Ge hut wires with length of 10 μm, square-shaped and L-shaped Ge hut wires at the edges of trenches on Si (001) substrate, respectively[42]; (e)?(g) AFM images of Ge0.33Si0.67 hut wires inside the trenches on Si (001) substrate with a period of 1 μm, 2 μm and 500 nm, respectively[125]; (h) AFM line-scan of a Ge0.33Si0.67 hut wire inside the trench, which shows the {105} side facet with an inclination angle of 11.3°[125].

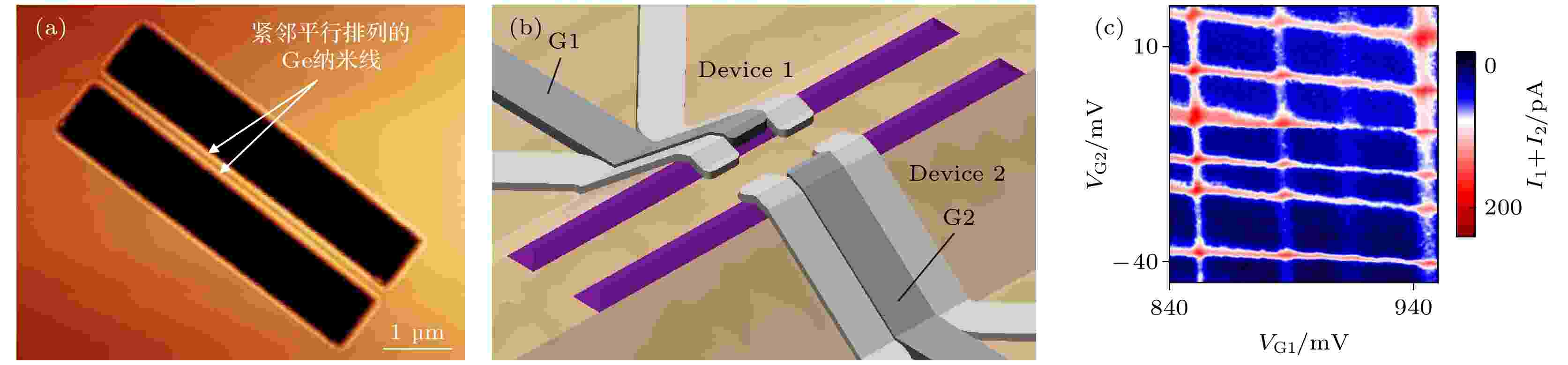

基于有序Ge量子线的器件研究还处于起始阶段, 基于凹槽边缘的棚屋型Ge量子线制备了单量子点器件, 观察到了典型的库仑阻塞现象, g因子最高可达3.91[42], 同时观测到了重空穴态的零场分裂现象[126], 表明量子线具有强的自旋-轨道耦合相互作用, 且可以利用电场对自旋-轨道耦合强度进行调控. 此外, 实现了两个紧邻平行排列Ge量子线(图7(a))上单量子点间的电容耦合. 器件示意图如图7(b)所示, 图7(c)为单量子点器件1和2的总电流与门电压VG1和VG2的关系图, 从图中的交叉点处可以看出, 当1个空穴隧穿过任意1个器件时, 另1个器件的库仑峰就会出现位移, 表明两个量子点之间出现了耦合.

图 7 (a)紧邻平行排列的Ge量子线AFM图; (b)双量子点器件结构示意图[42]; (c)总电流I1 + I2与VG1以及VG2的变化关系图[42]

图 7 (a)紧邻平行排列的Ge量子线AFM图; (b)双量子点器件结构示意图[42]; (c)总电流I1 + I2与VG1以及VG2的变化关系图[42]Figure7. (a) AFM image of the closely spaced parallel Ge hut wires; (b) schematic diagram of double quantum dot devices[42]; (c) total current I1 + I2 versus VG1 and VG2[42].

位错、应力、原子占位、原子台阶、同位素纯化程度和纳米线结构与成分的可控制备等都是影响量子比特性质和集成的关键因素. 未来量子计算芯片材料的研究主要目标是实现晶圆级硅锗量子材料原子尺度的可控制备, 以推动硅基量子计算领域的发展.