全文HTML

--> --> -->引起SPAD器件暗计数的载流子被称为暗载流子, 暗载流子通常来自于热激发与隧穿效应[6,7]. 在热激发的作用下, PN结中的少数电子会发生能带跃迁, 在价带中留下空穴, 在SPAD器件内的强电场作用下触发雪崩, 产生暗计数. 隧穿效应一方面发生在强电场情况下, 能带间距减小使得带-带隧穿(band-to-band tunneling, BTBT)的影响加剧; 另一方面, SPAD器件中存在缺陷, 通过缺陷辅助隧穿(trap-assisted tunneling, TAT)同样会产生暗计数. 并且由于工艺节点不断降低, 有源区掺杂浓度不断提高, 雪崩区电场不断增强, TAT的影响逐渐成为暗计数的主要来源[8]. 此外, 后脉冲(after pulsing, AP)是SPAD器件的另一种暗噪声来源, 雪崩过程中会产生大量载流子, 半导体材料中的陷阱能级会俘获其中一部分载流子并在短时间内重新释放, 此时若器件仍处于反偏状态便会再次触发雪崩, 造成误判断.

SPAD器件中的缺陷密度主要受工艺影响, 由于CMOS图像传感器(CMOS image sensor, CIS)工艺采用高纯度的硅, 制成的SPAD缺陷较少, 更易于获得较低的暗计数[9,10], 但制造成本相对昂贵. 而低成本标准CMOS工艺下的SPAD缺陷密度较高, 缺陷相关暗计数噪声十分严重, 因此如何降低标准CMOS工艺下SPAD暗计数的方法得到广泛的研究. 近些年的研究一方面通过优化SPAD的结构, 利用标准工艺提供的更深的注入层形成更深的雪崩区, 其受到缺陷的影响更小, 从而改善器件的暗计数性能[11,12], Bose等[11]基于0.18-μm CMOS工艺制作了p+/nwell, pwell/dnw, nwell/psub三种雪崩区从浅到深的结构及一种n+/pub结构, 结果显示, 对于三种雪崩区从浅到深的结构, 随着雪崩区的变深, 其受到器件表面缺陷的影响减小, 暗计数率(dark count rate, DCR)随之不断降低. 另一方面, 通过优化保护环的结构来减小器件表面及浅沟道隔离区(shallow trench isolation, STI)附近的电场以减小表面暗电流, 在降低边缘击穿概率的同时也能够减小暗计数[13,14]. Accarino等[14]基于0.18-μm标准CMOS工艺, 在深P阱中注入浅P阱形成保护环, 在室温4 V过偏压下的DCR仅为217 Hz, 相比只用P阱的保护环结构有了显著的改善. 此外, 其他材料雪崩光电二极管在优化保护环设计时还会改良扩散/注入工艺来削弱暗电流的影响[15,16]. 上海技术物理研究所的李庆等[16]研究了引入不同保护环结构的HgCdTe电子雪崩光电二极管的噪声特性, 发现保护环的引入可以削弱由表面电场引起的暗电流从而减小暗噪声, 并且退火过程不但可以将雪崩区与损伤区分开, 而且有利于形成轻掺杂雪崩区, 因此合适的退火工艺可以有效抑制暗噪声. 然而, 一个高性能器件的结构设计往往需要考虑诸如掺杂浓度、位置分布和工艺约束等许多繁复的方面, 会消耗较多的时间、精力和研究成本, 甚至会提高工艺复杂度, 先进工艺的采用更是增加了制作成本. 因此, 探究出一种简单、有效、低成本的暗计数降低方法尤为重要.

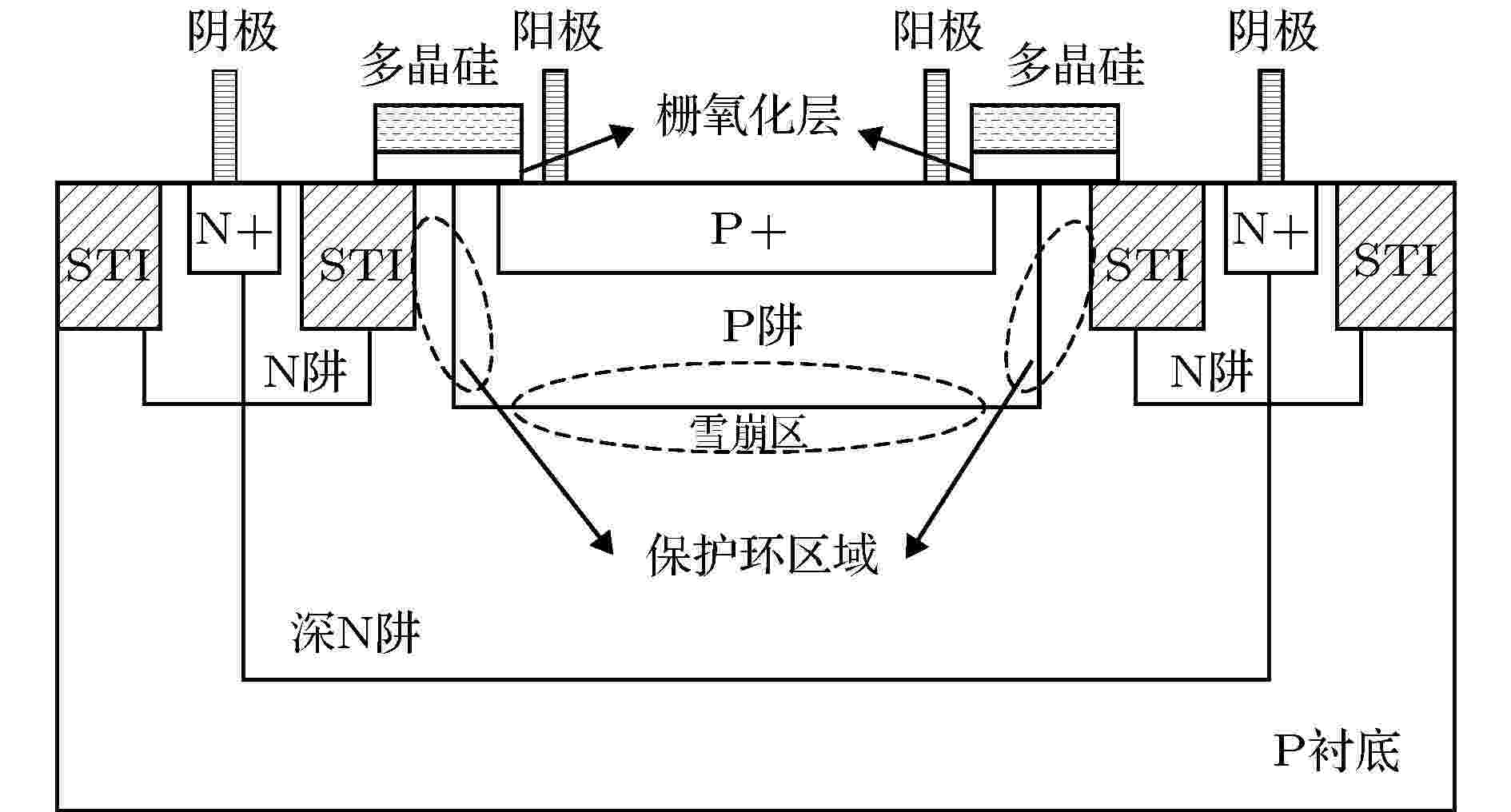

利用多晶硅场板不仅能有效降低SPAD器件的暗计数率, 而且实现方法简单, 与标准CMOS工艺中淀积多晶硅栅级同步制作, 不需要额外的工艺步骤, 制造成本低. 本文基于SMIC 0.18-μm标准CMOS工艺研究了采用多晶硅场板降低SPAD暗计数的物理机理. 首先介绍了多晶硅场板结构的SPAD器件的设计与测试, 对比分析在P+有源区和STI之间淀积多晶硅场板前后器件暗计数特性的变化情况. 然后进行了SPAD器件的建模与TCAD仿真, 探究多晶硅场板对保护环区域电场的影响. 最后分析讨论多晶硅场板降低器件暗计数的物理机理.

图 1 淀积了多晶硅场板的P+/P阱/深N阱SPAD器件结构示意图

图 1 淀积了多晶硅场板的P+/P阱/深N阱SPAD器件结构示意图Figure1. Structure of the P+/P-well/deep N-well SPAD device with polysilicon field plate.

该SPAD器件的制作流程完全基于SMIC 0.18-μm标准CMOS工艺, 无需改变任何工艺条件, 主要的前端制备工艺步骤如图2所示. 在晶圆的准备工作完成后, 首先进行STI的刻蚀, 并进行垫氧, 填充高密度等离子体(high density plasma, HDP), 形成STI区域; 然后依次进行深N阱-N阱-P阱的离子注入, 再进行高温退火, 分别形成深N阱、N阱和P阱区域; 之后淀积栅氧化层和多晶硅栅极, 此时多晶硅场板和MOSFET的多晶硅栅极同时形成, 不需要额外的工艺步骤; 最后进行MOSFET源、漏区的N+和P+离子注入, 然后再进行快速热退火, 从而形成SPAD器件的的N+及P+有源区. 最后按照一般CMOS后端工艺步骤形成接触孔、介质层、通孔、金属层和钝化层. 器件完成所有流片步骤后就可以对器件进行封装测试.

图 2 主要前端工艺步骤

图 2 主要前端工艺步骤Figure2. Main front-end process steps.

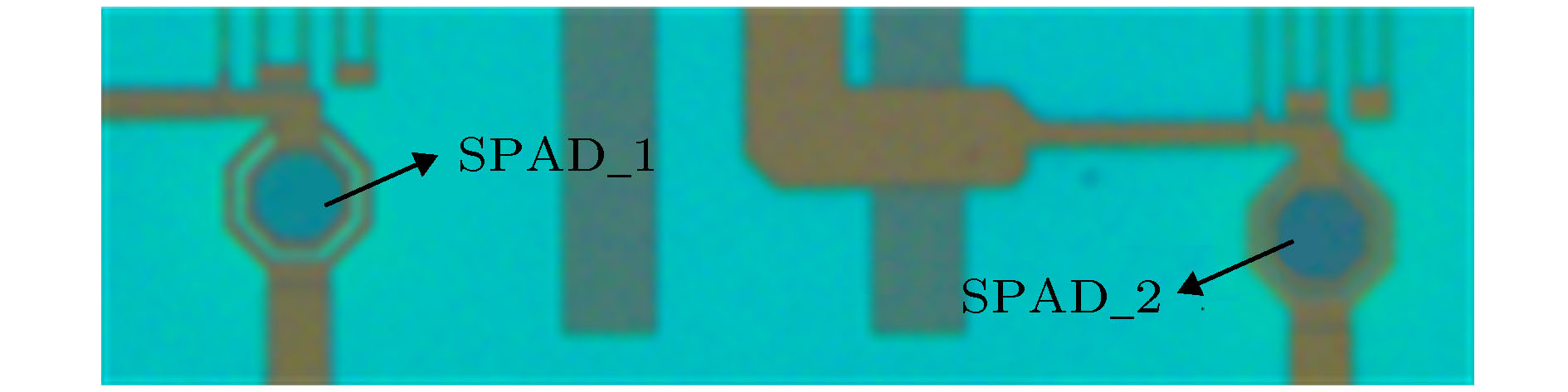

为了进行暗计数噪声性能的对比研究, 无多晶硅场板结构的SPAD器件也进行了流片制作, 两种SPAD器件的尺寸完全相同, 流片后的显微照片分别如图3所示, 器件位置如箭头标注. SPAD_1没有淀积多晶硅场板, 而SPAD_2的P+有源区和STI之间区域的上方淀积了多晶硅场板. 在Cascade探针台上对SPAD_1和SPAD_2的暗计数率进行了测试. 分别将SPAD器件的阴极、阳极以及接地电极通过探针引出. SPAD的阳极连接一个阻值为100 kΩ的电阻, 电阻的另一端接地, 起到被动淬灭的作用.

图 3 器件显微照片

图 3 器件显微照片Figure3. Micrograph of the devices.

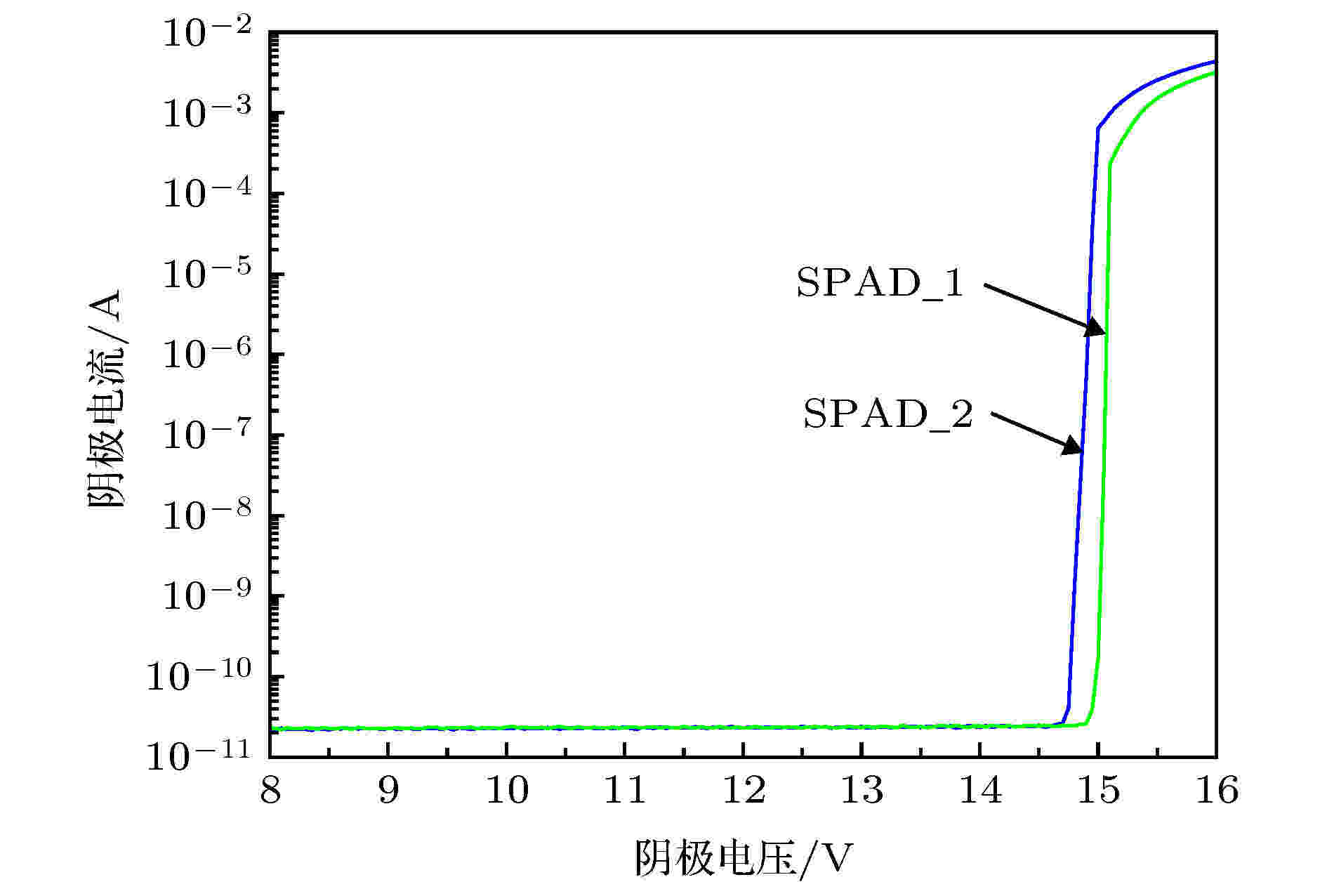

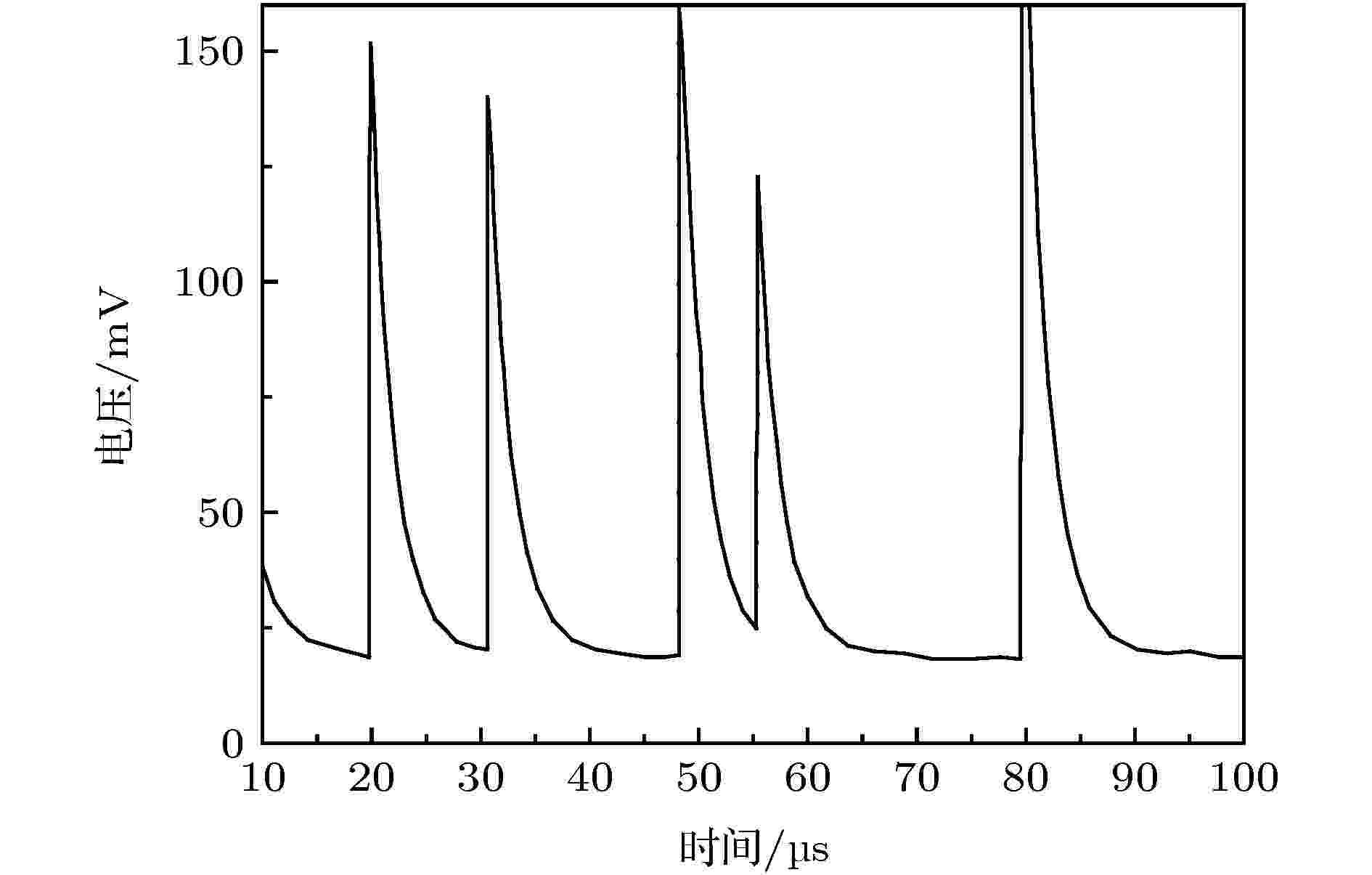

首先测试了SPAD器件的反向I-V特性, 得到器件雪崩电压. 图4展示了对器件阴极进行电压扫描操作得到的I-V特性曲线. 由于SPAD_1和SPAD_2的结构只有多晶硅场板的区别, 所以它们的雪崩电压几乎相同, 分别为15 V和14.7 V. 进一步对SPAD器件的DCR进行测试, 当器件工作在盖革模式下, 示波器观察到的器件阳极输出的雪崩脉冲信号如图5所示. 雪崩电流产生后阳极电压上升, 淬灭复位结束, 这个过程大约需要10 μs. 可以看到有的单个雪崩脉冲上存在两个尖峰, 即发生了后脉冲现象. 后脉冲严重依赖于温度, 温度越低, 后脉冲概率便越大. 并且主要受雪崩触发概率、陷阱能级的载流子俘获率和陷阱能级密度的影响, 通过降低反偏电压、减小材料陷阱能级密度以及利用有源淬灭实现可调死区时间等可以有效抑制后脉冲的产生及其干扰.

图 4 器件I-V特性曲线图

图 4 器件I-V特性曲线图Figure4. I-V characteristic curve of the devices.

图 5 雪崩脉冲电压信号

图 5 雪崩脉冲电压信号Figure5. Avalanche pulse voltage signal.

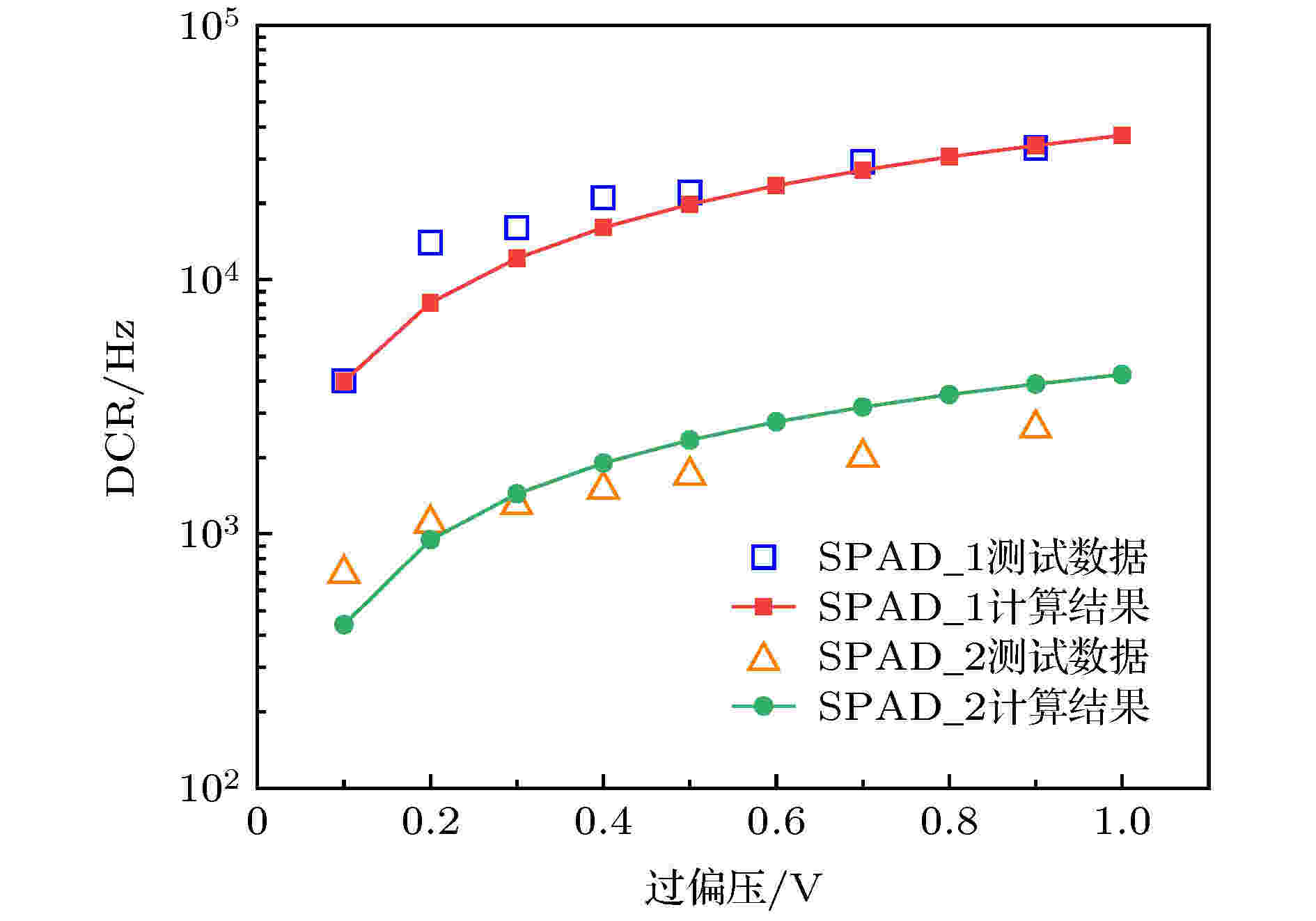

在室温下测得的两种SPAD器件的DCR随过偏压的关系如图6所示. 在0.1 —1.0 V的过偏压范围内, 两个器件的DCR都随过偏压逐渐上升. SPAD_1的DCR从10 kHz左右增加到了40 kHz左右, 整体暗计数水平较高; 而淀积了多晶硅场板的SPAD_2的DCR低于3 kHz, 比SPAD_1的DCR降低了一个数量级. 可以看出, 淀积多晶硅场板能明显改善SPAD器件的暗计数性能, 下面对SPAD_2做了进一步的性能测试, 详细观察其在不同过偏压和温度下的暗计数性能.

图 6 室温下SPAD暗计数率与过偏压关系

图 6 室温下SPAD暗计数率与过偏压关系Figure6. DCR as a function of excess bias voltage at room temperature.

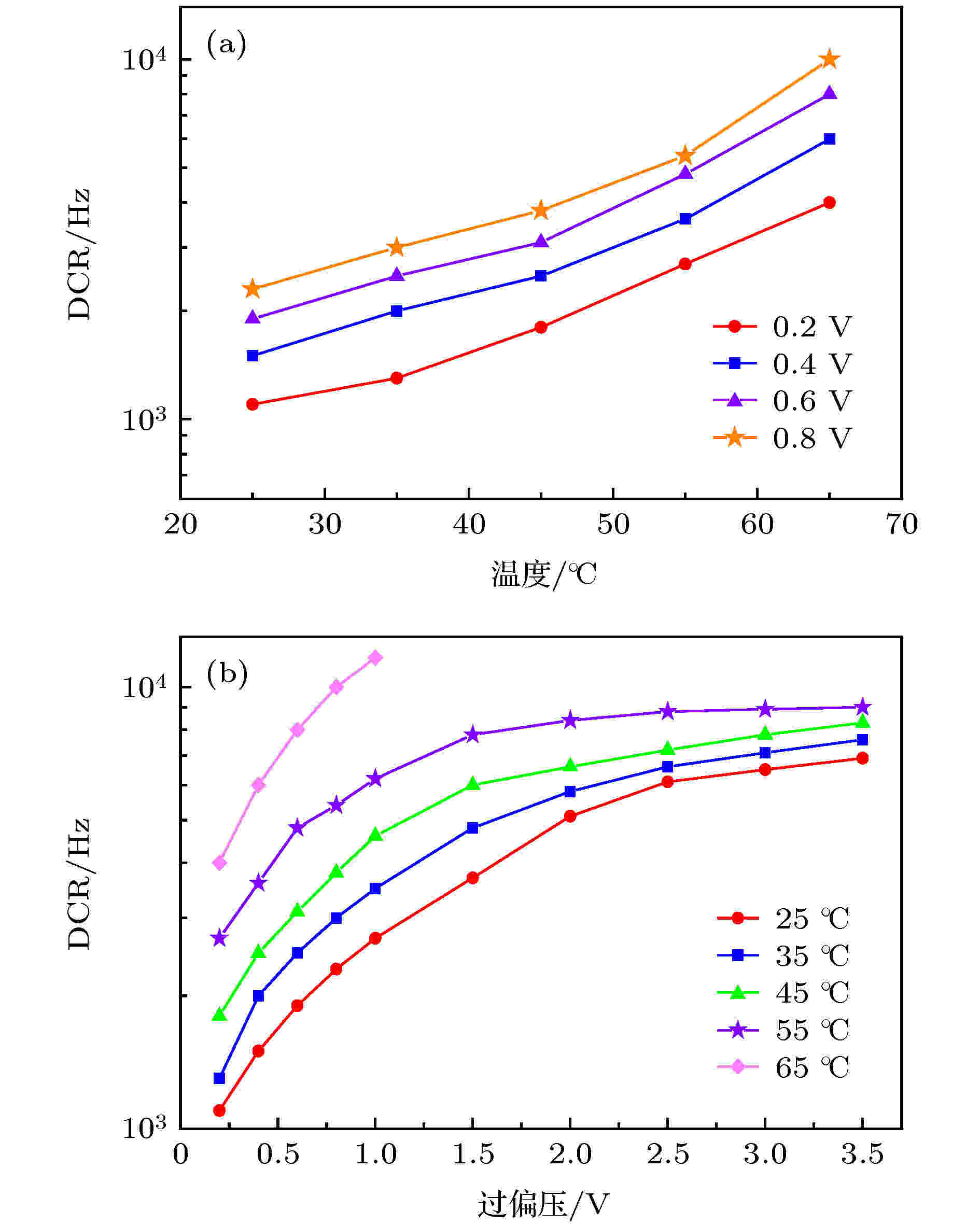

图7(a)展示了SPAD_2在不同过偏压下的DCR随温度变化的关系, 当温度由25 ℃变化至65 ℃时, DCR显著增加, 体现了温度对该器件的强烈影响, 说明DCR的主要来源不是BTBT, 而是与缺陷相关的暗计数[18]. SPAD_2在不同温度下的DCR随过偏压的变化情况如图7(b)所示, 65 ℃时的实验数据不全, 这是因为器件能承受的最高温度为65 ℃左右, 在该温度下持续工作一段时间后器件无法正常工作. 温度低于55 ℃时, 在过偏压由0.1 V上升至3.5 V的过程中, SPAD器件的DCR逐渐增加, 随着雪崩触发概率趋于饱和, DCR的增加趋于平缓, 整体水平低于10 kHz. 在室温25 ℃下, 在过偏压1.5 V时, 器件的DCR为3.7 kHz. 测试结果表明在器件P+有源区和STI之间淀积多晶硅场板可以明显改善SPAD器件的暗计数性能. 即便是在55 ℃下, 淀积了多晶硅场板的SPAD_2的暗计数性能都优于室温下没有多晶硅场板的SPAD_1.

图 7 SPAD_2的DCR变化曲线图 (a) 不同过偏压下的温度特性; (b) 不同温度下的过偏压特性

图 7 SPAD_2的DCR变化曲线图 (a) 不同过偏压下的温度特性; (b) 不同温度下的过偏压特性Figure7. DCR of SPAD_2 as a function of (a) temperature at different excess bias voltage, and (b) excess bias voltage at different temperature.

当考虑了保护环区域对暗计数产生的贡献, 则器件的缺陷相关DCR可由下式计算:

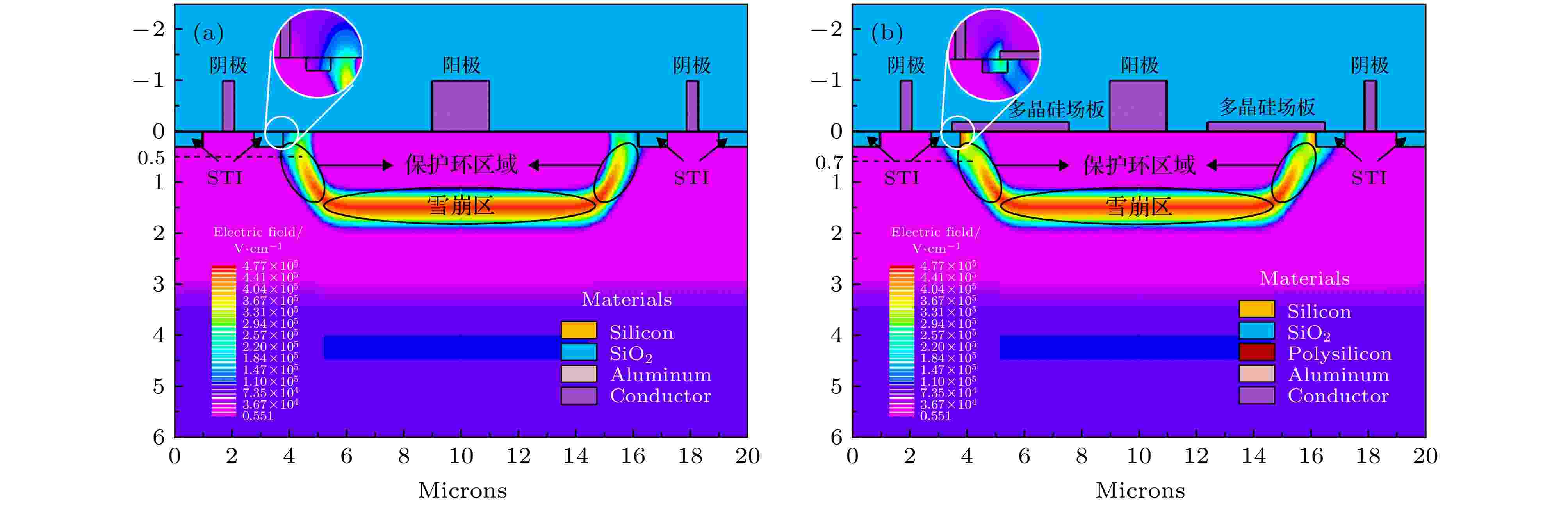

为了能准确得到DCR模型中的关键参数如雪崩触发概率和电场分布, 我们进行了TCAD仿真. 首先基于SMIC 0.18-μm工艺流程, 使用SILVACO Athena工具对P+有源区直径为10 μm的SPAD_1和SPAD_2进行了二维工艺仿真, 然后根据工艺仿真获得的器件结构和杂质分布, 再使用SILVACO Atlas工具进行了盖革模式的二维器件仿真. 在TCAD仿真时, 除了在SPAD_2的P+有源区和STI之间设置了多晶硅场板外, 两个SPAD器件其他参数的设置都相同. 直径10 μm的P+有源区注入在一个浅P阱中, 结深约为2.2 μm, 峰值浓度约为6 × 1017 cm–3, 深N阱在结深1.5 μm处的峰值浓度约为2 × 1017 cm–3. 在器件仿真中采用了Conmob和Fldmob迁移率模型、SRH载流子产生-复合模型、Selberherr碰撞电离模型和Geiger模型等以获得器件的电学特性, 对比了SPAD器件淀积多晶硅场板前后的电场分布.

图8(a)和 图8(b)分别为SPAD_1和SPAD_2的二维电场仿真分布图, 对STI及保护环表面区域的电场仿真结果进行了局部放大显示. 可以看出两个器件的雪崩区电场几乎相同, 结深约为1.5 μm, 厚度约为0.8 μm, 峰值电场达到4.7 × 105 V/cm. 而在保护环区域, 没有多晶硅场板的SPAD_1的电场仍然较强, 处于105 V/cm的量级; 而淀积了多晶硅场板的SPAD_2保护环区域的峰值电场被引入了STI内部, 硅表面下0.5—0.7 μm处的电场显著降低, 保护环区域的整体电场相比SPAD_1降低了25%, 从而有效削弱了STI附近缺陷相关的非平衡载流子借助电场向保护环边界漂移所产生的暗计数噪声. 盖革模式TCAD仿真进一步揭示SPAD_2器件除了保护环区域电场被削弱了以外, 保护环区域的雪崩触发概率也明显降低, 在0.4 V过偏压下SPAD_1和SPAD_2的Pr分别为0.07和0.01. 除此之外, 两个器件的其他的DCR模型计算的参数都一样, 表1列出了过偏压为0.4 V时室温下的其他关键模型参数.

| 参数 | 描述 | 值 |

| Aa/μm2 | 雪崩区面积 | 63.6 |

| Ar/μm2 | 保护环区域面积 | 49.4 |

| Wa/μm | 雪崩区厚度 | 0.8 |

| Wr/μm | 保护环区域厚度 | 0.8 |

| Pa | 雪崩区平均雪崩触发概率 | 0.09 |

| $ m_{\rm n}^*/m_0 $ | 电子有效质量 | 0.43 |

| $ m_t^*/m_0 $ | 电子隧穿有效质量 | 0.25 |

| m0/10–31 kg | 电子静止质量 | 9.108 |

| ni/1010 cm–3 | 本征载流子浓度 | 1.5 |

| k/10–23 J·K-1 | 玻尔兹曼常数 | 1.38 |

| $\hbar $/10–34 J·s | 狄拉克常数 | 1.054 |

| q/10–19 C | 电子电荷量 | 1.602 |

表1关键模型参数取值 (温度T = 300 K, 过偏压VEX = 0.4 V)

Table1.Summary of the key parameters for model-ing (T = 300 K, VEX = 0.4 V).

图 8 TCAD二维电场仿真图 (a) SPAD_1; (b) SPAD_2

图 8 TCAD二维电场仿真图 (a) SPAD_1; (b) SPAD_2Figure8. TCAD simulation of 2D electric field: (a) SPAD_1; (b) SPAD_2.

图 9 模型算得室温下SPAD暗计数率与过偏压关系图

图 9 模型算得室温下SPAD暗计数率与过偏压关系图Figure9. Calculated DCR as a function of excess bias voltage at room temperature.

测试数据与模型计算结果都表明, 淀积多晶硅场板可以显著降低器件暗计数. 从DCR模型中可以看出SPAD器件的DCR主要受温度、电场和缺陷密度等因素的影响, 并且与这三者都是正相关, 也就是说, 温度越高, 电场强度越强, 缺陷密度越大, 暗计数水平就会越高. 考虑到TAT机制的影响越来越严重, 器件整体DCR主要产生于缺陷密度高的区域, 削弱高缺陷密度区域的电场将会有效抑制缺陷相关暗计数的产生, 从而改善器件暗计数性能. 在SPAD器件中, 晶圆表面相对而言缺陷较多, 并且在形成STI时, 光刻、刻蚀等工艺步骤又会在晶圆上引入较多的缺陷, 保护环区域相比雪崩区更靠近器件表面和STI, 缺陷密度更高, 缺陷相关暗计数的产生几率变大. 因此削弱保护环区域的电场是一种可行的改善器件暗计数性能的方法.

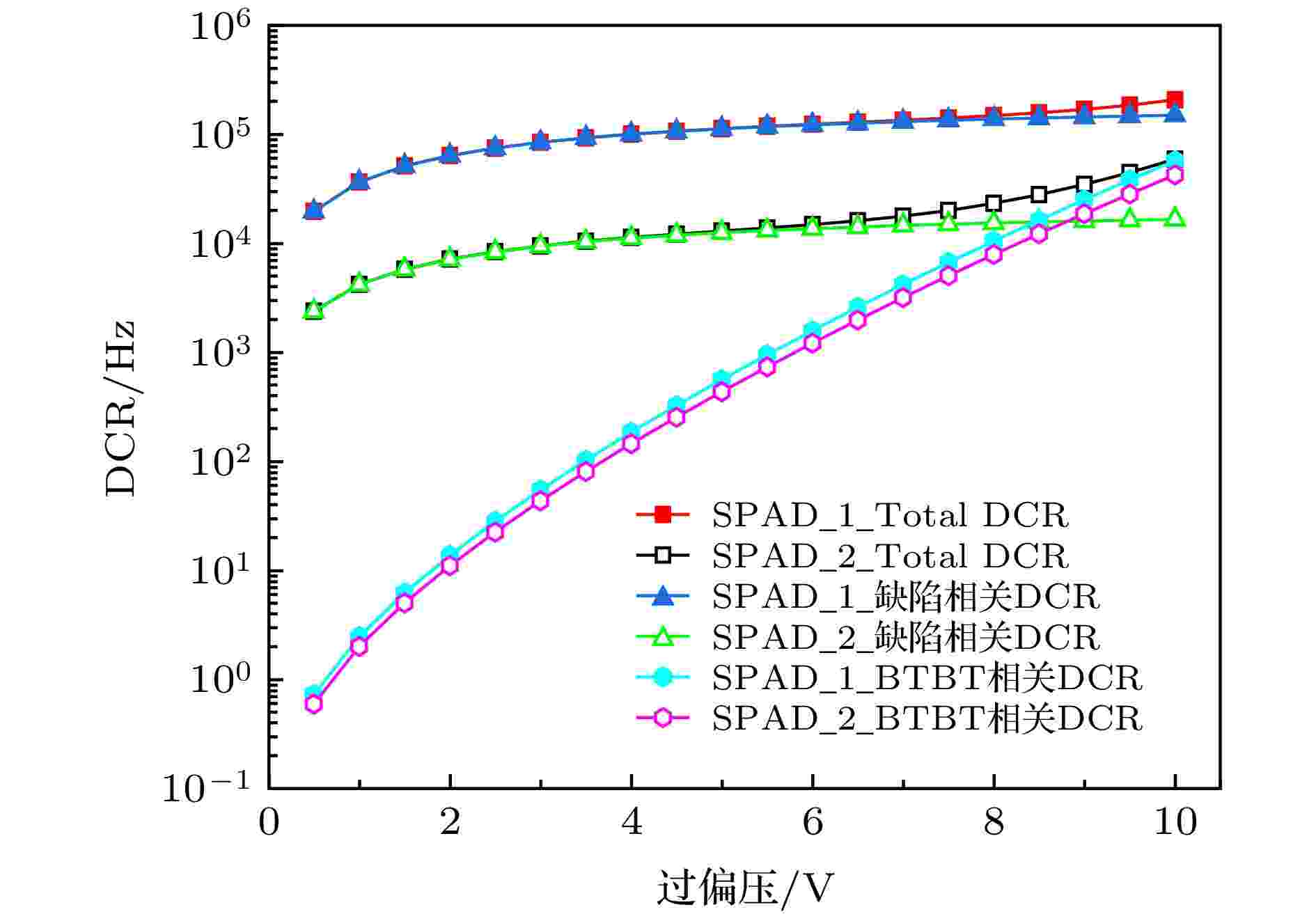

为了进一步明确DCR降低的主要来源, 考虑BTBT机制对暗计数的影响, 在0—10 V过偏压范围内进行了仿真计算, 其中BTBT相关载流子产生率表示为:

图 10 室温下0—10 V过偏压范围内的DCR变化情况

图 10 室温下0—10 V过偏压范围内的DCR变化情况Figure10. Variety of DCR under 0–10 V excess bias voltage at room temperature.

场板在功率器件中是一种通过调制耗尽区电场分布以提高器件击穿电压的电场优化技术[22], 其本质往往是在主结的边缘形成PN结或金属-氧化物-半导体(MOS)结构. 外加反向偏压时, 其耗尽区会往半导体内部扩展, 削弱边缘密集的电场[23]. 本文利用浮空场板形成MOS结构, 无需施加电压偏置, 由场板所处的场势环境决定其电势, 通过场板使保护环区域的雪崩区横向扩展, 将保护环区域的一部分电场线转移至场板边缘, 从而降低了高缺陷密度的保护环区域的电场. 仿真结果表明, 淀积了多晶硅场板后, 保护环区域的峰值电场被引入了STI内部, 保护环区域电场被降低, 缺陷相关载流子的产生明显减少, 从而显著降低了器件暗计数噪声. 而场板的引入对雪崩区的影响微乎其微, 不会影响雪崩区的深度、厚度、电场分布和掺杂情况等, 而SPAD器件的其他关键性能参数例如光子探测效率(photon detection efficiency, PDE)主要与雪崩区深度、厚度和电场强度有关; 时间抖动主要受过偏压大小和工艺掺杂的影响. 多晶硅场板的淀积没有改变这些影响因素, 从而在降低了器件暗计数的同时不会对器件的探测性能造成影响. 因此合理地设置多晶硅场板可以有效改善器件的暗计数性能.