全文HTML

--> --> -->大尺寸超高分辨率面板为了实现无边框设计, 需要在显示区周边集成阵列基板栅极驱动(gate driver on array, GOA)电路[7,8]. 显示区的IGZO TFT尺寸都采用同样的宽长比(W/L), 而GOA电路的每个单元都密集分布着十多个不同W/L的IGZO TFT. 这样的GOA单元在扫描线两侧同时设计, UHD和QUHD面板上的数量分别达到4320个和8640个. 另外, GOA电路位于基板玻璃或者面板的周边, ESD风险相对更高. 通过调整GOA电路单元的器件组合、扫描线ESD保护电路结构、TFT开关态电压大小等参数, 发现ESD破坏的改善效果并不明显. 所以, 有必要在分析IGZO TFT器件的ESD应力的基础上, 对玻璃基板上的IGZO TFT, 特别是GOA电路中的IGZO TFT, 进行系统级的ESD研究, 并通过规模生产进行对策验证.

综合IGZO TFT器件工艺、GOA区与显示区金属密度比、栅极金属层与绝缘层厚度非均匀性分布等因素, 采用系统级ESD分析方法, 提出栅极Cu:SiNx/SiO2界面缺陷是导致GOA电路中IGZO TFT发生ESD失效的基本要素, GOA电路区域金属密度比高以及Cu:SiNx/SiO2三层薄膜厚度分布的非均匀性是诱发ESD失效的重要因素. Cu原子晶界扩散和界面扩散的激活能分别只有1.2 eV和0.7—1.0 eV, 小于Al的扩散激活能1.48 eV[9,10]. Cu会扩散进入SiNx/SiO2[11]. 因此, 栅极Cu:SiNx/SiO2界面性质关系到IGZO TFT可靠性. GOA区与显示区的Cu金属密度相差悬殊, 在工艺上容易引起GOA区的Cu:SiNx/SiO2界面缺陷[12-14]. 对应地, 我们提出了降低GOA电路中大尺寸IGZO TFT发生ESD失效风险的设计结构.

2.1.GOA电路

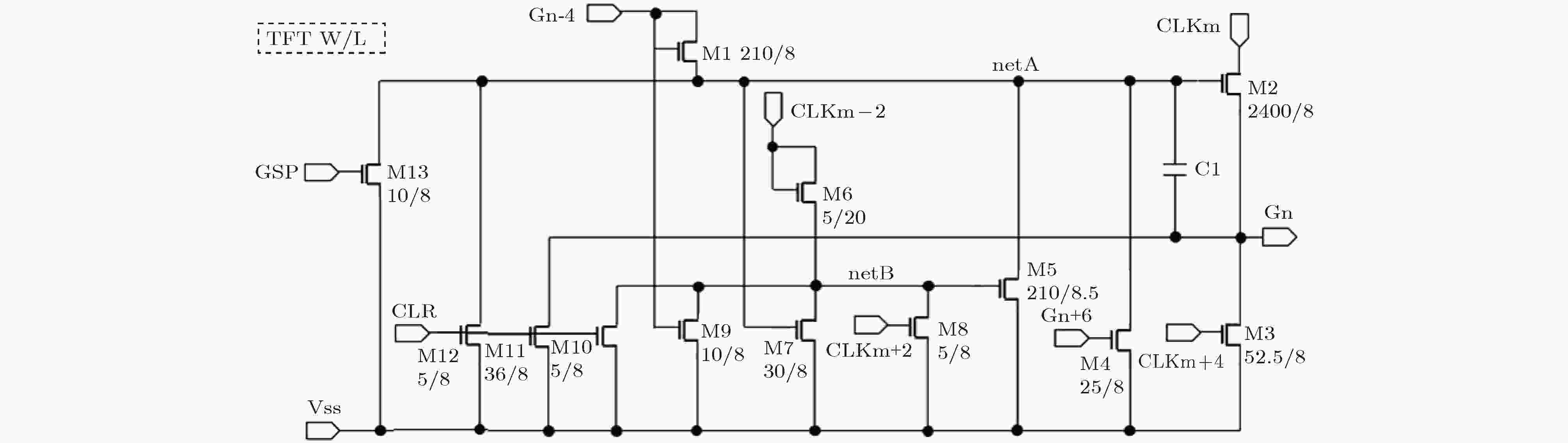

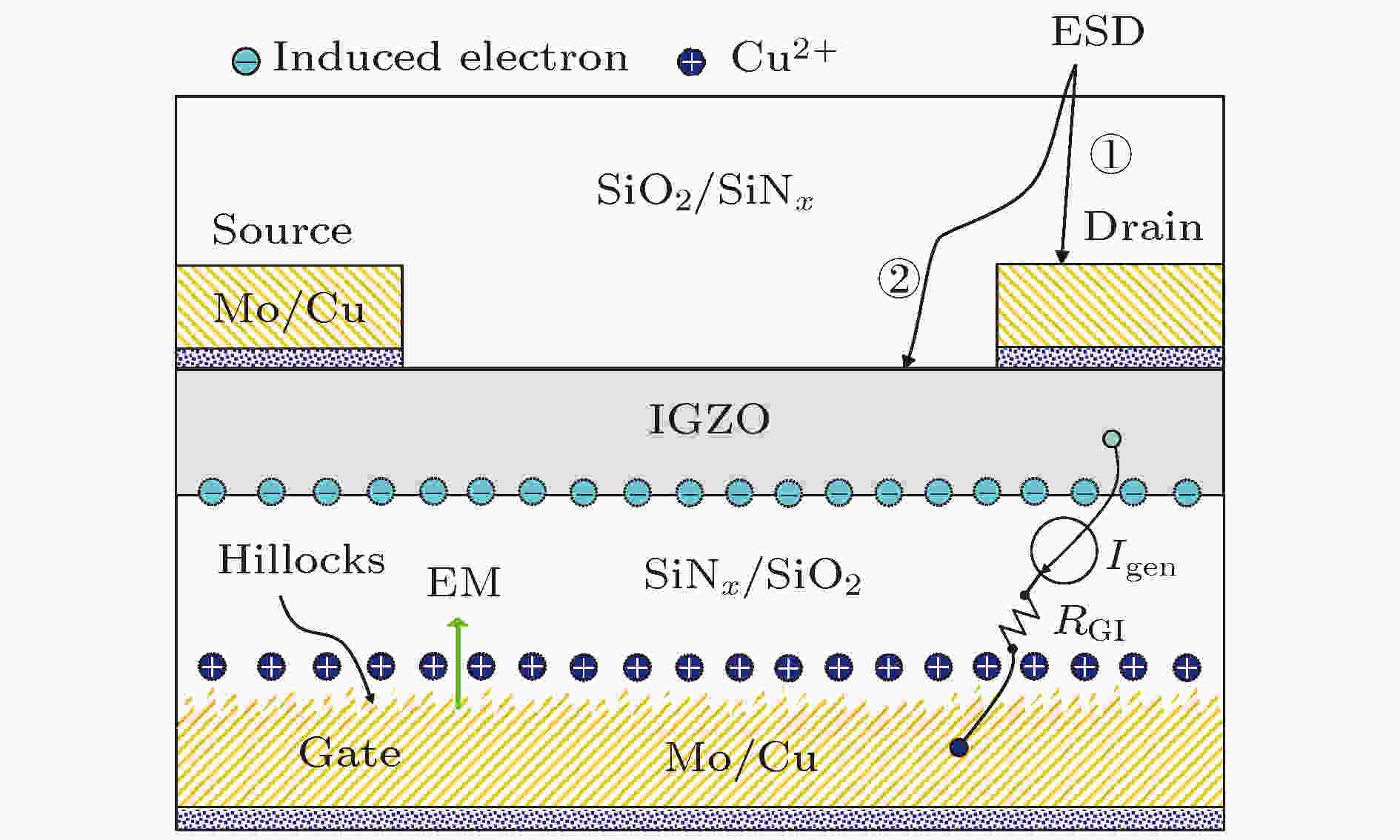

本研究的IGZO TFT背板的各层薄膜自玻璃基板起依次是Mo/Cu栅极层、SiNx/SiO2栅极绝缘层、IGZO有源层、Mo/Cu源漏极层、SiO2/SiNx保护层. 扫描线左右两侧的GOA驱动电路采用由13个IGZO TFT和1个电容构成的13T1C架构(图1). 该架构在4T1C架构基础上增加了GOA电路信赖性提升单元和辅助帧电荷清除单元, 其输入信号有: 初始置位信号GSP、时钟信号CLK1-CLK8、清空信号CLR和关态低电位VSS. 采用8根CLK可以降低时钟信号线的负载, 满足对上升时间的要求, 在降低功耗的同时提升显示区像素的充电能力[15]. 设计55寸UHD面板像素时, 保证数据线信号和扫描线脉冲信号的交叠时间控制在2 μs以内, 输出使能(output enable, OE)时间为1.8 μs, 以防止错误的数据线信号充入像素. 图 1 13T1C架构的GOA电路单元原理图

图 1 13T1C架构的GOA电路单元原理图Figure1. Diagram of the GOA circuit unit composed of 13 TFTs and 1 capacitor.

在13个IGZO TFT中, M2的沟道W/L最大, 达到2400 μm/8 μm. M2 TFT是扫描线脉冲信号的上拉模块, 其沟道宽度W越大, 扫描线脉冲信号的上升时间和下降时间越小. 上升时间越小, 预留的充电时间越长, 像素电压的充电率越高; 下降时间越小, 充入像素的信号电压越准确. M2 TFT沟道宽度的设计需要综合考虑版图空间.

2

2.2.GOA电路的ESD

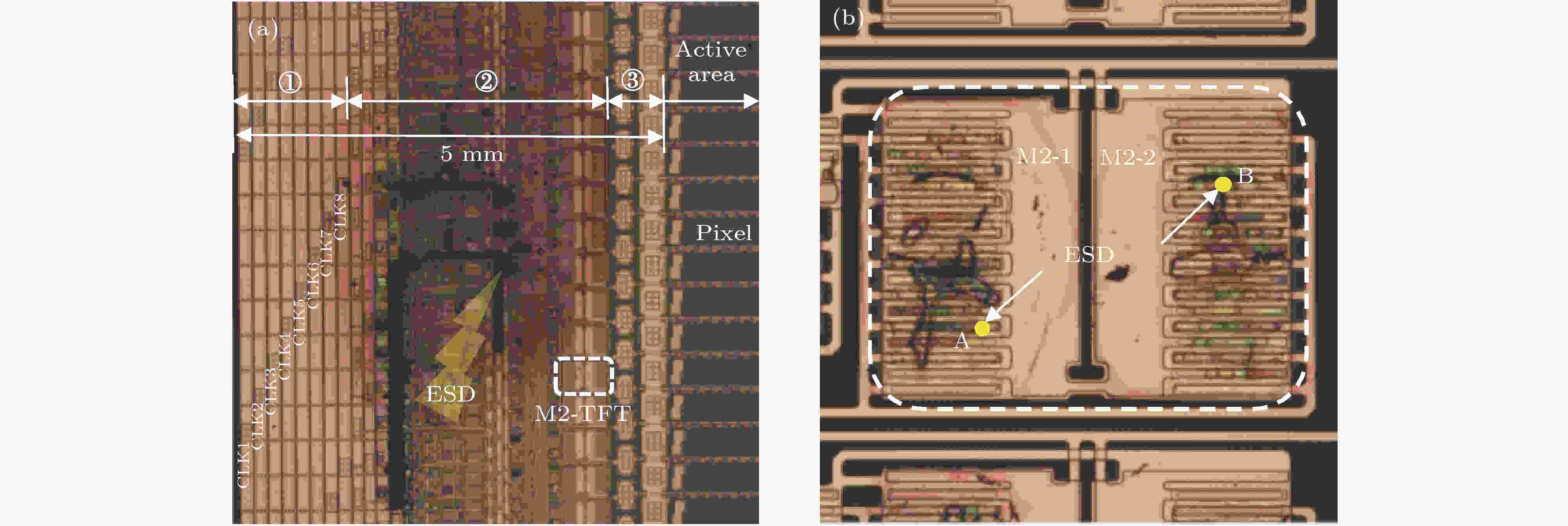

在IGZO TFT背板制作以及面板没有绑定IC前, 容易发生如图2(a)所示的GOA区域大面积ESD烧伤现象. 其中, 8根CLK的总线区①、GOA电路区②、扫描线ESD保护区③的合计总宽度约为5 mm. ESD烧伤区域从破坏严重的中心GOA单元向上下GOA单元传播, 范围可达到4 mm×10 mm. GOA电路右侧的扫描线ESD保护电路和左侧的时钟信号线受到ESD破坏的影响较小. 出现这种烧伤问题的GOA电路, 集中在玻璃基板边缘, 玻璃基板中央基本没有. 图 2 GOA电路的ESD破坏现象 (a) GOA区大面积的ESD烧伤现象; (b) M2 TFT的ESD破坏现象

图 2 GOA电路的ESD破坏现象 (a) GOA区大面积的ESD烧伤现象; (b) M2 TFT的ESD破坏现象Figure2. ESD damage phenomenon of GOA circuit: (a) Photo image of the overall GOA where ESD damage occurs. (b) photo image of ESD damage M2 TFT in the GOA unit.

对驱动IC绑定前的所有工序加强ESD保护对策后, GOA区域的大面积ESD烧伤现象有效减少. 但是, 依然存在个别IGZO TFT的ESD失效现象, 其中M2 TFT的ESD失效现象最严重. 如图2(b)所示, 观察到的ESD突发性损伤位置呈黑点状或者黑块状分布. 同时可以推断, 其他位置的IGZO TFT可能存在ESD潜在性损伤. 所以, 要系统研究IGZO TFT背板GOA电路的ESD失效机理.

2

2.3.ESD破坏区域分析

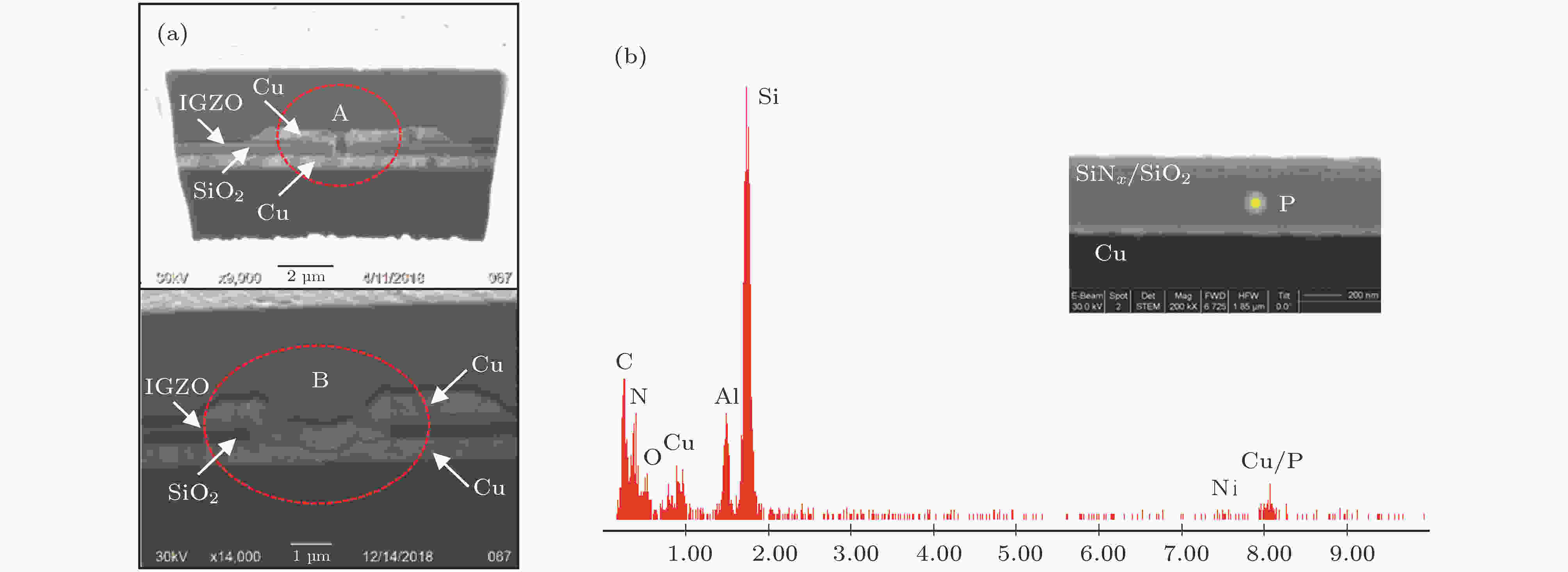

GOA电路的M2 TFT在扫描线ESD保护单元工作之前发生ESD破坏, 说明M2 TFT的抗ESD能力低. 在发生ESD破坏的M2 TFT中, 选取如图2(b)所示的A, B两个黑点状和黑块状位置, 利用FIB解析ESD破坏位置的各膜层状态, 发现ESD破坏发生在栅极绝缘层成膜后、源漏极金属层成膜前(图3(a)). 图 3 M2 TFT的ESD失效区域解析 (a) ESD失效位置的FIB断面解析; (b) ESD失效位置的栅极绝缘层元素分析

图 3 M2 TFT的ESD失效区域解析 (a) ESD失效位置的FIB断面解析; (b) ESD失效位置的栅极绝缘层元素分析Figure3. Analysis of ESD failure area of M2 TFT: (a) FIB section analysis of ESD failure position; (b) elemental analysis of gate insulator at failure position of ESD.

对I-V特性正常的M2 TFT栅极绝缘层进行EDS分析, 发现栅极Cu金属层上方的SiNx/SiO2绝缘层中, 在靠近SiO2的SiNx层中存在Cu原子成分(图3(b)). 初步判断, 栅极Cu原子扩散到SiNx/SiO2绝缘层中, 是影响IGZO TFT器件性能与导致ESD失效的一个重要因素.

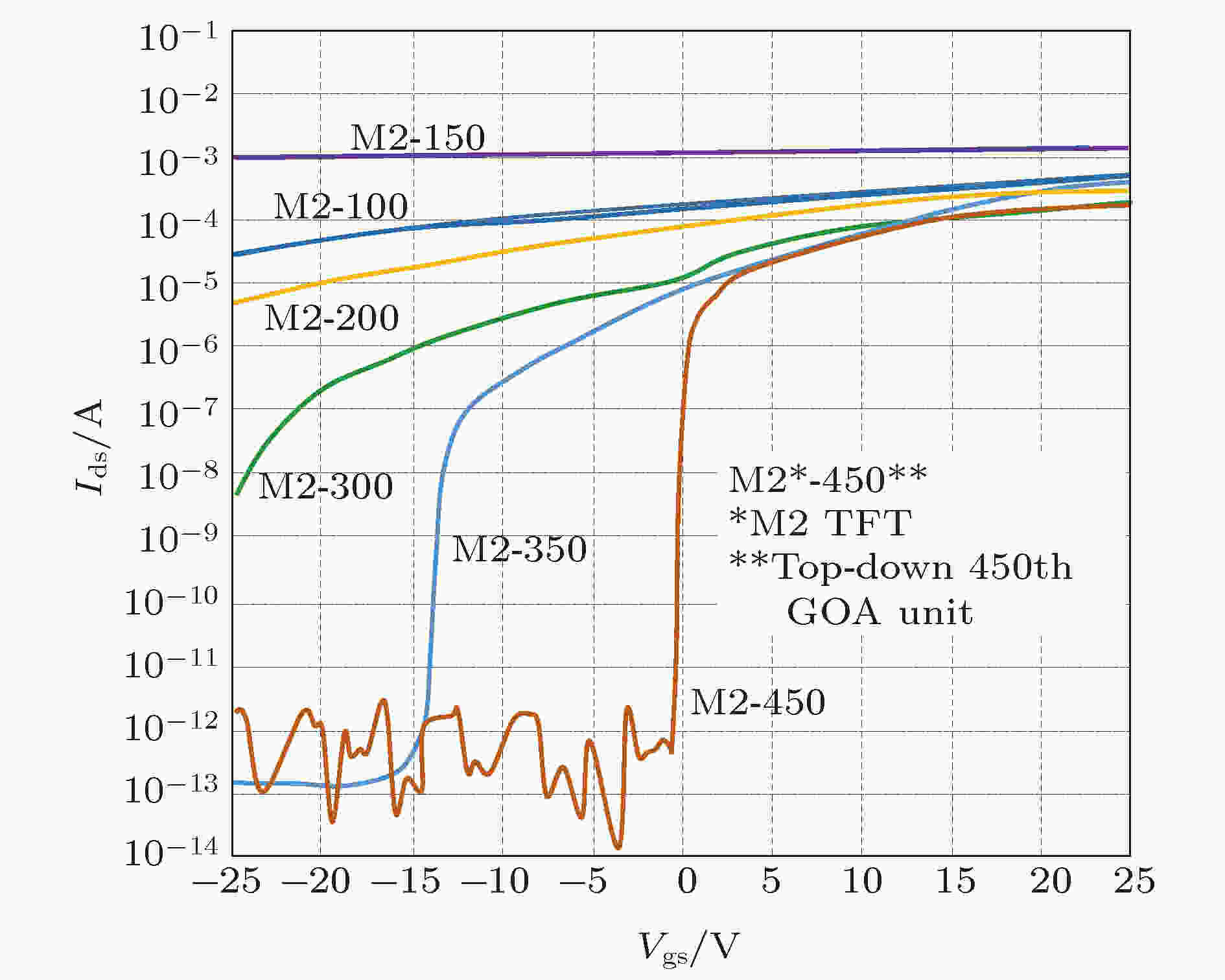

为了建立IGZO TFT器件性能恶化与ESD失效之间的关系, 针对沟道W/L最大、ESD破坏最严重的M2 TFT, 从靠近ESD烧伤区到远离ESD烧伤区, 分别检测器件的I-V特性. 如图4所示, 样品发生ESD烧伤的中心位置在第100个GOA单元到第200个GOA单元之间, 远离ESD烧伤区的M2 TFT(M2-450)特性正常, 越靠近ESD烧伤区的M2 TFT阈值电压(Vth)负漂越严重, 电流开关比越小, 直到器件(M2-100和M2-150)的源漏极与栅极完全短路.

图 4 距离ESD失效中心不同位置的M2 TFT特性

图 4 距离ESD失效中心不同位置的M2 TFT特性Figure4. M2 TFT characteristics at different positions from ESD failure center.

作为对比, 我们检测了靠近烧伤区的M1 TFT, M4 TFT, M7 TFT和M12 TFT等其他器件, I-V特性正常. 这表明沟道W/L最大的M2 TFT发生ESD破坏的风险最高; 并且, M2 TFT阈值电压负漂的绝对值与ESD破坏风险具有正相关性, 部分阈值电压负漂严重的M2 TFT已经导致对应的总线处于漏电状态.

3.1.器件级分析

栅极Cu金属在Cu:SiNx/SiO2界面的粘附性直接影响到Cu在SiNx/SiO2绝缘层中的扩散速率[16]. 用PECVD沉积SiNx/SiO2薄膜时, 等离子体不断地对Cu表面物理轰击并在Cu表面反应依次形成SiNx/SiO2. 由于SiNx/SiO2成膜时薄膜内的晶粒之间存在空隙, 部分Cu原子沿着SiNx/SiO2中的空隙扩散, 并在原来位置形成空隙, 在SiNx/SiO2中形成类似晶须的结构, 成为深能级杂质, 使器件性能退化甚至失效[17]. 栅极Cu与栅极绝缘层SiNx/SiO2界面的Cu表面的hillocks凸起位置, 是Cu离子向SiNx/SiO2层扩散的拥挤点. 一旦在栅极和源漏极(ESD stress ①), 或者栅极和IGZO有源层(ESD stress②)之间形成一定的压降, Cu与SiNx/SiO2界面由于电极反应产生大量的Cu离子, 向SiNx/SiO2层扩散, 在SiNx/SiO2层形成陷阱态. 如图5所示, Cu离子向IGZO沟道方向移动并大量积累, 形成空间电荷效应, 使IGZO层与SiNx/SiO2栅极绝缘层的表面势垒厚度减少, 势垒降低. Cu离子带正电, 扩散到SiNx/SiO2层形成空间分布状态, 会改变栅极绝缘层内电场强度的空间分布. 可以用泊松方程描述Cu离子扩散形成空间电荷效应的机理[18,19]: 图 5 Cu扩散引起的空间电荷效应与ESD失效机理

图 5 Cu扩散引起的空间电荷效应与ESD失效机理Figure5. Mechanism of space charge effect formed by Cu2+ ion entering SiO2.

IGZO TFT阈值电压Vth负漂, 可以看成是多种机制的组合, 即ΔVth, tot = Vth1 + Vth2 + ··· [20-22]. 图4中靠近ESD烧伤中心区的IGZO TFT阈值电压负漂的关键影响因素是栅极Cu扩散进入栅极绝缘层SiNx/SiO2引起的有效栅极绝缘层厚度减小以及内建电场效应. 由于内建电场效应, 当栅极和源漏极(ESD stress ①)或者栅极和IGZO有源层(ESD stress②)之间存在电压分布, 随着IGZO能带弯曲, IGZO有源层中的电子就很容易越过降低后的势垒, 在栅极绝缘层的陷阱态中进行跳跃导电, 甚至注入形成场致发射. 如果场致发射电流Igen接近限制电流, SiNx/SiO2栅极绝缘层的阻抗RGI将从高阻态变为低阻态, 丧失绝缘性能, 导致TFT器件失效[23]. Qiang等[22]和Wang等[24]提出, 用IGZO TFT栅极电压产生的强垂直电场的效应有助于捕获的载流子直接隧穿进入导电带, 并导致几乎与温度无关的迁移率.

2

3.2.系统级分析

Cu金属薄膜在PVD沉积过程中会形成晶界缺陷. 在后续的等离子体高温工艺中, 随着应力释放再结晶, Cu表面会产生hillocks. 玻璃基板边缘的GOA电路中, M2 TFT栅极Cu表面的hillocks凸起最为严重, 栅极Cu: SiNx/SiO2界面的Cu离子最容易向SiNx/SiO2层扩散, 导致GOA区M2 TFT容易出现ESD失效.影响玻璃基板周边M2 TFT栅极Cu表面的hillocks凸起, 主要有两个因素, 包括GOA区与显示区金属层密度比差异大导致的周边金属层平坦度低, 以及玻璃基板周边Cu金属膜厚和SiNx/SiO2膜厚的均匀性差导致的栅极Cu:SiNx/SiO2性质稳定性低.

以3840×2160分辨率的 55寸IGZO TFT背板为例, GOA区域对应栅极金属层和源漏极金属层的Cu金属覆盖密度分别达到54%和68%, 是显示区(active area, AA)的4.42倍和4.48倍. GOA区与AA区的Cu金属覆盖密度差值太大, GOA区的Cu金属层平坦性较差, 导致Cu表面hillocks凸起更严重.

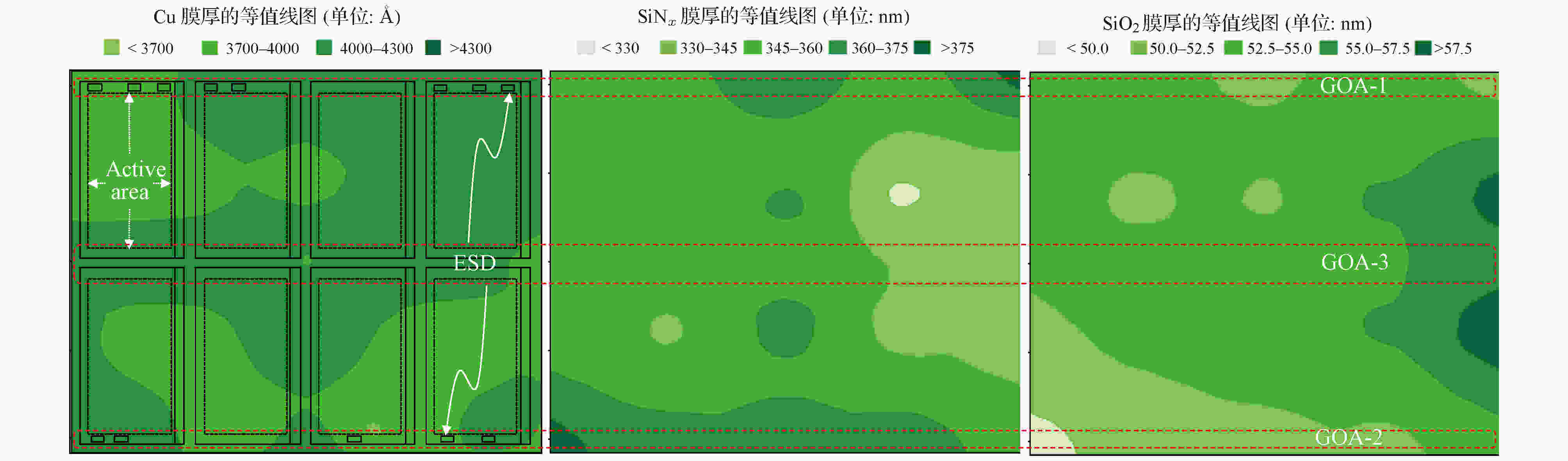

如图6所示, 玻璃基板周边的GOA电路(GOA-1和GOA-2)中, Cu金属、SiNx薄膜、SiO2薄膜的厚度起伏明显, 均匀性较差. 而玻璃基板中央的GOA电路(GOA-3)中, 三层薄膜厚度均匀性较好. 所以, 位于玻璃基板边缘的GOA电路中, Cu表面的hillocks凸起较严重, 栅极绝缘层的耐压差异较大, ESD失效风险较高.

图 6 Cu:SiNx/SiO2三层薄膜的厚度等值线分布

图 6 Cu:SiNx/SiO2三层薄膜的厚度等值线分布Figure6. Thickness contour distribution of Cu: SiNx/SiO2 three films.

根据以上的ESD失效机理, 为了提高GOA电路ESD鲁棒性, 工艺上可以提高IGZO TFT背板的Cu金属表面平坦性、Cu: SiNx/SiO2界面结合的紧密性、栅极绝缘层SiNx/SiO2的厚度均匀性, 设计上可以分解大面积的栅极Cu金属块.

如表1所示, 把原来一分为二的M2 TFT, 分解为6个子TFT并联和8个子TFT并联的结构. 一方面, 降低了栅极和源漏极的金属层密度, 降低同一个TFT内栅极Cu金属层和SiNx/SiO2栅极绝缘层厚度的起伏程度; 另一方面, 提高了M2 TFT失效区域的可切割修复能力.

| 结构 | 2个子TFT | 6个子TFT | 8个子TFT |

| 版图 |  |  |  |

| 版图空间 | 274.5 μm × 259.2 μm | 274.5 μm × 300.2 μm | 274.5 μm × 351.2 μm |

| 扫描线面积 | 53158.8 | 59647.3 | 65519.6 |

| 数据线面积 | 43155.8 | 46190.2 | 49248.2 |

| 扫描线密度 | 74.71% | 72.4% | 68% |

| 数据线密度 | 60.7% | 56.1% | 51.1% |

表1GOA区M2 TFT不同设计方案比较

Table1.Comparison of different design schemes of M2 TFT in GOA.