全文HTML

--> --> -->随着晶体管的特征尺寸越来越接近其物理极限, 沟道内的杂质数量及其随机分布对器件的电学性能影响越来越显著[16]. Colinge研究组[17]通过三维模拟的方式研究硅纳米线晶体管中离散杂质对量子输运特征的影响, 表明位于器件沟道中间的杂质原子对器件亚阈值特性的影响最大; 而当电压值大于阈值电压时, 距离源端更近的杂质原子对器件特性表现出更大的影响. 当掺杂浓度很高的时候, 电子的平均自由程比相邻杂质间的距离大, 因此, 杂质间的相互作用将更加显著. Ueda等[18]通过研究无结硅纳米线晶体管在高掺杂浓度下的迁移率变化, 表明当掺杂浓度达到1019 cm–3时, 由于电离杂质电势被载流子屏蔽, 随着掺杂浓度的增大, 迁移率也增大.

在传统半导体器件中, 杂质一般是用来提供载流子, 掺杂的类型和浓度直接影响着器件的性能和参数. 而在有限的局域纳米空间中, 电离杂质能诱导形成量子点, 为电荷输运提供两个分立的杂质能级, 载流子隧穿通过量子点可以展现出丰富的量子效应[19-21]. 杂质原子晶体管就是一种利用电离杂质诱导形成的量子点进行工作的纳米结构器件. 其中, 单杂质原子晶体管不仅能缩小到原子级尺度, 而且具有极少的载流子数目, 极有可能应用于超低功耗器件.

本文从利用杂质原子作为量子输运构件的角度出发, 结合安德森定域化理论和Hubbard带模型对单个、分立和耦合杂质原子系统中的量子输运特性进行了详细的阐述. 杂质原子晶体管不仅与传统互补金属氧化物半导体(complementary metal oxide semiconductor, CMOS)工艺兼容, 而且在未来量子电路中具有很大的应用可能性. 然而, 由于杂质原子的基态能级较浅, 难以将量子效应拓展到室温. 因此, 研究提升杂质原子晶体管工作温度的方法对量子计算电路开发具有重要的指导意义.

2

2.1.单杂质原子形成单量子点

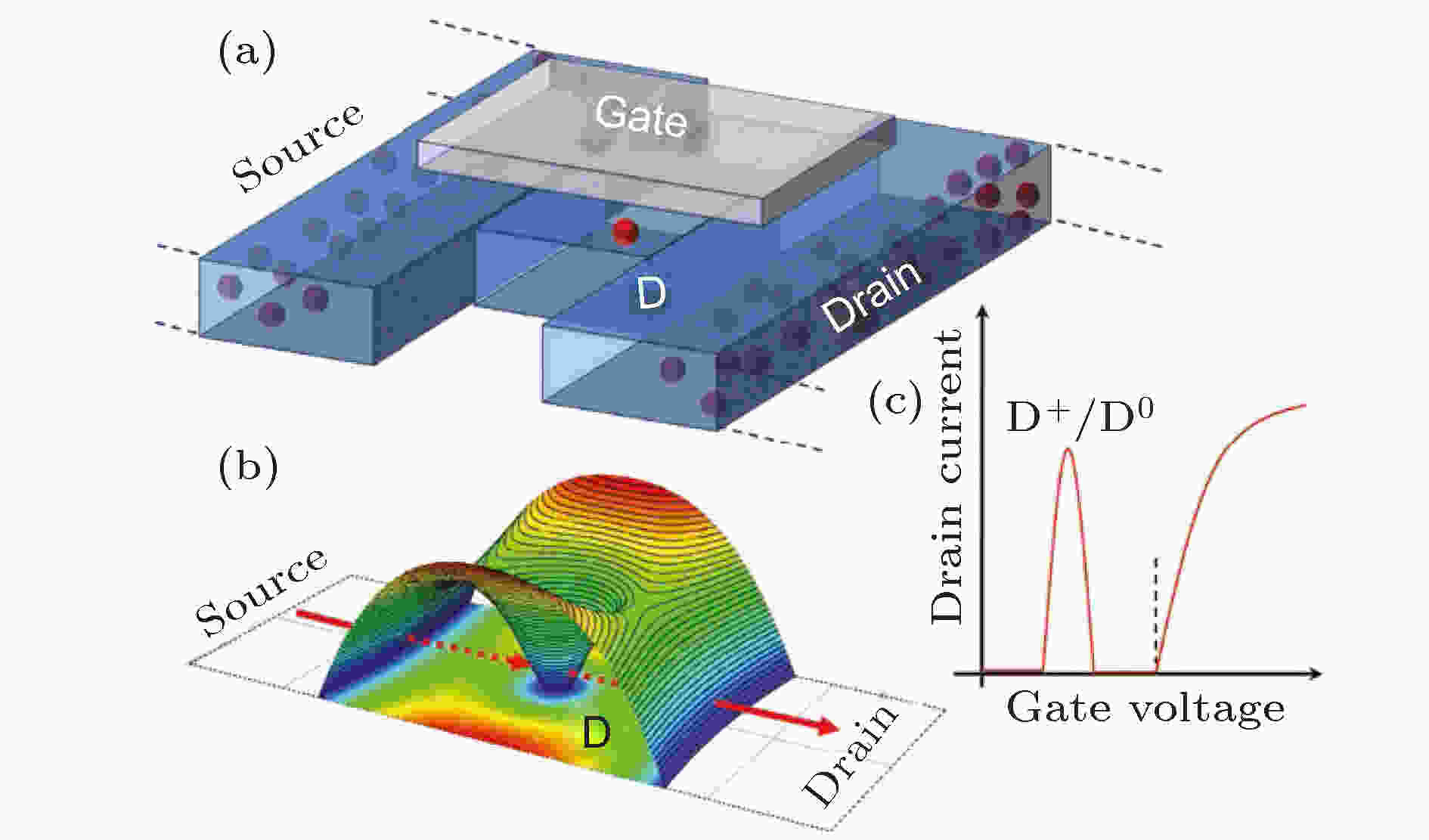

一个掺杂在硅中的施主原子有三个状态, 电离出电子形成的电离态D+, 束缚一个电子形成的中性态D0以及束缚两个电子形成的D–态. 单个电离施主原子的静电势呈现出放射状, 在三维方向上形成对称的势阱结构[19]. 因为电离态D+对应于一个空的能态, 所以在这个杂质的势阱中不存在它对应的电子态, 如图1所示. 当晶体管中的杂质原子作为一个量子点工作时, 电子可以共振隧穿通过D0和D–两个量子态. 其可以表述为: 电离施主在沟道中形成一个库仑势阱, 类似于一个天然的量子点结构. 在栅压调制下, 费米能级EF逐渐升高, 杂质原子表现为从电离态D+到中性态D0再到负电态D–的转变. 图 1 电离杂质形成的势阱结构[19]

图 1 电离杂质形成的势阱结构[19]Figure1. Confinement potential induced by ionizing impurity[19].

2

2.2.依赖单杂质量子点的输运特性

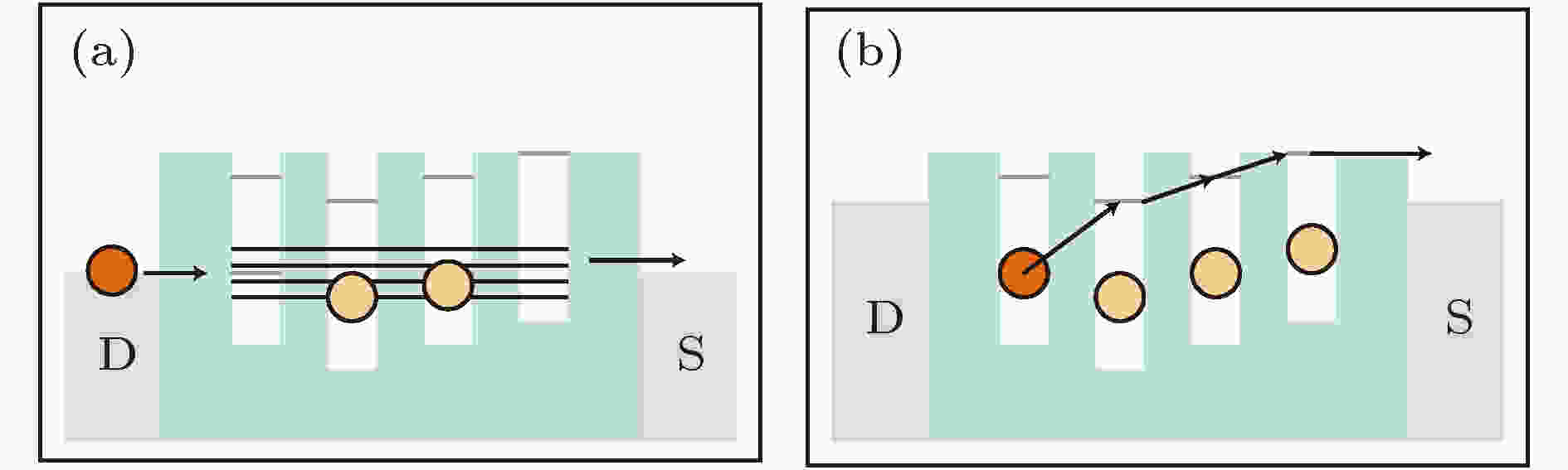

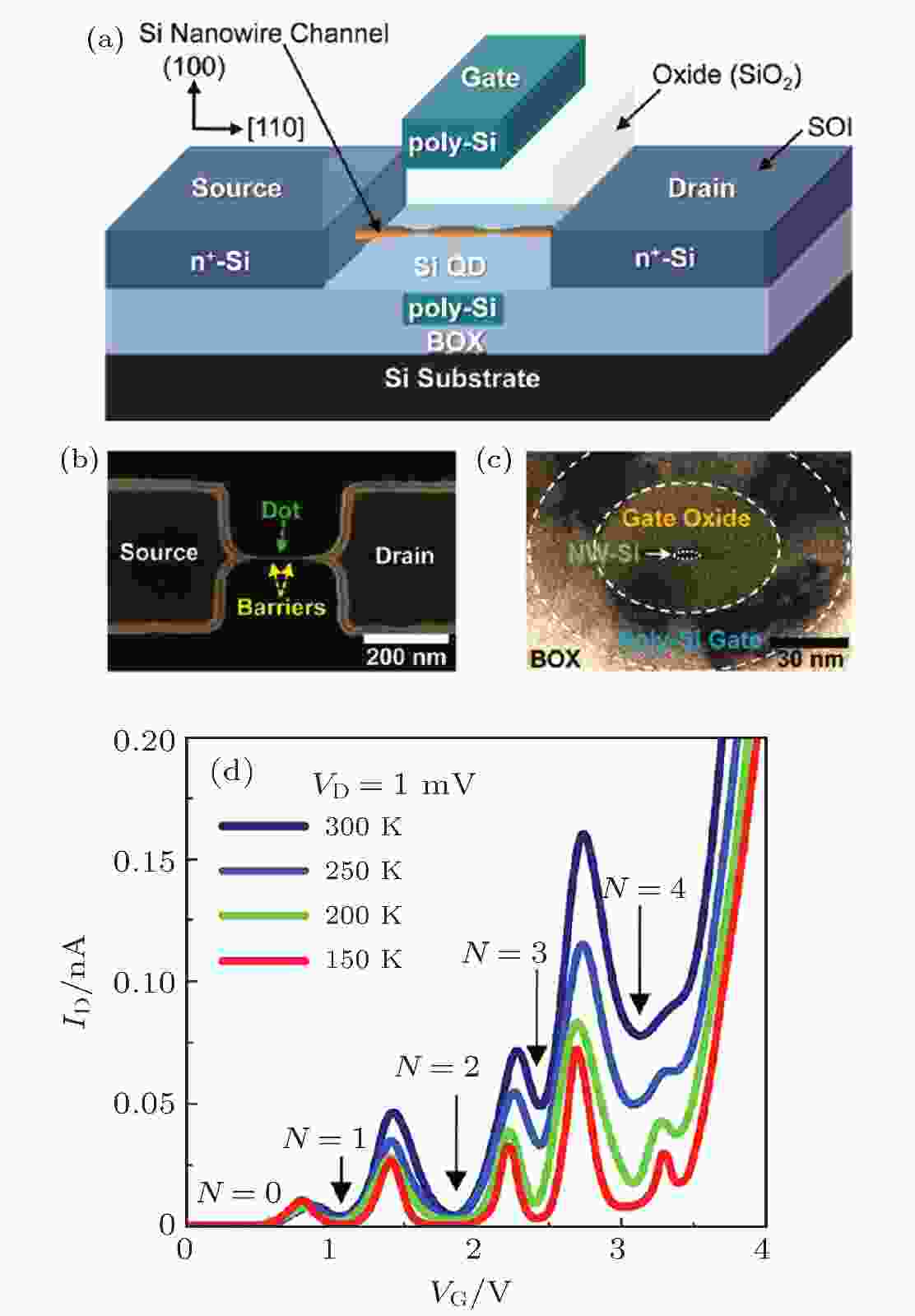

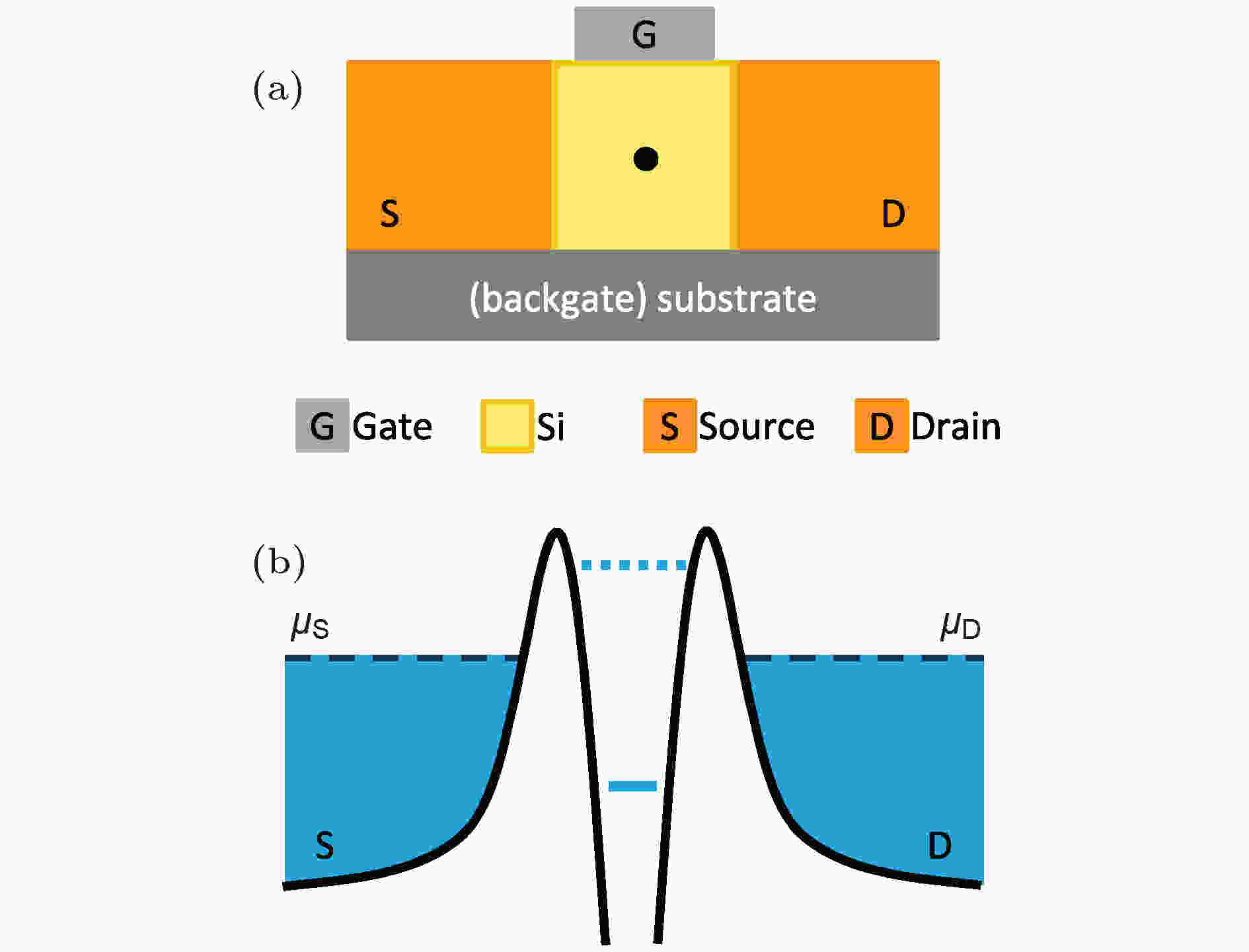

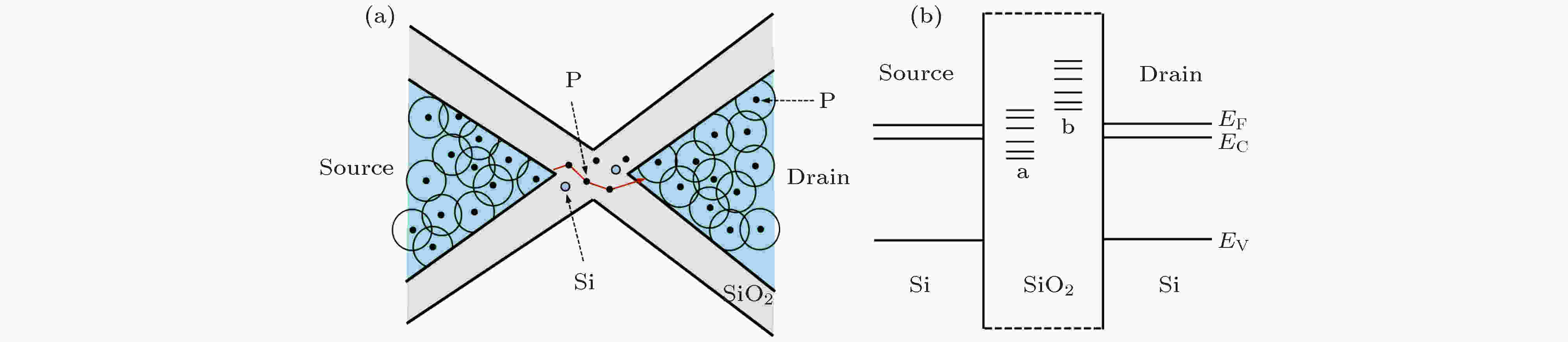

图2为理想单杂质晶体管的基本结构和工作原理图[25], 源区和漏区n型掺杂, 硅纳米线沟道连接源区和漏区, 且沟道中只有一个施主原子. 施主原子产生电离时, 可以认为沟道区中的电子被耗尽. 当栅极电压正向移动时, 施主的基态能级将逐渐对准源漏端的费米能级, 电子通过隧穿在源端和漏端输运. 在低温下, 载流子的热激活受到抑制, 在转移特性曲线中可以观测到一个电流峰. 这种电子输运机理与单电子晶体管中的库仑阻塞效应十分相似. 图 2 理想单杂质晶体管的基本结构和工作原理图 (a)单杂质晶体管结构示意图; (b)施主原子调制源端到漏端的单电子隧穿; (c)低温下单杂质晶体管的转移特性曲线[25]

图 2 理想单杂质晶体管的基本结构和工作原理图 (a)单杂质晶体管结构示意图; (b)施主原子调制源端到漏端的单电子隧穿; (c)低温下单杂质晶体管的转移特性曲线[25]Figure2. Structure and schematic diagram of the ideal single-dopant transistor: (a) Schematic illustration of single-dopant transistor; (b) donor mediates single-electron tunneling from source to drain; (c) transfer characteristics for single-dopant transistor in the low temperature[25].

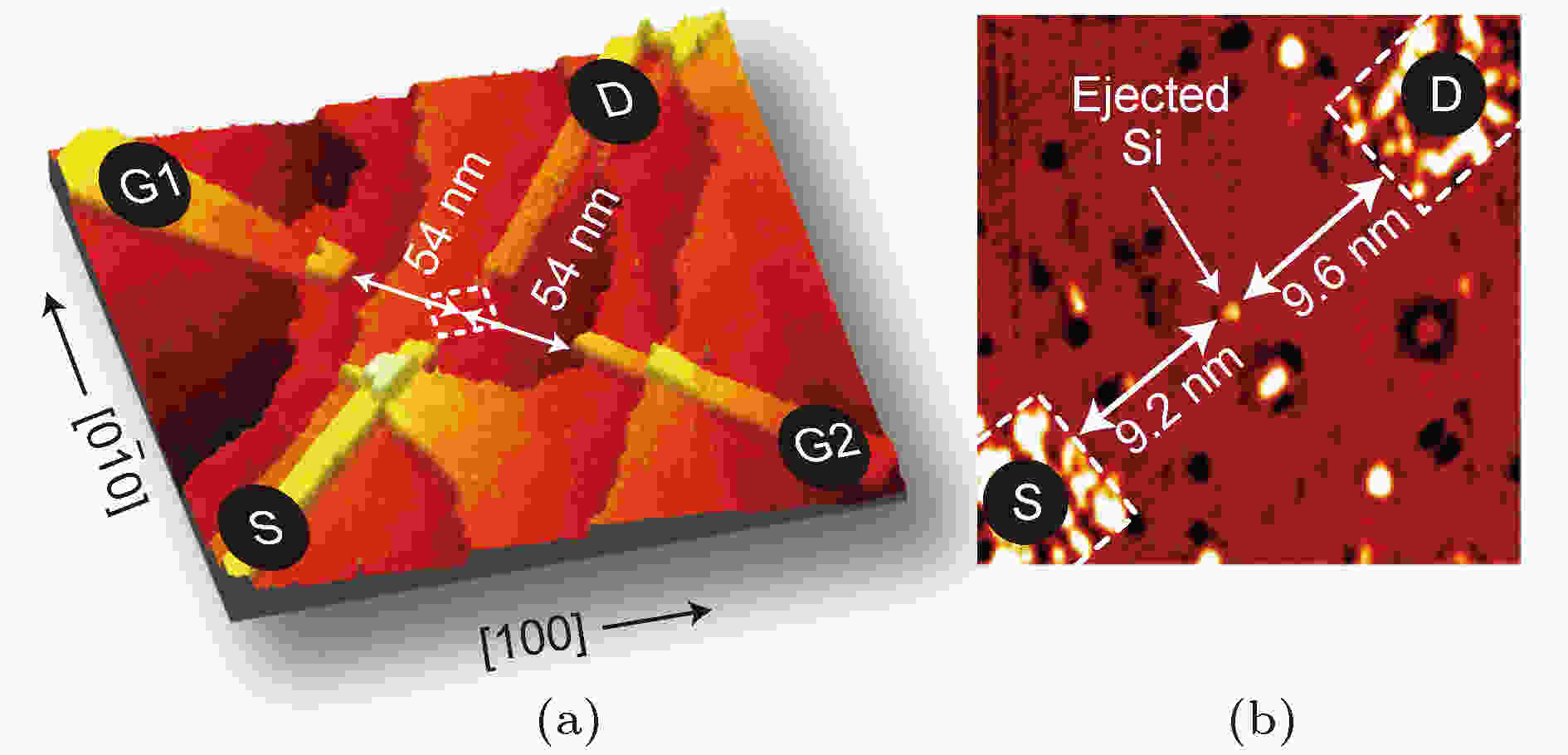

随着半导体技术的不断发展, 扫描隧道显微镜技术(scanning tunneling microscope, STM)的出现为研究杂质原子晶体管提供了更为精确的方法, 其优点在于能够在原子尺度分辨率上进行精确定位. 在硅器件中精确放置的单个杂质原子具有很长的自旋相干和自旋弛豫时间[26, 27], 这种硅基器件可能在固态量子计算体系中具有很大的应用前景. 澳大利亚新南威尔士大学Fuechsle研究组[28]利用STM在氢钝化的硅表面制备出单原子晶体管, 其能在精确度高达 ± 1个原子间距内定位单个磷原子, 器件结构如图3所示. 在液氦温度下, 观测到单个磷原子在D+(电离态)、D0(中性态)以及D–(负电态)之间的转变, 证明了在硅衬底上操控单个杂质原子的可行性. 单原子晶体管依赖单个杂质原子作为量子点工作, 代表了固态器件的最终尺度极限.

图 3 (a)单原子晶体管器件结构 STM 图像; (b)局部放大图[28]

图 3 (a)单原子晶体管器件结构 STM 图像; (b)局部放大图[28]Figure3. (a) Perspective STM image of single-atom transistor; (b) close-up of the inner device area[28].

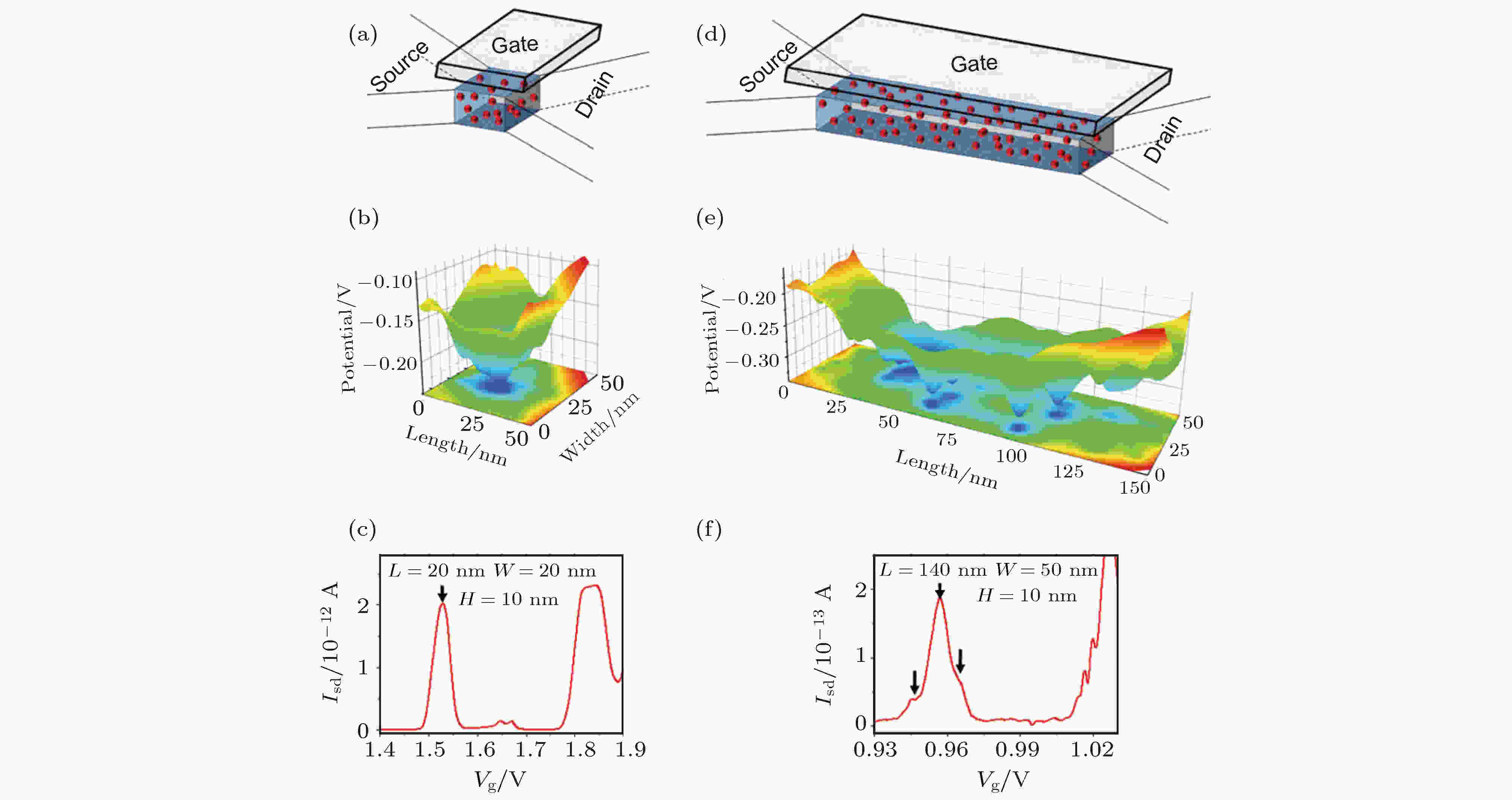

虽然STM技术能够精确定位单个杂质原子, 但是其工艺过程相对复杂, 并不适合大规模的生产. 基于CMOS工艺中的传统掺杂技术, Tabe研究组[29]制备出不同沟道长度(20—150 nm)的器件, 如图4(a)和(d)所示. 通过开尔文力显微镜(Kelvin force microscope, KFM)测量其沟道电势分布, 发现纳米线器件沟道中心区域由于周围杂质的累积效应存在最低的电势, 图4(b), (e)为模拟的沟道电势分布图. 在17 K下, 通过分别测量栅长为20 nm和140 nm的器件中源漏电流(Isd)相对于栅压(Vg)的特性曲线, 来研究不同沟道长度的磷掺杂纳米线器件中的单电子输运特性, 发现在Isd -Vg特性曲线中存在非周期性的电流振荡, 这是因为单电子隧穿通过电离杂质诱导形成的量子点, 如图4(c)和(f). 短沟道器件中的电流峰比较平滑, 而在长沟道器件中则存在分裂的电流子峰. 这说明在长沟道中存在多个量子点形成的阵列, 分裂的电流峰子数目对应于量子点的个数.

图 4 (a)短沟道器件示意图; (b)短沟道器件电势分布图; (c)短沟道器件Isd -Vg特性曲线(Vsd = 5 mV); (d)长沟道器件示意图; (e)长沟道器件电势分布图; (f)长沟道器件Isd -Vg特性曲线(Vsd = 5 mV)[29]

图 4 (a)短沟道器件示意图; (b)短沟道器件电势分布图; (c)短沟道器件Isd -Vg特性曲线(Vsd = 5 mV); (d)长沟道器件示意图; (e)长沟道器件电势分布图; (f)长沟道器件Isd -Vg特性曲线(Vsd = 5 mV)[29]Figure4. (a) Schematic channel structure; (b) example of simulated potential profile; (c) example of dc Isd -Vg characteristics (Vsd = 5 mV) for a short-channel FET; (d) schematic channel structure; (e) example of simulated potential profile; (f) example of dc Isd -Vg chara-cteristics (Vsd = 5 mV) for a long-channel FET[29].

通过实验统计不同沟道长度(20—150 nm)器件的Isd -Vg特性曲线中第一个电流峰包含的子峰个数, 发现子峰个数整体表现出随着沟道长度增加而增加的趋势, 如图5(a)所示. 接着模拟统计不同沟道长度(20—150 nm)器件中量子点的个数, 发现和实验统计结果相吻合, 如图5(b)所示. 这不仅说明电离杂质诱导形成的量子点个数可以由沟道长度控制, 而且在较低的电势窗口下, 一个量子点中平均只含有一个杂质原子, 如图5(c)所示. 这种通过传统掺杂技术制备的纳米结构晶体管不仅在实验上证明了即使在随机掺杂的环境中, 单电子也能通过单个或者几个杂质原子诱导形成的量子点进行隧穿输运. 而且当器件沟道长度足够短时, 沟道中很可能只存在一个杂质原子, 这为运用传统掺杂技术制备单杂质晶体管提供了思路.

图 5 (a)不同沟道长度下分裂峰个数的实验统计; (b)不同沟道长度下量子点个数的模拟统计; (c) 50 nm × 50 nm纳米结构中一个量子点中的平均杂质数目[29]

图 5 (a)不同沟道长度下分裂峰个数的实验统计; (b)不同沟道长度下量子点个数的模拟统计; (c) 50 nm × 50 nm纳米结构中一个量子点中的平均杂质数目[29]Figure5. (a) Statistical results of the number of subpeaks; (b) statistical results of the number of dopant-induced QDs; (c) average number of dopants embedded in one QD for 50 nm × 50 nm nanostructures[29].

2

3.1.分立杂质原子系统中的量子输运特性

采用传统的掺杂技术, 掺杂原子在沟道中满足泊松分布. 以磷原子为例, 当掺杂浓度较小时(一般约为1 × 1018 cm–3), 磷原子之间的平均距离(大约10 nm)大于2rB (rB为磷原子在硅中的玻尔半径). 此时可以认为磷原子之间相互隔离, 每个杂质原子局部调制沟道电势. Anwar等[30]通过在低温(T = 13 K)下用开尔文探针力显微镜 (Kelvin probe force microscope, KPFM)测量器件沟道电势分布, 发现在负栅压下(VBG = -3 V)分立的杂质原子形成独立的势阱结构, 如图6(a)所示. 当VBG正向移动, 势阱逐渐消失, 并且在VBG = 0 V时不再具有明显的电势分布特征. 结合图6(b), 这种情况可以解释为每个分立的电离施主原子自身作为量子点工作, 随着栅极电压增大, 这些分立的施主原子将连续俘获电子. 图 6 (a)低温下随栅压变化的电势分布图; (b)分立的磷施主原子在不同栅压下逐个电中性化[30]

图 6 (a)低温下随栅压变化的电势分布图; (b)分立的磷施主原子在不同栅压下逐个电中性化[30]Figure6. (a) Sequence of electronic potential landscapes as a function of applied VBG; (b) a simple illustration of one-by-one neutralization of individual P-donors at different VBG[30].

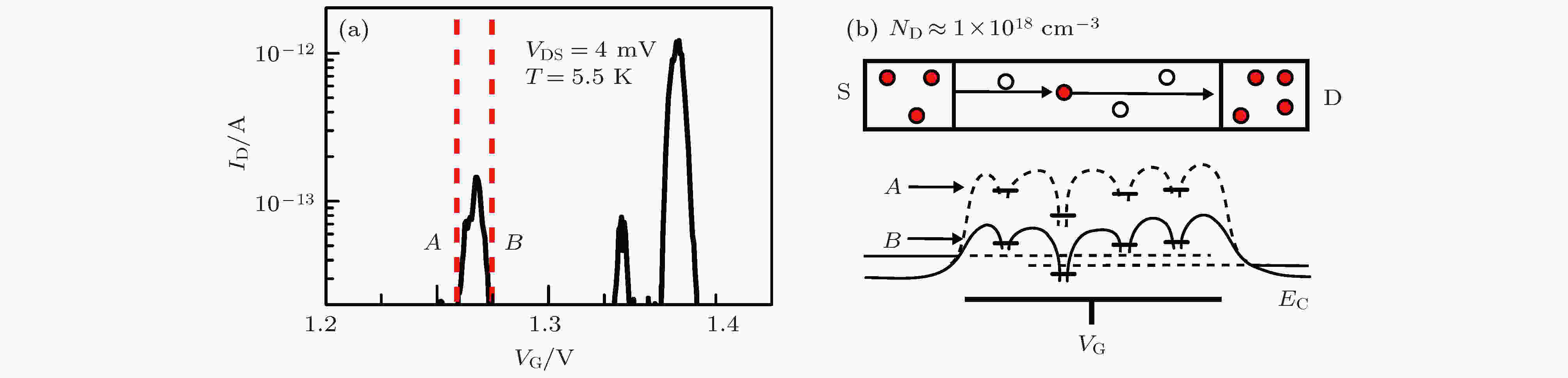

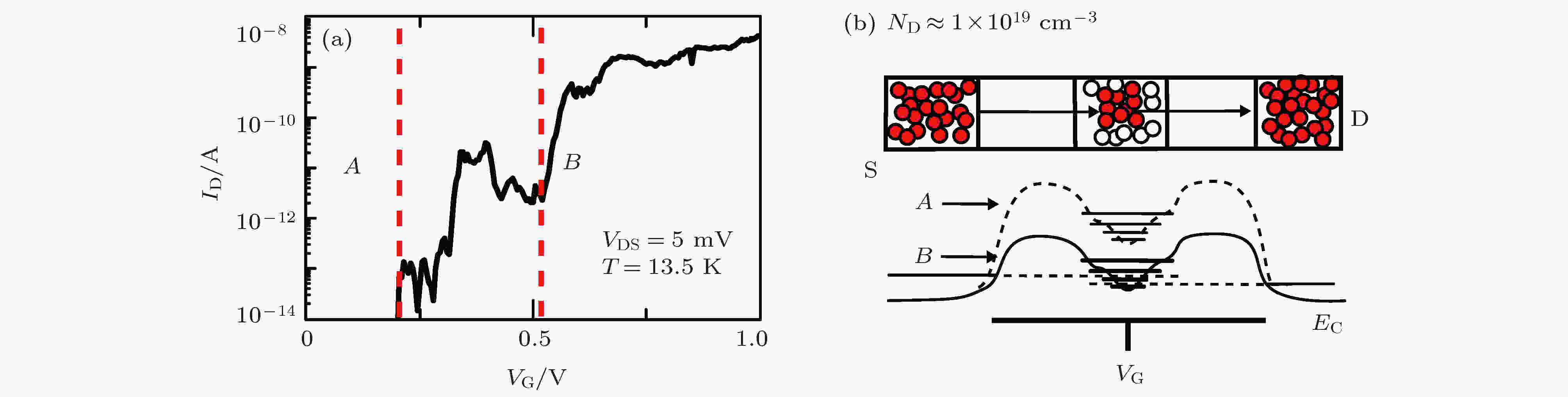

在低掺杂浓度下(1 × 1018 cm–3左右), 杂质原子的平均间距较大, 从统计分布的角度上来说不太可能形成杂质原子团簇, 单个分立的杂质原子自身就能够作为一个量子点工作. 对于长沟道器件而言, 沟道中含有多个这样分立的杂质原子, 电子在源区和漏区之间的输运只能依赖隧穿通过电容耦合的杂质原子阵列. 当器件沟道足够短的时候, 沟道中可能只含有一个杂质原子, 此时电子的输运特性就是由单个电离杂质诱导形成的量子点进行调控. 运用热扩散掺杂技术对SOI-FETs进行磷原子掺杂, 通过在低温下测量ID-VG特性曲线, 可以研究电子在分立杂质原子系统中的输运特征[31]. 如图7(a)所示, ID-VG特性曲线中的电流峰表现出非周期性, 且每个电流峰的强度也不相同. 由此说明, 这些电流峰对应于不同的量子点, 进而可以得出, 每个量子点是由不同的分立杂质原子形成. 图7(b)为掺杂磷原子在沟道中可能形成的分布情况, 以及其对应的沟道电势分布示意图. 从图7(b)中可以看出, 每个分立的杂质原子在沟道中形成一个独立的库仑势阱, 量子点之间相互隔离. 当施加特定的栅压VG, 具有最深电势的量子点的基态能级与源漏端的费米能级(EF)对准, 电子隧穿通过这个量子点, 在ID-VG特性曲线中出现第一个电流峰. 当栅压VG小于电流峰处的电压值(对应于图7中的A区), 沟道中的电子是耗尽的; 当栅压VG大于电流峰处的电压值(对应于图7中的B区), 电子被这个量子点俘获. 继续升高栅压VG, 其他量子点的基态能级逐渐对准源漏端的费米能级EF, ID-VG特性曲线中将出现新的电流峰.

图 7 (a) SOI-FET低温下的ID-VG特性曲线; (b)沟道中可能的杂质原子分布以及沟道电势分布示意图[31]

图 7 (a) SOI-FET低温下的ID-VG特性曲线; (b)沟道中可能的杂质原子分布以及沟道电势分布示意图[31]Figure7. (a) Low-temperature source-drain current (ID) vs. gate voltage (VG) characteristics; (b) one possible P-donors’ distribution and schematic channel potential profiles[31].

2

3.2.与温度相关的电子跃迁输运

在分立的杂质原子系统中, 沟道中杂质的间距较大, 量子态没有发生交叠. 随机分布的杂质可以认为处于无序的状态, 载流子可以通过跃迁在分立的杂质原子系统中进行输运. 在非零温度下, 电子可以从一个杂质定域态跃迁到另一个杂质定域态, 这种跃迁输运方式受温度的影响.安德森提出在无序系统中电子运动定域化的概念, 称为安德森定域化[32, 33], 无序系统电子能态密度示意图如图8所示. 在带顶和带底区域出现带尾, 在带尾区域中的电子态为定域态, 带中间区域的电子态为扩展态, 它们之间的分界Ec和

图 8 无序系统中的带尾定域态[32]

图 8 无序系统中的带尾定域态[32]Figure8. Tailed localized states in disordered systems[32].

分立的杂质原子系统被认为是无序的, 可以运用安德森定域化来解释分立杂质原子系统中电子输运行为随温度的变化. 图9(a)和(b)分别为弱杂质补偿和强杂质补偿情况下n型半导体的能带和定域态空间分布示意图. 图中的短划线代表施主原子的能级, 圆圈代表局域在能级上的电子, Ec为导带底, E0是单个分立施主原子的电离能,

图 9 弱杂质补偿和强杂质补偿情况下的能带和定域态空间分布示意图 (a)弱杂质补偿; (b)强杂质补偿[34]

图 9 弱杂质补偿和强杂质补偿情况下的能带和定域态空间分布示意图 (a)弱杂质补偿; (b)强杂质补偿[34]Figure9. Schematic representation of the energy and space distribution of the localized states in the case of weak (a) and strong (b) compensation[34].

杂质补偿是电子从一个被占据的施主原子上跃迁到一个空的施主能级上的一项必要条件, 因为在T = 0时, 空的能态需要由杂质补偿提供. 从图9可以看出, 无论在强或弱杂质补偿的情况下, 费米能级都有可能出现在带尾区域, 即处于定域态范围中. 在分立的杂质原子系统中可以认为单个分立的杂质原子是一个定域中心, 在低温下电子被局域在杂质原子上, 随着温度的升高, 电子可以借助声子的作用, 实现在不同定域态之间的转移, 即电子在不同杂质原子间进行跃迁输运. 此时电导率随温度升高表现出热激活的性质, 电阻温度系数为负值, 称这种情况为费米玻璃(Fermi glass)[35].

电子的跃迁方式分为可变程跃迁和最近邻跃迁[36], 在极低的温度下, 电子获得的热激活能很小, 不足以跨越势垒进行输运, 电子趋向于在能量相近的能级之间做变程跃迁. 但是定域态的能量无规则地分布在相当宽的能量范围内, 相邻的定域中心之间往往有较大的能量差, 只有在更远的距离才可能找到能量相近的定域中心, 对应于图10(a). 根据文献[37, 38], 可变程跃迁的跃迁距离r和跃迁概率P满足如下关系式:

图 10 电子的跃迁方式 (a)可变程跃迁; (b)最近邻跃迁[38]

图 10 电子的跃迁方式 (a)可变程跃迁; (b)最近邻跃迁[38]Figure10. Hopping modes of the electron: (a) Variable range hopping; (b) nearest neighbor hopping[38].

2

4.1.耦合杂质原子系统中的量子输运特性

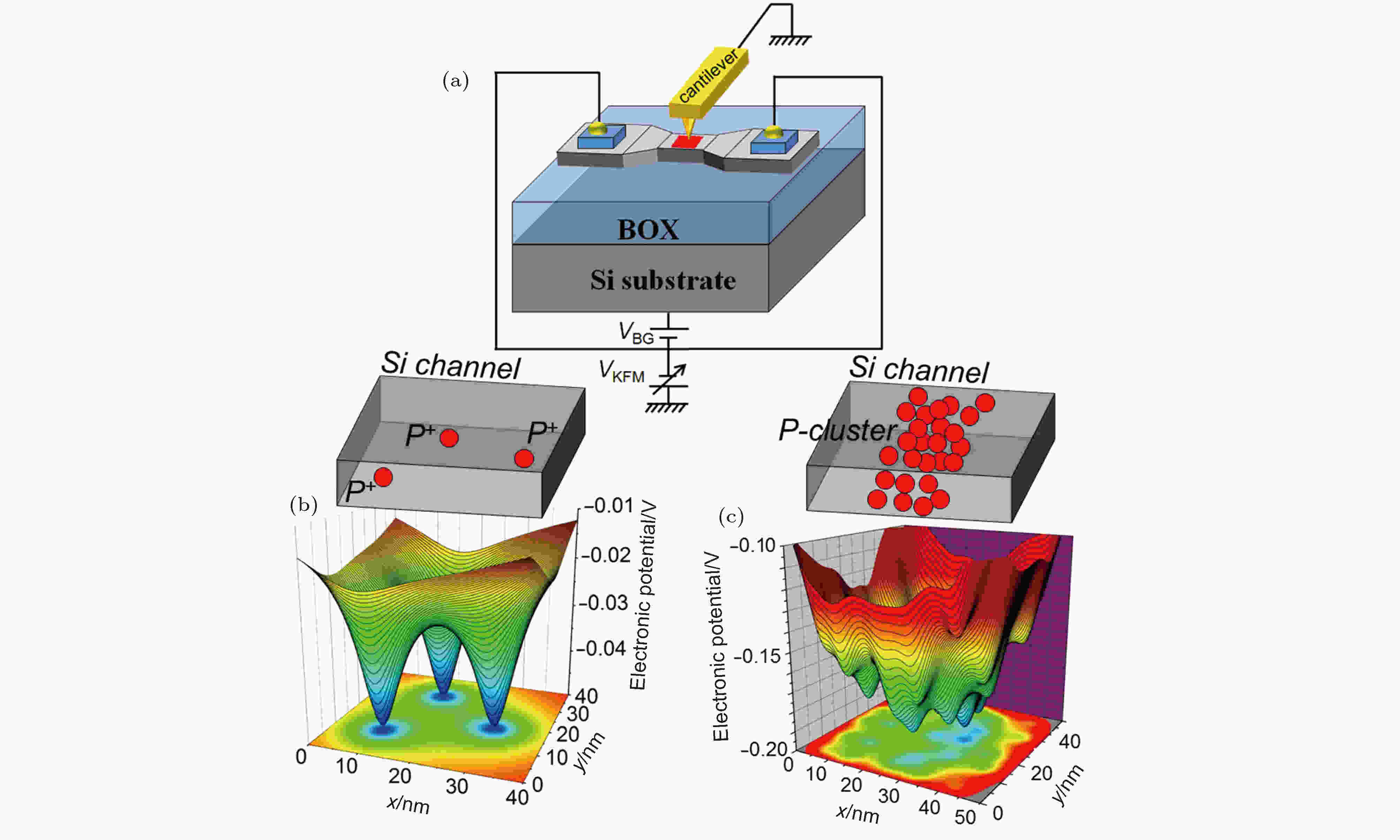

当器件沟道中的掺杂浓度逐渐提高到金属-绝缘体转变(metal-insulator transition, MIT)浓度以上时, 杂质原子间距逐渐减小, 它们之间存在着强烈的相互作用, 电子波函数发生交叠. 这里考虑沟道磷原子掺杂浓度在1 × 1019 cm– 3左右时的情形[39], 可以认为磷原子之间的距离小于2rB (rB为磷原子在硅中的玻尔半径). 如图11所示, 运用开尔文探针力显微镜能分别测量出低掺杂浓度和高掺杂浓度下, 施主原子在器件沟道中形成的电势分布情况. 对比得出, 随着掺杂浓度的升高, 杂质原子之间相互靠近, 沟道中的电势不再是由单个分立的电离杂质局部调制, 而是周围所有杂质原子电势的叠加. 在这样高的掺杂浓度下, 相邻杂质原子间发生强烈的耦合, 含有多个杂质原子的原子团簇形成量子点. 同时, 需要采用选择性掺杂技术[40]将这个由原子团簇形成的量子点与源漏区隔离, 以保证沟道的耗尽. 图 11 (a)开尔文探针力显微镜测量SOI-FETs的结构示意图; (b), (c)不同掺杂浓度下, 施主原子形成的电势分布图[39]

图 11 (a)开尔文探针力显微镜测量SOI-FETs的结构示意图; (b), (c)不同掺杂浓度下, 施主原子形成的电势分布图[39]Figure11. (a) Schematic of KPFM measurement setup; (b), (c) potential distribution of donor atoms at different doping concentrations[39]

电子在多杂质原子耦合系统中的输运特性与在分立杂质原子系统中的情形不同[31]. 如图12(a)所示, 随着栅极电压VG增大, 电子通过量子点的隧穿输运不再是独立的电流峰, 而是表现为多个电流峰包络. 这表明含有多个杂质的量子点中存在更为复杂的能态, 磷原子通过强烈的相互作用形成一个类分子的系统, 引起束缚和抗束缚态[40]. 当栅压VG大于第一个电流峰包络处的电压值(图12中B区), 对应于一个电子被这个量子点俘获, 后面出现的电流峰包络则为另一个电子隧穿通过同一个量子点. 如图12(b)所示, 采用选择性掺杂技术对沟道区域进行局部掺杂, 沟道中的电势分布将发生改变, 杂质原子在耦合作用下形成能态更复杂的量子点.

图 12 (a) SOI-FET低温下的ID-VG特性曲线; (b)选择性掺杂沟道中可能的杂质原子分布以及沟道电势分布示意图[31]

图 12 (a) SOI-FET低温下的ID-VG特性曲线; (b)选择性掺杂沟道中可能的杂质原子分布以及沟道电势分布示意图[31]Figure12. (a) Low-temperature source-drain current (ID) vs gate voltage (VG) characteristics; (b) a possible P-donors’ distribution and schematic channel potential profiles in the selective doping channel[31].

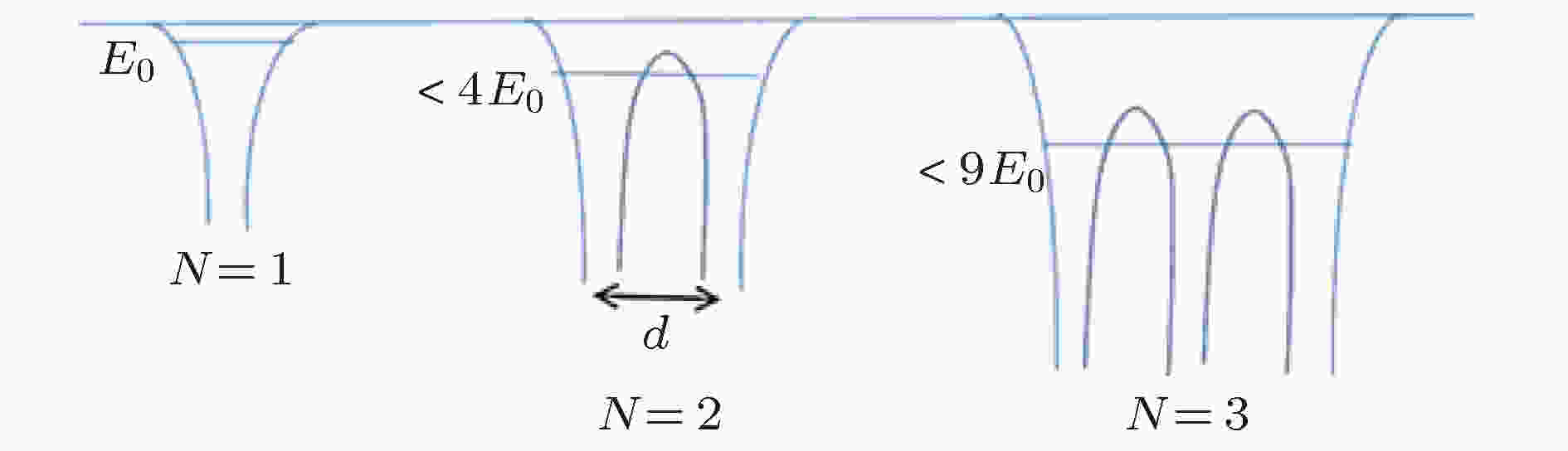

若是将耦合杂质原子系统中的每个杂质原子都看成是一个量子点, 当沟道中存在N个量子点, 量子点之间通过耦合形成一个量子点系统. 这个量子点系统中对应的能级分裂为N个, 分立的能级间距大小对应于耦合能Δ, 当量子点数目N较大时能级扩展为能带. 电子在栅压调制作用下, 首先填充基态能带中的最低能级, 系统费米势增加一个耦合能大小的能量时, 电子填充能带中的第二个能级, 在基态能带填充满之后, 电子需要一个较大的能量(U-NΔ)才能填充下一个能带, U为量子点系统的充电能. 电导峰在耦合作用下分裂为一系列的子峰, 子峰的个数对应量子点数目. 劈裂子峰对应的栅压间隔ΔVg与耦合能的关系如下[41]:

2

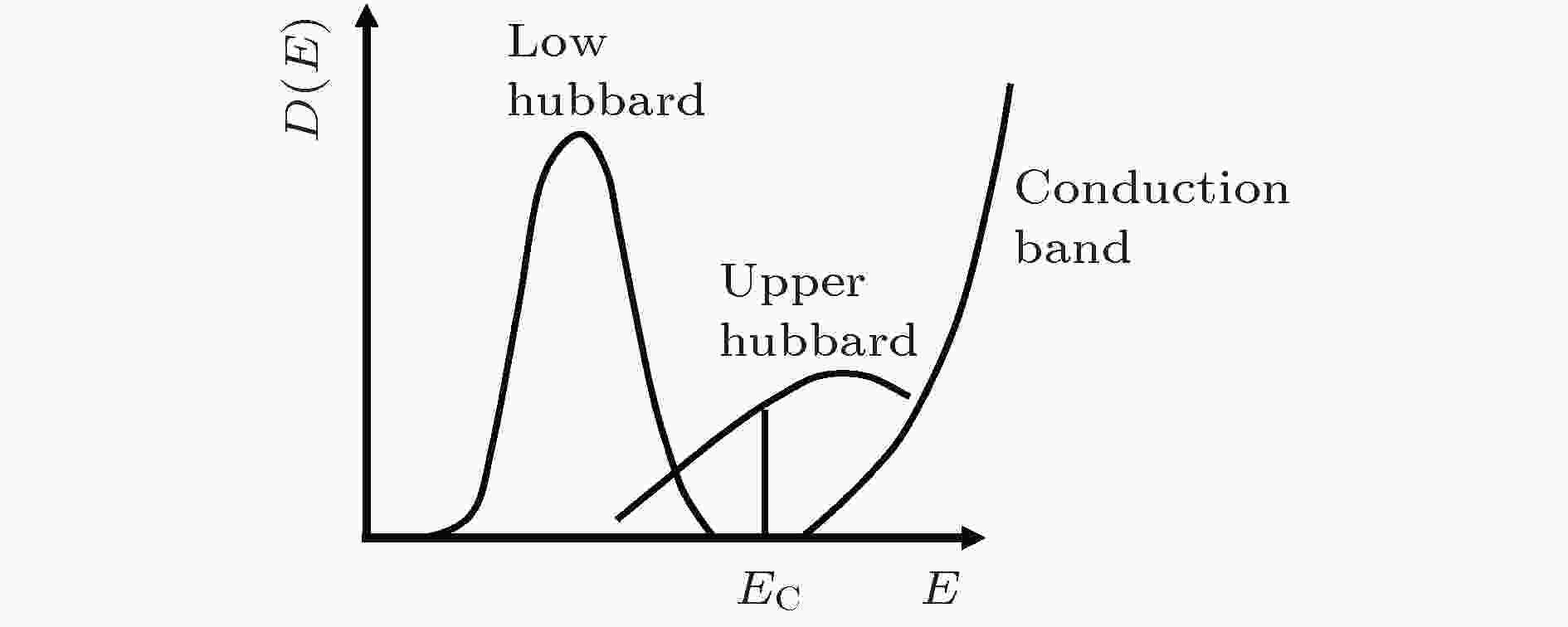

4.2.Hubbard能带输运方式

在耦合的杂质原子系统中, 当杂质原子排列相对有序时, 电子则可以通过Hubbard能带进行输运. 当每个原子的局域态上存在着两个自旋相反的电子时, 电子之间将存在库仑排斥作用, 从而电子之间具有正的相关能U (也称为Hubbard能). ε0表示第一个电子的能量, ε0 + U表示第二个电子的能量, 当N个原子相互靠近排列成晶格时, 能级展宽为能带, 分别称为下Hubbard带和上Hubbard带[43]. 图13给出了Hubbard能带模型示意图, 当相邻电子波函数重叠很小时, 能带宽度很窄, 上、下Hubbard带是分离的, 下Hubbard带是满带, 上Hubbard带是空带, 呈现绝缘体性质. 当原子逐渐靠近, 上、下Hubbard带发生交叠, 都变成部分填充的能带, 呈现金属电导的性质. 这种由上、下Hubbard带引起的金属-绝缘体转变, 称为Mott转变. 图 13 Hubbard能带模型[43]

图 13 Hubbard能带模型[43]Figure13. Hubbard band model[43].

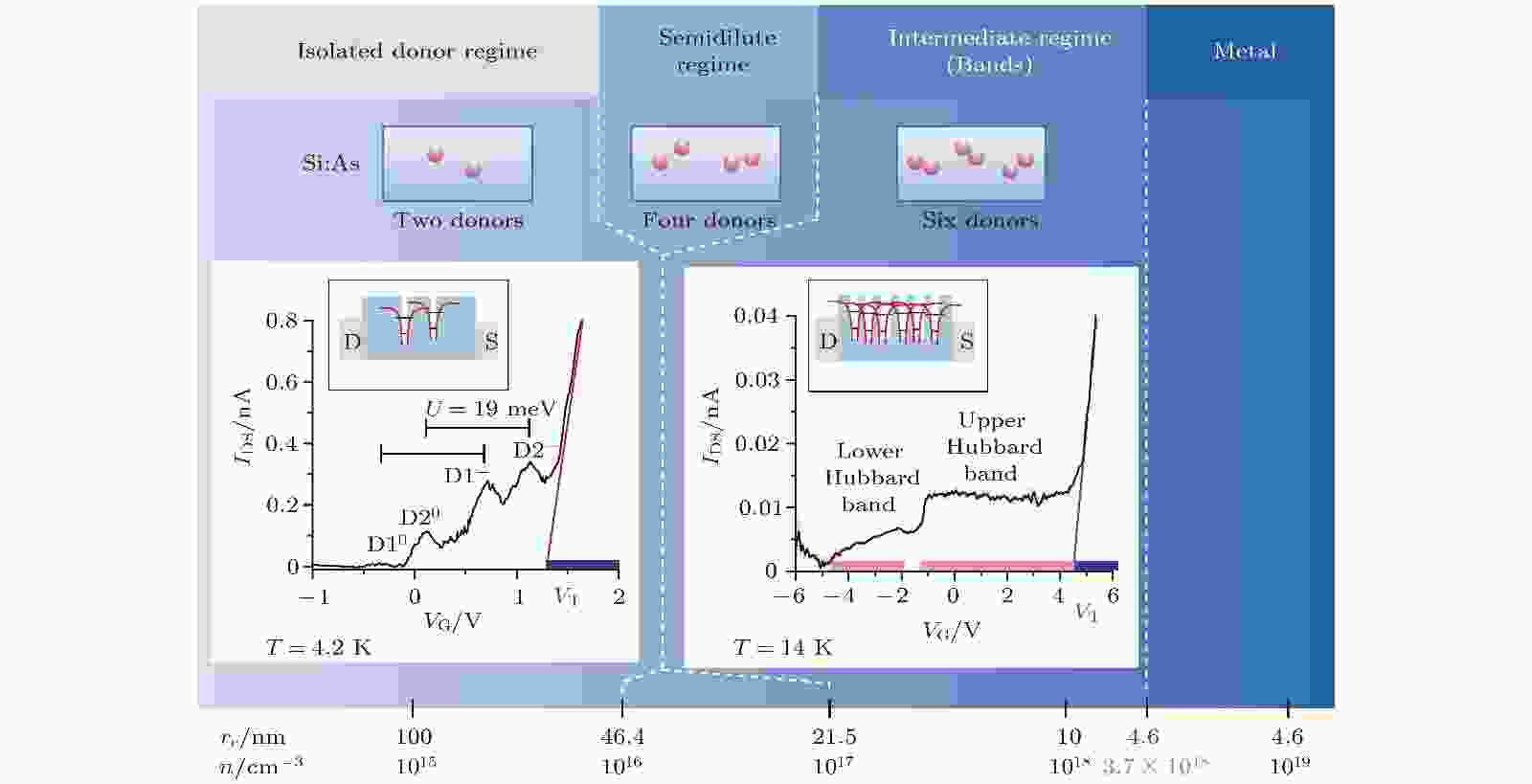

耦合杂质原子系统中的量子输运特性可以用Hubbard能带模型来解释. 前面已经提到, 单个电离施主原子中存在D0态和D–态, 在高掺杂浓度下, 杂质原子之间相互靠近, D0态和D–态分别通过耦合形成下、上Hubbard带. 在较低栅压下, 电子通过下Hubbard带输运, 随着栅极电压逐渐增大, 电子还可以通过上Hubbard带输运. 在ID-VG特性曲线中不再是单个分立的电流峰, 而是多个电流峰包络, 即电子不再是隧穿通过杂质量子点, 而是通过杂质原子耦合形成的能带进行输运. Shinada研究组[44]运用单离子注入技术在晶体管中注入2, 4, 6个砷原子, 在低温下观测到了这种电子输运方式的转变. 单离子注入技术能够精确控制掺杂原子在器件中的个数和位置, 通过控制杂质原子的间距, 可以在低温下观察到安德森-莫特转变现象.

如图14左所示, 在低温下观测到电子顺序隧穿通过两个施主原子的D0态和D–态, 表现为相互交叠的电导峰对. 峰的对数对应于施主原子的数量, 且每个施主原子D0态和D–态的能级间隔大约为19 meV. 如图14右所示, 在有6个施主原子的样品中观测到Hubbard能带的形成, 说明随着注入原子数目的增多, 单一的杂质能级逐渐扩展为杂质能带, 电子输运方式从隧穿转变为Hubbard能带输运.

图 14 不同杂质数目下的量子输运特征, 从单施主态到杂质带的安德森-莫特转变[44]

图 14 不同杂质数目下的量子输运特征, 从单施主态到杂质带的安德森-莫特转变[44]Figure14. Anderson-Mott transition probed by means of quantum transport[44].

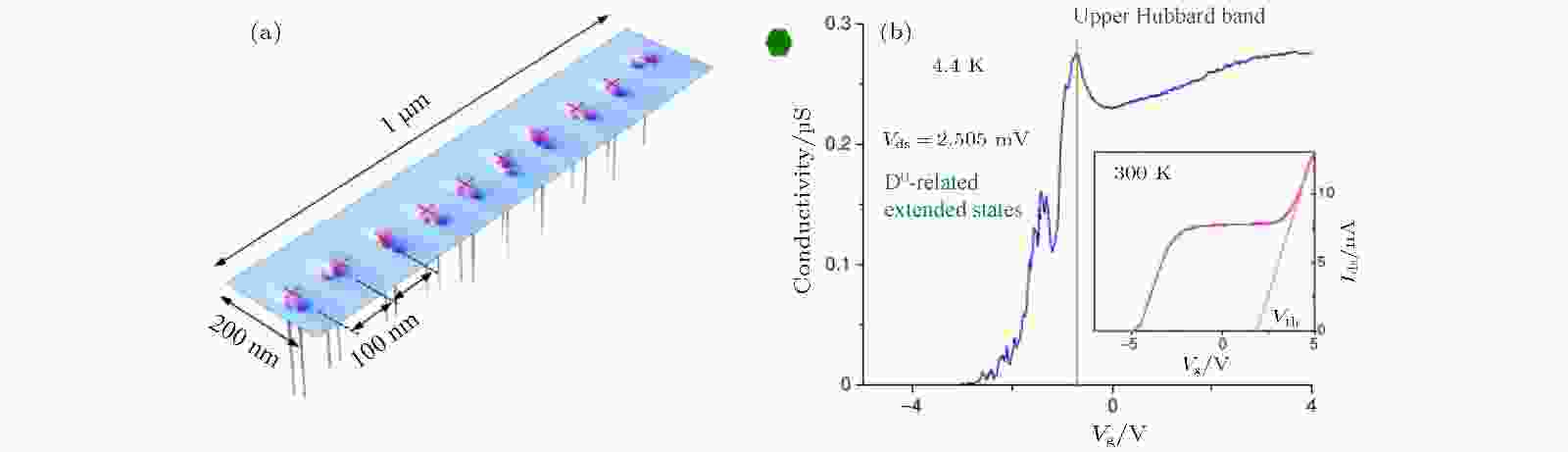

单离子注入技术相比于传统掺杂技术, 其优势是可以让杂质原子更为有序地排列. 该组通过单离子注入技术在硅晶体管沟道中形成一条大约由20个磷原子组成的

图 15 (a)沿沟道分布的20个磷施主原子中电势分布的理想示意图; (b)Vds = 2.505 mV时, 在4.4 K下测量的器件电导-栅压曲线. 插图: Vds = 2.505 mV时, 室温下提取的阈值电压[45]

图 15 (a)沿沟道分布的20个磷施主原子中电势分布的理想示意图; (b)Vds = 2.505 mV时, 在4.4 K下测量的器件电导-栅压曲线. 插图: Vds = 2.505 mV时, 室温下提取的阈值电压[45]Figure15. (a) An idealized representation of the potential distributions in the 20 phosphorous donors distributed along the channel of the sample; (b) conductance σ of the device probed at 4.4 K measured at Vds = 2.505 mV. Inlet: extraction of the threshold voltage at room temperature, at Vds = 2.505 mV[45].

如图16(a)所示, 通过测量这条单原子链器件的电导-栅压特性曲线, 发现不同温度区间下的电子输运过程对应不同的激活能. 如图16(c), (d)所示, 低温区间下, 随着温度升高, 电子从隧穿输运逐渐转变为定域态之间的热激活输运. 根据Mott理论, 还可以得出下Hubbard能带的激活能为ε3, 这个激活能相当于相邻定域中心之间的能量差. 而对于上Hubbard能带, 可以观测到可变程跃迁和最近邻跃迁间的转变, 通过拟合可以得到其对应的激活能ε2. 如图16(b)所示, 在高温区间下, 根据Anderson理论, 原子链表现为随机势能, 在费米能级附近的热辅助跃迁转变为到迁移率带边的非跃迁激活, 上Hubbard能带电子离域化且具有更高的激活能

图 16 (a)4.2—274 K温度区间下的电导-栅压曲线; (b)高温下上Hubbard带的热激活输运; (c)低温下下Hubbard带的热激活输运; (d)低温下上Hubbard带的热激活输运[45]

图 16 (a)4.2—274 K温度区间下的电导-栅压曲线; (b)高温下上Hubbard带的热激活输运; (c)低温下下Hubbard带的热激活输运; (d)低温下上Hubbard带的热激活输运[45]Figure16. (a) The conductance as a function of the gate voltage Vg from 4.2 to 274 K; (b) the thermal activation of the upper Hubbard band at high temperature; (c) the thermal activation of the lower Hubbard band at low temperature; (d) the thermal activation of the upper Hubbard band at low temperature[45].

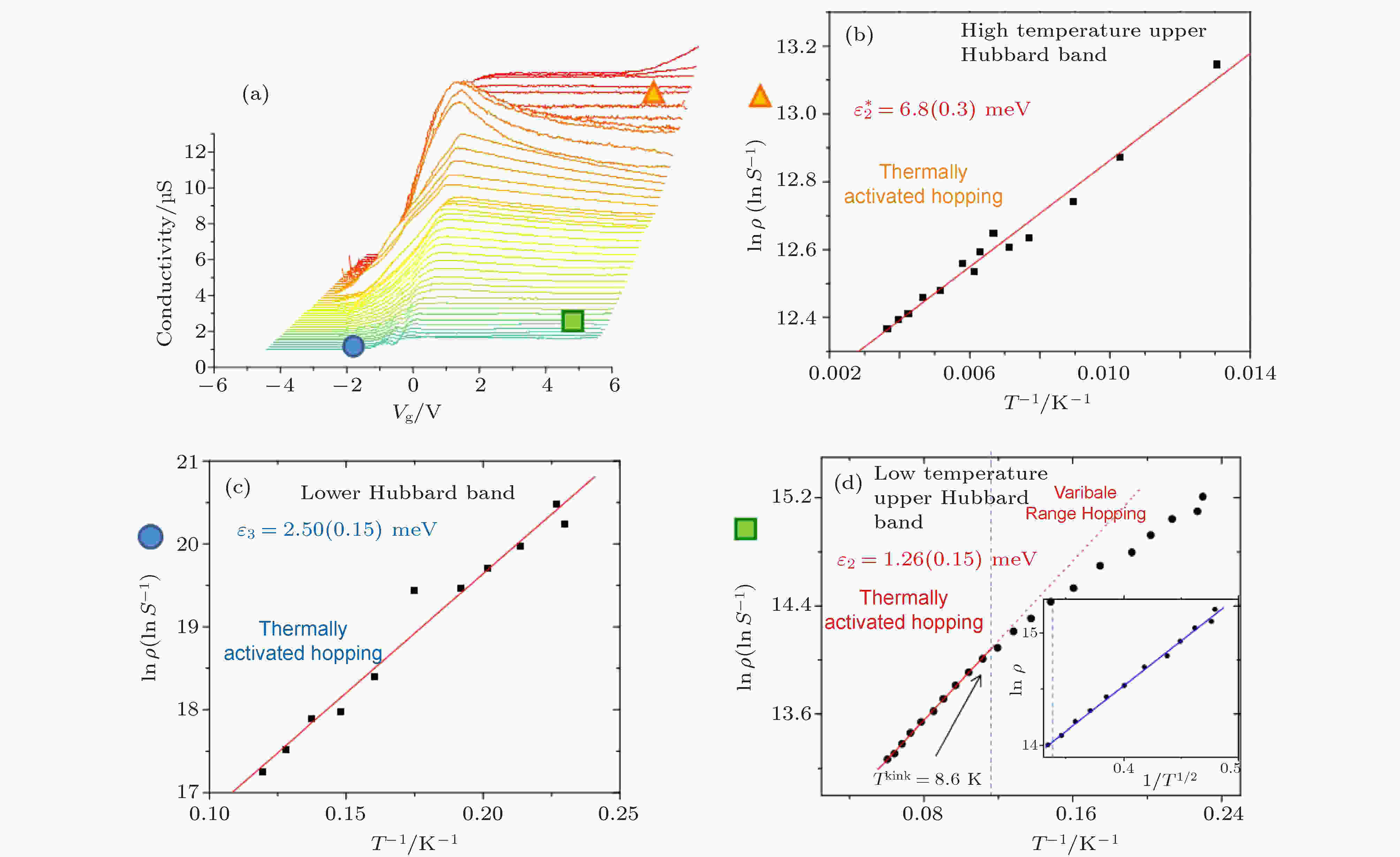

法国低温纳米科学研究所Sanquer研究组[50]采用高k值/金属栅堆叠CMOS技术制备宽度为20 nm和宽度小于7 nm的三栅硅纳米线晶体管 通过对比发现, 宽度小于7 nm的器件虽然表现出良好的静电控制能力, 但是在室温下观测到这其中一部分纳米线晶体管的电子输运行为从场效应晶体管输运特性转变为单电子晶体管输运特性. 产生这种情况的原因是刻蚀后的硅纳米线具有不同大小的粗糙程度且其在沟道中随机分布. 当纳米线表面粗糙度较大时, 沟道电势将变得无序, 对电子的限制作用加大, 能在更高的温度下表现出库仑阻塞效应. 此外, 该研究组还运用标准CMOS工艺制备出沟道直径为3.4 nm、栅长为10 nm, 栅极氧化层厚度为7 nm的Ω形栅极硅纳米线晶体管. 在源/漏和沟道区域之间引入较长的间隔物(25 nm)使沟道与电极之间分隔开, 以此来增强量子限制和库仑相互作用, 进而能在4.2 K到室温的范围内观察到电子通过量子点的输运行为[51].

为了让量子点中的能级间隔大于室温下的温度热能, Lee等[52]通过湿法腐蚀电子束曝光形成的硅纳米线结构, 使其具有不平整的起伏形状, 在硅纳米线结构中自形成硅量子点和隧穿势垒, 器件的结构如图17所示. 该器件能在室温下观测到单电子隧穿通过多个量子能级的行为, 其原因是量子点的物理尺寸足够小, 而且采用的围栅(gate-all-around, GAA)结构能提供良好的控制能力.

图 17 (a)单电子晶体管结构示意图; (b)化学湿法腐蚀后硅纳米线扫描电子显微镜(SEM)图; (c)形成围栅GAA结构后硅纳米线透射电子显微镜(TEM)图; (d)制备的单电子晶体管在150?300 K下的ID-VG特性曲线[52]

图 17 (a)单电子晶体管结构示意图; (b)化学湿法腐蚀后硅纳米线扫描电子显微镜(SEM)图; (c)形成围栅GAA结构后硅纳米线透射电子显微镜(TEM)图; (d)制备的单电子晶体管在150?300 K下的ID-VG特性曲线[52]Figure17. (a) Schematic configuration of the fabricated Si SET; (b) scanning electron microscopy image of the Si nanowire after chemical wet-etching; (c) transmission electron microscopy image of the Si nanowire after fabricating the GAA structure; (d) ID?VG characteristic curves of the fabricated SET at T = 150?300 K[52].

在以上提到的硅纳米结构晶体管中, 电子是通过人造库仑岛进行隧穿输运, 这是基于单电子晶体管的工作原理. 通过干法刻蚀或化学湿法腐蚀形成表面粗糙的纳米线沟道, 进而在沟道中形成超小的硅量子点. 虽然这类硅纳米结构晶体管可以在室温下观测到量子效应, 但是通过纳米加工手段形成的量子点的可控性却不高, 一是难以控制量子点的尺寸, 二是难以控制量子点在器件沟道中的形成位置. 而且在不同的量子点中, 难以确定其分立的量子能级个数.

有限局域纳米空间中的杂质原子也能展现出量子点的特性, 这类利用杂质原子作为量子输运构件的纳米结构晶体管称为杂质原子晶体管. 硅材料中电离杂质具有均匀的玻尔半径, 而且当一个杂质原子作为量子点工作时能提供两个更为确定的能态, 即D0态和D–态, 如图18所示. 其不仅在量子输运中具有更高的可控性, 而且制造工艺与CMOS技术中scaled-down工艺也更为兼容, 有望成为量子计算的基本组成器件. 因此, 以硅纳米结构晶体管为基础, 将杂质原子晶体管的工作温度逐步提升至室温成为了一个重要的研究方向.

图 18 (a)杂质原子晶体管结构示意图; (b)杂质在器件沟道中提供确定的两个能级[19]

图 18 (a)杂质原子晶体管结构示意图; (b)杂质在器件沟道中提供确定的两个能级[19]Figure18. (a) Schematic of dopant atom transistor; (b) two determined levels provided by impurity in device[19].

要想实现杂质原子晶体管在室温下工作, 将其中相关的量子效应拓展到更高的温度下, 杂质原子的隧穿势垒需要远高于室温下的温度热能kBT. 基于这点, 目前提出的思路主要分为以下几种.

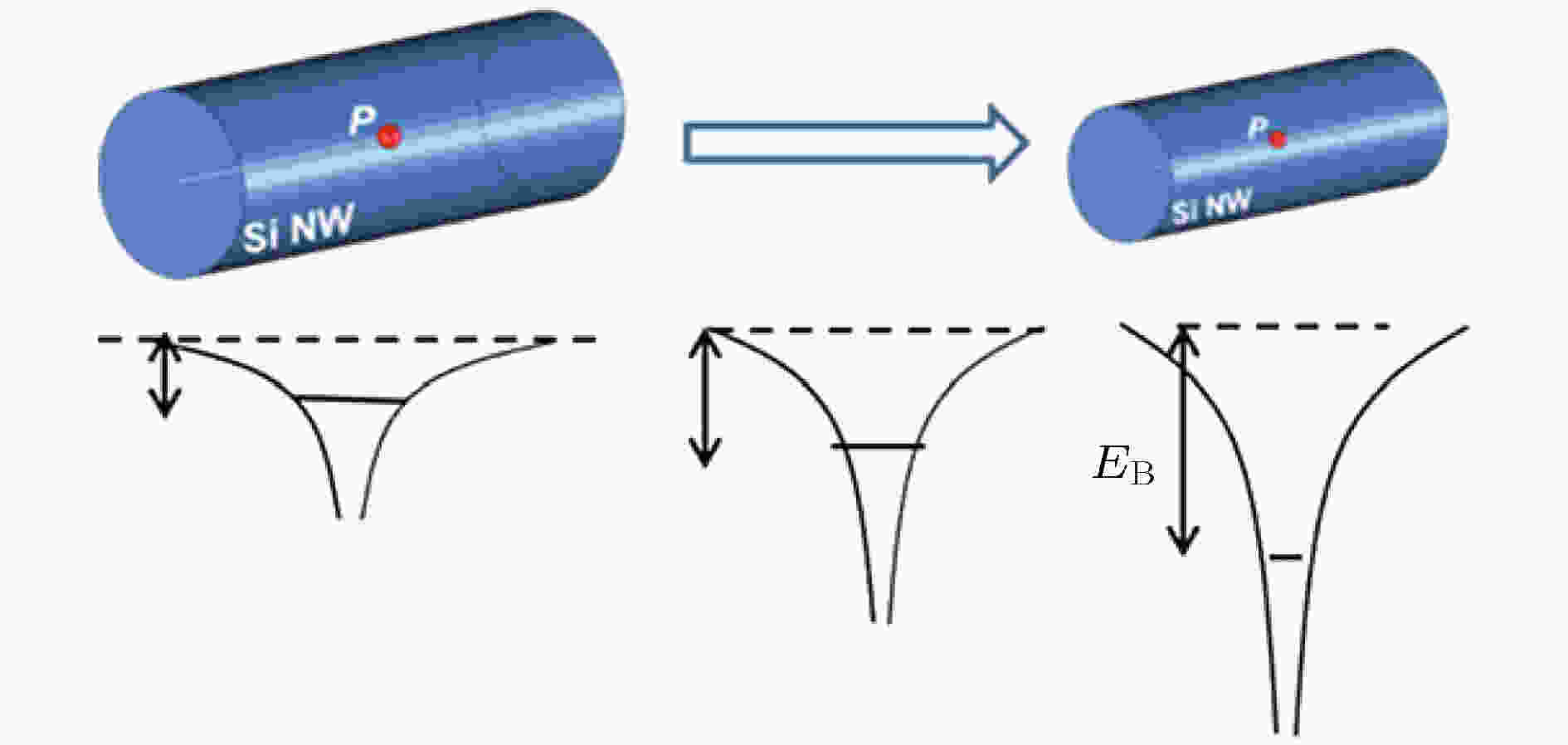

1)增大杂质电离能. 杂质原子晶体管的工作温度较低主要是因为杂质原子的基态能级很浅, 所以需要通过增强量子限制和介电限制来加深杂质原子的基态能级, 即增大杂质原子的电离能. 在量子限制的作用下导带边发生移动, 纳米线尺寸越小, 量子限制作用越明显. 如图19所示, 随着纳米线直径的减小, 杂质的基态能级加深, 即杂质对电子的束缚能增大[53].

图 19 磷原子的基态能级随硅纳米线直径的减小而加深[53]

图 19 磷原子的基态能级随硅纳米线直径的减小而加深[53]Figure19. Ground state of phosphorous donor becomes deeper with decreasing radius of Si nanowire[53].

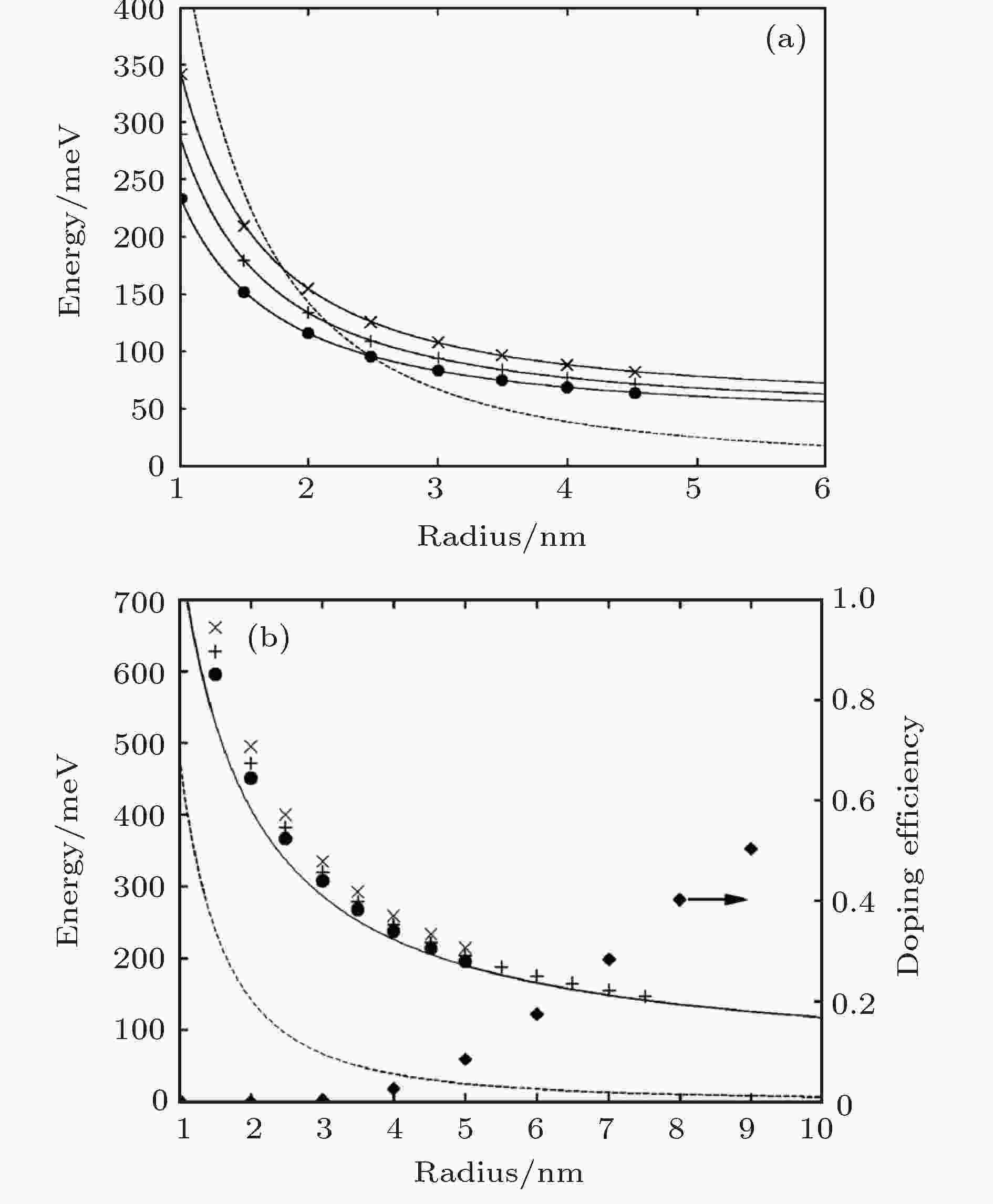

电离能除了受到量子限制作用的影响, 介电限制也能增大杂质的电离能. 电离能增大量为:

图 20 (a)没有和(b)有介电限制时杂质原子的电离能随纳米线半径的变化曲线图[55]

图 20 (a)没有和(b)有介电限制时杂质原子的电离能随纳米线半径的变化曲线图[55]Figure20. Ionization energy EI vs. the wire radius R for donor impurities: (a) Without dielectric confinement; (b) with dielectric confinement[55].

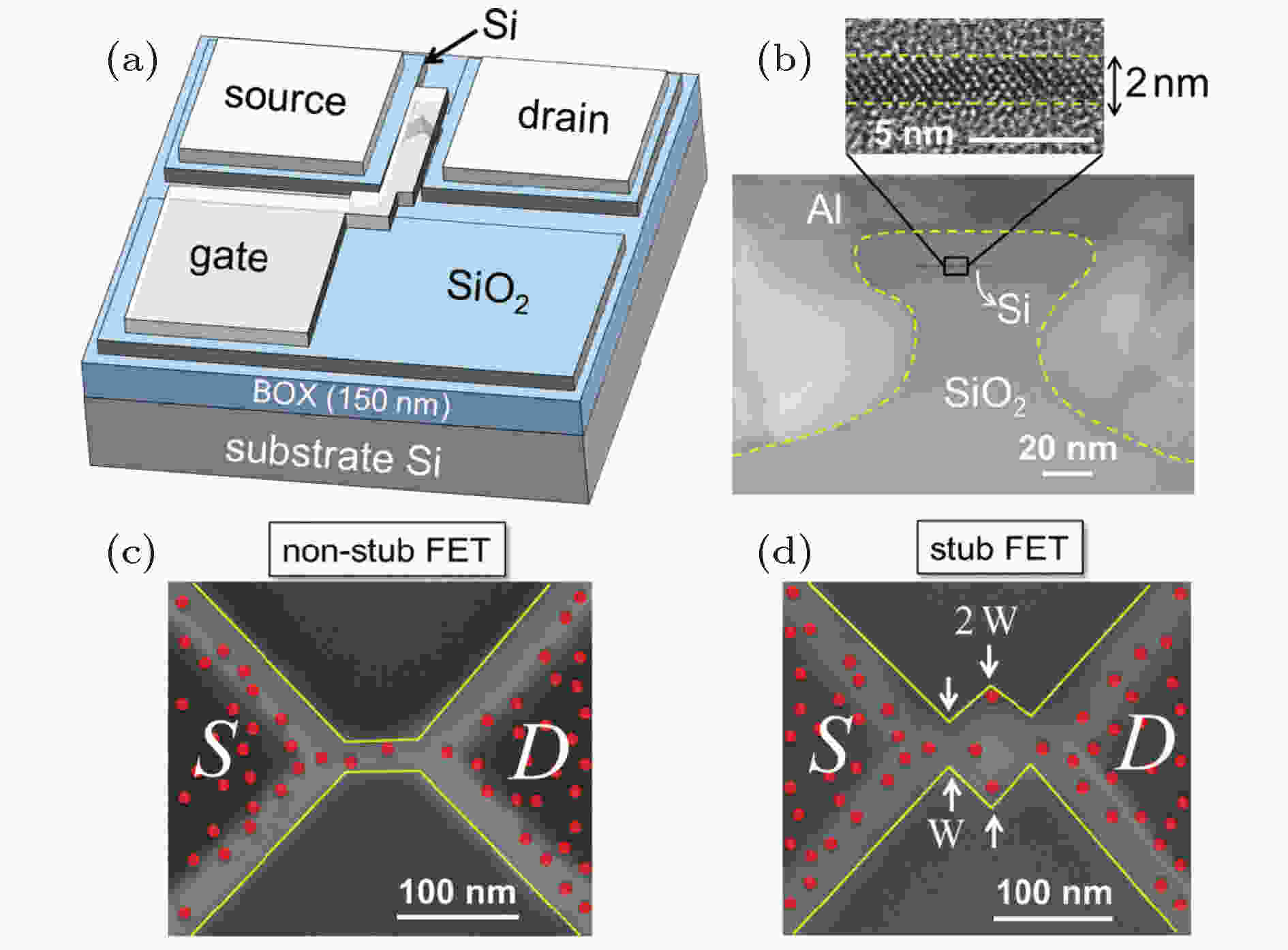

增强对杂质原子的介电限制作用, 其一般的思路是改变纳米线沟道的形状, Tabe研究组[57]在纳米线中间设计了一个stub结构. 这个stub区域中的杂质原子由于更强的介电限制效应, 其基态能级加深, 能在100 K左右观测到单电子隧穿通过施主原子, 原纳米线结构和设计的纳米线结构如图21所示.

图 21 (a) SOI晶体管结构示意图; (b)器件沟道TEM图; (c)原纳米线结构; (d) stub纳米线结构[57]

图 21 (a) SOI晶体管结构示意图; (b)器件沟道TEM图; (c)原纳米线结构; (d) stub纳米线结构[57]Figure21. (a) Schematic of SOI transistor; (b) TEM image taken across the device channel; (c) SEM images of non-stub channel and (d) stub channel[57].

2)由施主原子团簇形成量子点. 施主原子团簇的概念可以这样理解, 当掺杂在纳米结构晶体管沟道中的施主原子足够接近, 它们之间的原子电势将相互重叠, 从而对基态电子的束缚能增大, 电子的隧穿势垒高度增大[53]. 图22更为形象地表述了这一过程.

图 22 基态电子的束缚能随耦合原子数目的增加而增大[53]

图 22 基态电子的束缚能随耦合原子数目的增加而增大[53]Figure22. Binding energy of clustered donors is shown for different N[53].

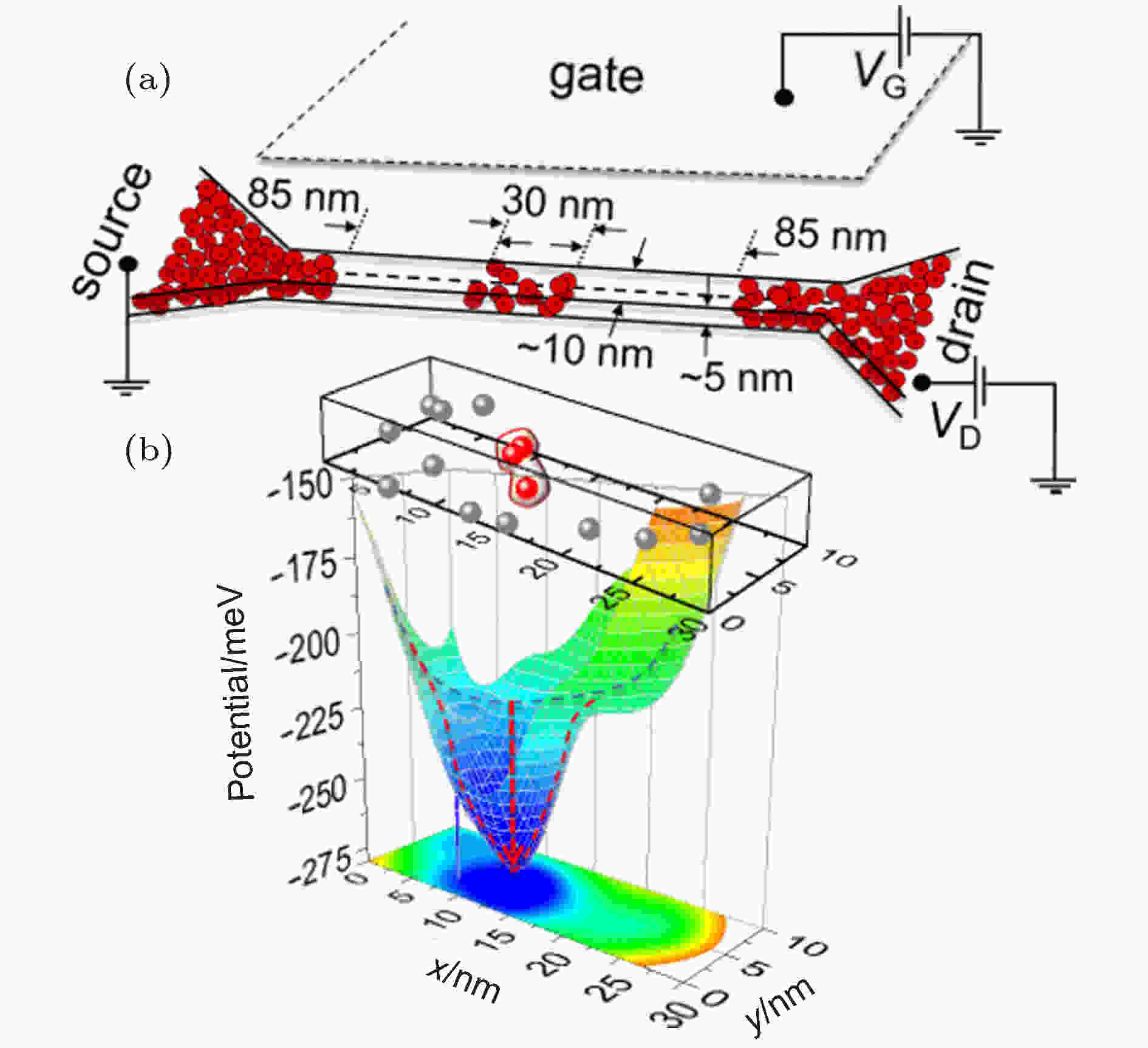

采用这种施主原子团簇的方法需要优化两个关键参数, 一是杂质原子间距, 二是耦合的施主原子数目. 要想提高杂质对电子的束缚能, 需要相对较小的杂质间距和较大的耦合杂质数目, 当杂质间距小到2—3 nm, 即与掺杂在硅中磷原子的玻尔半径相当时, 只需要3—5个耦合的杂质原子就能够让杂质对电子的束缚能提高到100 meV以上[53]. Samanta等[58]运用选择性掺杂工艺, 在纳米线沟道区域中心附近形成一个多杂质耦合的量子点, 沟道中杂质分布情况以及杂质形成的电势分布由图23给出.

图 23 (a)选择性掺杂硅纳米沟道; (b)选择性掺杂区域模拟的最深势阱分布[58]

图 23 (a)选择性掺杂硅纳米沟道; (b)选择性掺杂区域模拟的最深势阱分布[58]Figure23. (a) The selectively-doped Si nanoscale channel; (b) atomistic representation of the potential landscape simulated for a selectively-doped area with deepest potential well[58].

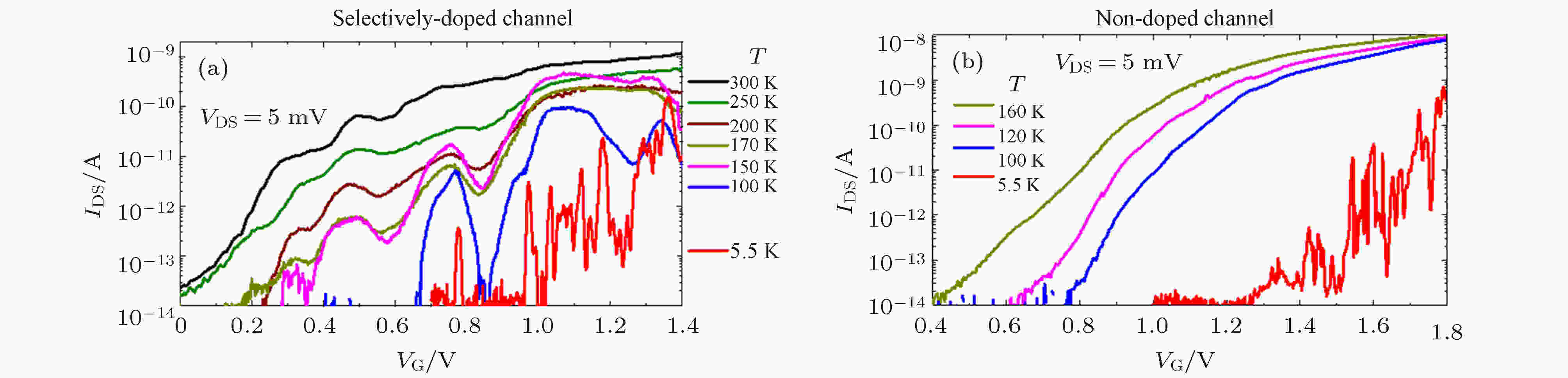

通过测量沟道选择性掺杂SOI-FET和沟道未掺杂SOI-FET这两类器件在不同温度下的ID-VG特性曲线, 可以发现一些相似点和不同点. 如图24所示, 相似点为在低温下(5.5 K)都可以观察到具有微小间距的电流峰. 但这种相似点不能归结为电子通过杂质量子点的输运, 而可能是单电子隧穿通过库仑小岛. 这些库仑小岛可能是在对特定图形的氧化过程中形成, 也可能是由粗糙的纳米线沟道形成. 不同点是随着温度升高, 沟道选择性掺杂SOI-FET在更小的栅压VG下出现了新的电流峰, 而沟道未掺杂SOI-FET在温度大于100 K时不能再观察到单电子隧穿特性, 说明这些较低栅压VG下出现的电流峰是由于电子隧穿通过耦合施主原子形成的量子点.

图 24 (a)沟道选择性掺杂和(b)沟道未掺杂SOI-FET在不同温度下的ID-VG特性曲线[58]

图 24 (a)沟道选择性掺杂和(b)沟道未掺杂SOI-FET在不同温度下的ID-VG特性曲线[58]Figure24. (a) and (b) IDS-VG characteristics as a function of temperature for a selectively-doped-channel SOI-FET (up to 300 K) and for a non-doped-channel SOI-FET (up to 160 K)[58].

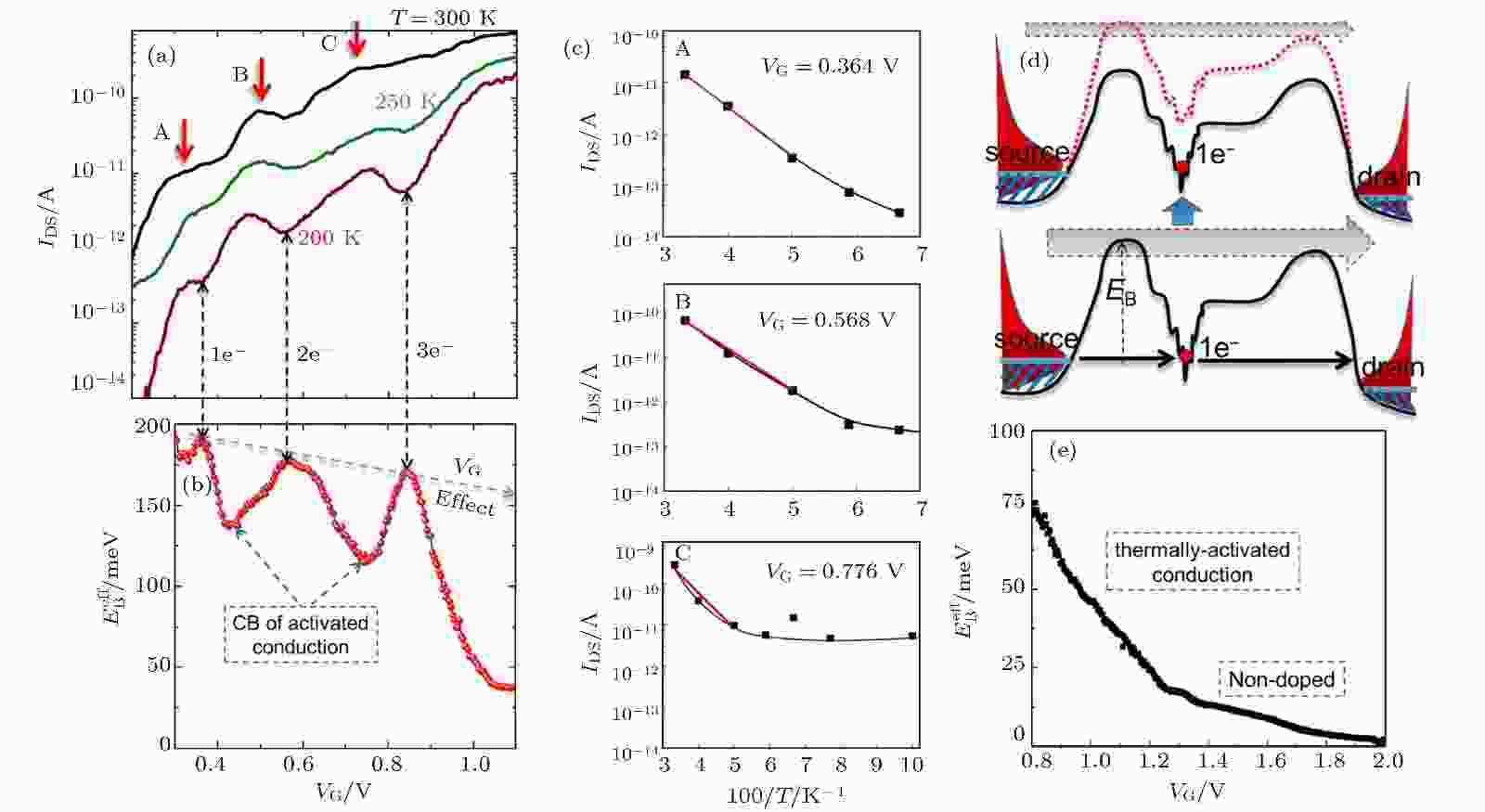

从图25(a)可以看出, 电流振荡现象在T = 200—300 K时仍可以观测到, 即单电子隧穿行为维持到了室温. 图25(c)中Arrhenius曲线所呈现的趋势与传统的库仑阻塞理论不相符合, 这种IDS随1/T的变化情况类似于晶体管中的热激活输运方式, 所以高温下的电流振荡现象需要用修正的库仑阻塞理论来进行解释[59-61]. 从图25(b)中可以看出, 有效势垒高度

图 25 (a)不同温度下, 沟道选择性掺杂SOI-FET器件IDS-VG特性曲线; (b)有效势垒高度随栅压VG的变化; (c)不同电流峰对应的Arrhenius曲线; (d)激活传导的库仑阻塞机制(下图), 量子点俘获电子的库仑阻塞情形(上图); (e)沟道未掺杂SOI-FET器件仅仅表现出热激活传导性质[58]

图 25 (a)不同温度下, 沟道选择性掺杂SOI-FET器件IDS-VG特性曲线; (b)有效势垒高度随栅压VG的变化; (c)不同电流峰对应的Arrhenius曲线; (d)激活传导的库仑阻塞机制(下图), 量子点俘获电子的库仑阻塞情形(上图); (e)沟道未掺杂SOI-FET器件仅仅表现出热激活传导性质[58]Figure25. (a) IDS-VG characteristics as a function of temperature for the selectively-doped channel SOI-FET; (b) effective barrier height (EBeff) estimated from Arrhenius plots as a function of VG; (c) arrhenius plots for VG corresponding to different peaks; (d) schematic illustrations of the mechanism of Coulomb blockade of activated conduction for the single-electron tunneling current peak (lower panel) and for the Coulomb blockade condition with an electron trapped in the QD (upper panel); (e) EBeff extracted for a non-doped-channel SOI-FET, exhibiting only behavior typical of thermally-activated conduction[58].

3)纳米尺度SiO2隧穿结中嵌入杂质原子. 运用电子束曝光技术制备超精细纳米结构晶体管的过程中, 高能的电子束可能对器件造成一定程度的损伤, 而且传统半导体工艺一般是在硅材料中进行掺杂, 杂质原子在硅中形成的量子点势阱比较浅. Durrani等[62]提出用场发射扫描探针光刻(FE-SPL)技术在SiO2层中的嵌入杂质原子, 形成点接触式的量子点晶体管. 研究表明用这种方法形成的量子点具有很深的势阱(大约2—3 eV), 能在室温下更好地限制电子. 器件的点接触结构如图26(a)所示, 通过热氧化过程将点接触区域完全氧化, 在源漏区之间形成一个大约10 nm尺度的SiO2隧穿结, 嵌入在SiO2隧穿结中的磷原子是隔离的, 能形成量子点. 他们通过模拟仿真得出, 量子点的尺寸大约为2 nm. 图26(b)为点接触区域的能带图, 源区和漏区为简并掺杂, 不同的量子点对应形成不同的能态. 当栅极电压变化时, 在与栅极静电耦合的作用下, 这些能态将扫过源端费米能级EFS, 电子共振隧穿通过这些能态.当一个确定的能态与EFS发生共振, 出现一个电流峰, 当EFS位于能态之间, 出现一个电流谷. 扫描探针光刻(scanning probe lithography, SPL)不仅能达到纳米尺度下所需的分辨率, 还能够减少对于纳米器件的损伤. 更为关键的是运用这项技术可以制备在更高温度下工作的纳米结构晶体管, 为实现室温下工作的单原子晶体管提供了思路.

图 26 (a)点接触式量子点晶体管结构示意图; (b)点接触区域的能带示意图[62]

图 26 (a)点接触式量子点晶体管结构示意图; (b)点接触区域的能带示意图[62]Figure26. (a) Schematic of the point contact QD transistor; (b) schematic representation of the energy diagram across the point-contact region[62].

目前关于杂质原子晶体管的具体应用方向, 人们提出了很多思路. 利用纳米尺度下杂质离散的电子态, 可以实现更为复杂的布尔逻辑[63]. 根据嵌入在Fin-FET中单杂质原子的电荷态, 将器件的电流和跨导作为逻辑输出值, 可以实现三值乘法器[64]. 通过对掺杂在硅中相互作用的杂质原子进行电寻址, 可以并行计算出多变量、多值逻辑函数 所有可能的输出值[65]. 更深层次地研究杂质原子晶体管中的量子输运特性是发掘其潜在应用的基础.