全文HTML

--> --> -->2

2.1.原子芯片上的微势阱

大部分的宏观静磁阱(尺寸为1—100 cm)通过大型通电线圈、超导线圈或永磁体等产生. 在芯片上利用微纳加工制作出特定结构的导线, 通电后产生的磁场与外部偏置磁场相结合可以构造与宏观效果类似的微磁阱, 并且得益于衬底对载流导线的优异散热性能, 可以产生很大的电流密度和磁场梯度, 很容易实现如四极阱[12]和Ioffe-Prichard阱(IP阱)[13]等静态阱以及与时间相关的动态阱[14,15].常见的微磁阱主要有如下几种构型.

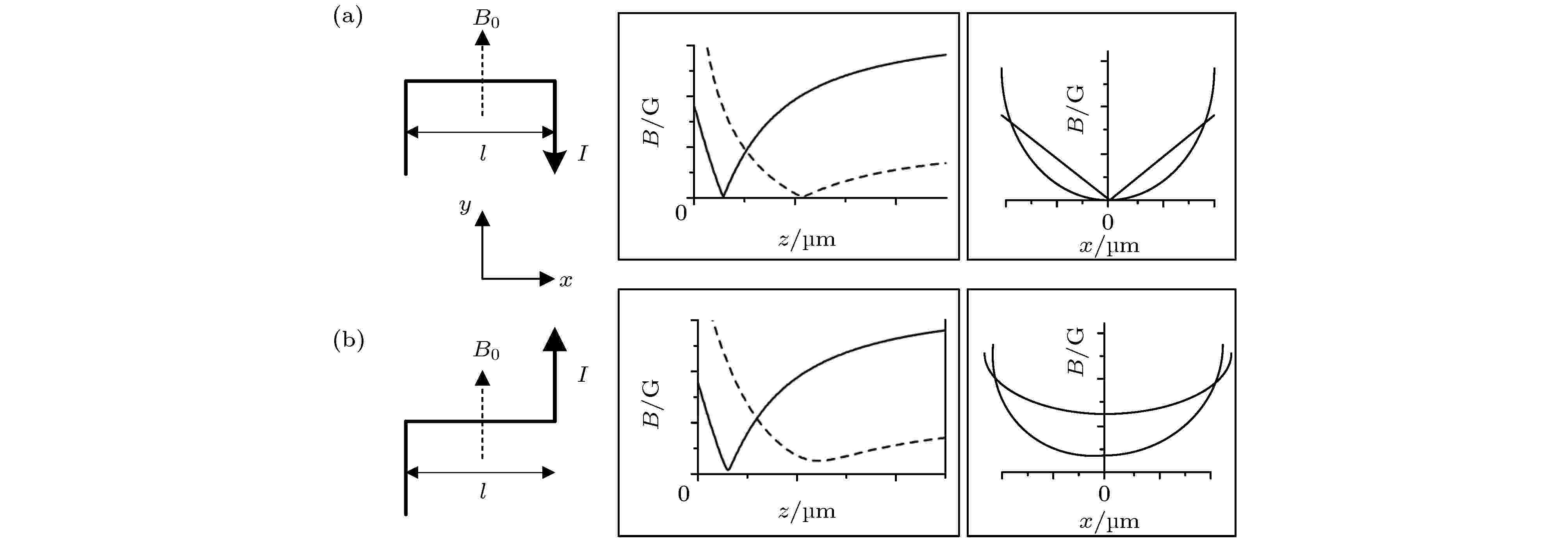

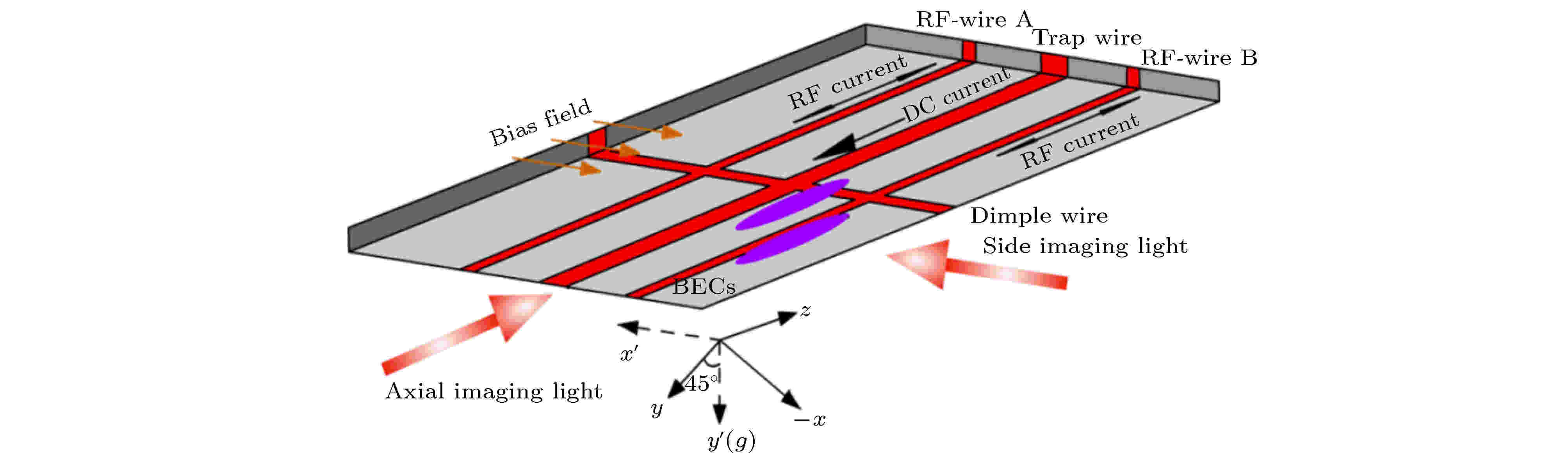

1) 简单结构的三维微磁阱. 将一根直导线弯折成U形或Z形, 通电后再辅以外部偏置磁场就可以构成微磁阱, 如图1所示. 当直导线折成U形时, U形两边所产生的磁场在阱的中心相互抵消, 形成一个零场区域. 由于原子在经过磁场零点处可能因为马约拉纳跃迁由束缚态转变为非束缚态而从磁阱中逃逸, 因此消除磁阱的磁场零点非常重要, 如通过时间轨道平均势(time-orbiting potential, TOP)的方法来消除[16]. 当直导线折成Z形时, Z形阱的中心磁场是两个折弯的部分产生的磁场的叠加, 是一种没有零点的静磁IP阱[17]. 计算U形和Z形阱的磁场性质时需要考虑导线的有限尺寸效应及弯曲部分的折向等因素的影响, 对于不同的导线结构所产生的总磁场, 可以通过数值叠加不同部分所产生磁场来获得[3,18].

图 1 (a)由U形阱形成的四极磁阱; (b)由Z形阱形成的IP阱[3]

图 1 (a)由U形阱形成的四极磁阱; (b)由Z形阱形成的IP阱[3]Figure1. (a) Quadrupole trap by U configuration; (b) Ioffe-Pritchard trap by Z configuration[3].

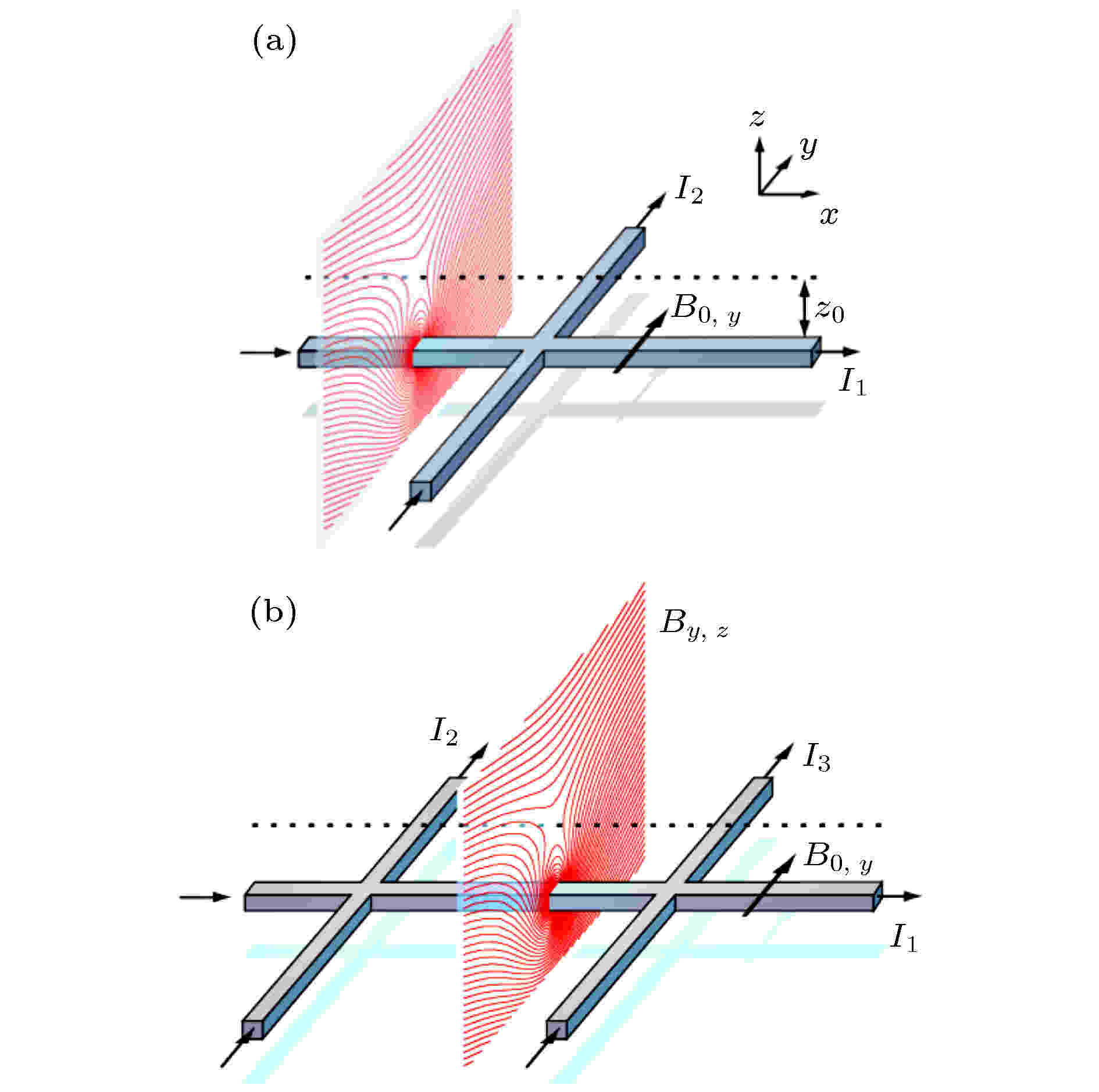

2) 基于交叉导线结构的表面微磁阱. 在垂直于侧边导引的导线方向加上一根直导线, 会在导线交叉位置上方形成dimple阱[19,20], 如图2(a)所示. 在y方向电流较弱的情况下, dimple阱可以认为是一个由x方向导线形成的四极阱和y方向导线形成的磁场的叠加, 形成的雪茄型阱的方向取决于偏置场方向. 此时额外添加一根载有相同大小电流的导线即可得到两个磁场极值, 这种结构被称为H形阱, 如图2(b)所示[20]. 对应于y方向两根导线的相对电流的方向(平行或者反平行)的不同, H形导线结构也可以实现四极阱或IP阱.

图 2 (a) Dimple阱; (b) H形阱[20]

图 2 (a) Dimple阱; (b) H形阱[20]Figure2. (a) Dimple trap; (b) H-type trap[20].

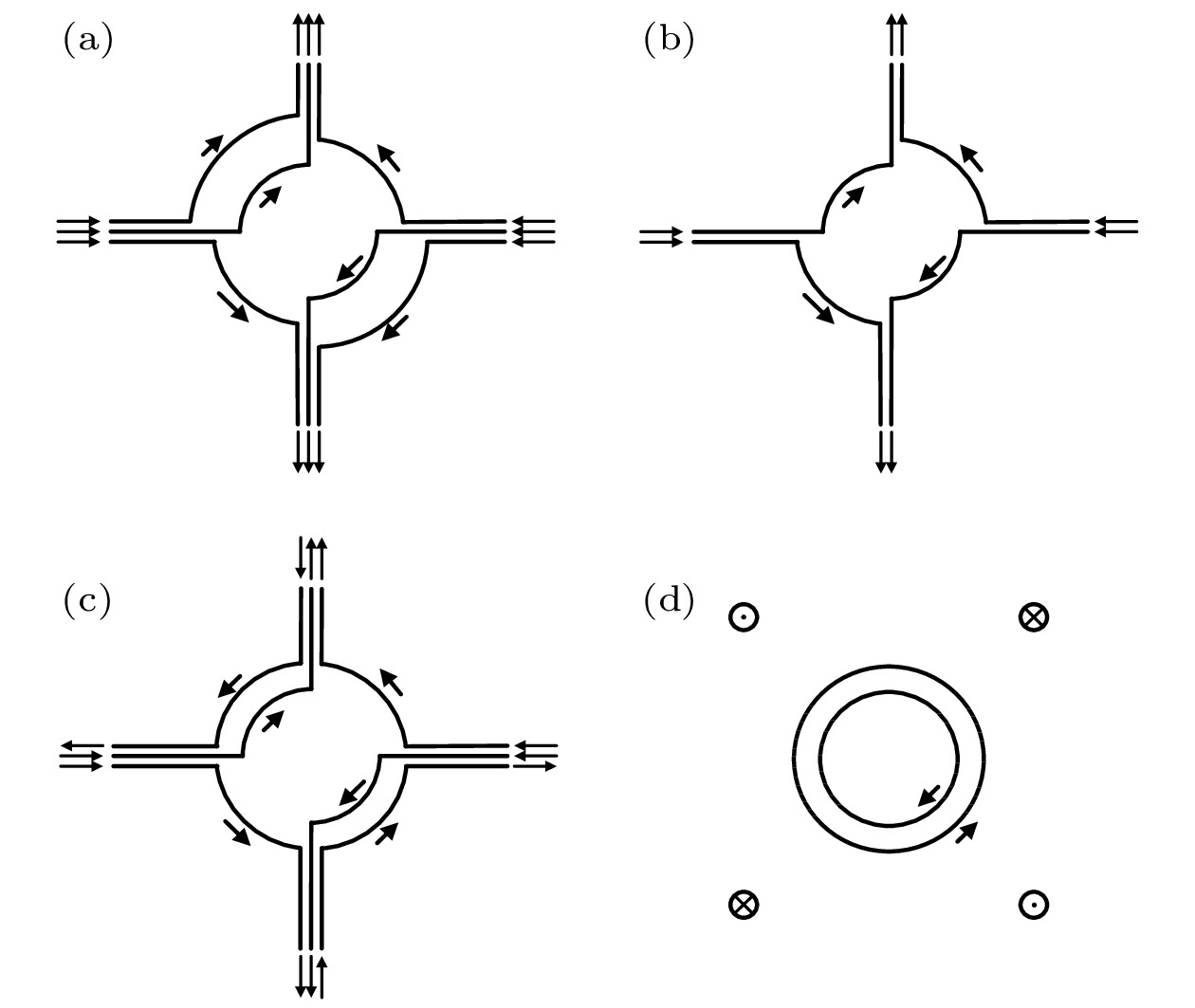

3) Weinstein-Libbrecht阱. 1995年, Weinstein和Libbrecht[21]巧妙地提出了实现IP阱的平面载流导线设计方案, 图3为几种典型结构[21,22]: 图3(a)由3组同心半环组成; 图3 (b)由两组同心半环和一个外加偏置磁场组成; 图3 (c)由一个半环、一个圆环和一个偏置磁场组成, 基本结构与图3 (b)类似, 不同之处在于其轴线的磁场梯度更大而径向的磁场梯度更弱, 这意味着相同的电流强度可以得到更深的势阱; 图3 (d)由两个圆环、一个偏置磁场和额外的Ioffe棒组成.

图 3 四种平面Ioffe阱的方案[22]

图 3 四种平面Ioffe阱的方案[22]Figure3. Four planar Ioffe trap configurations[22].

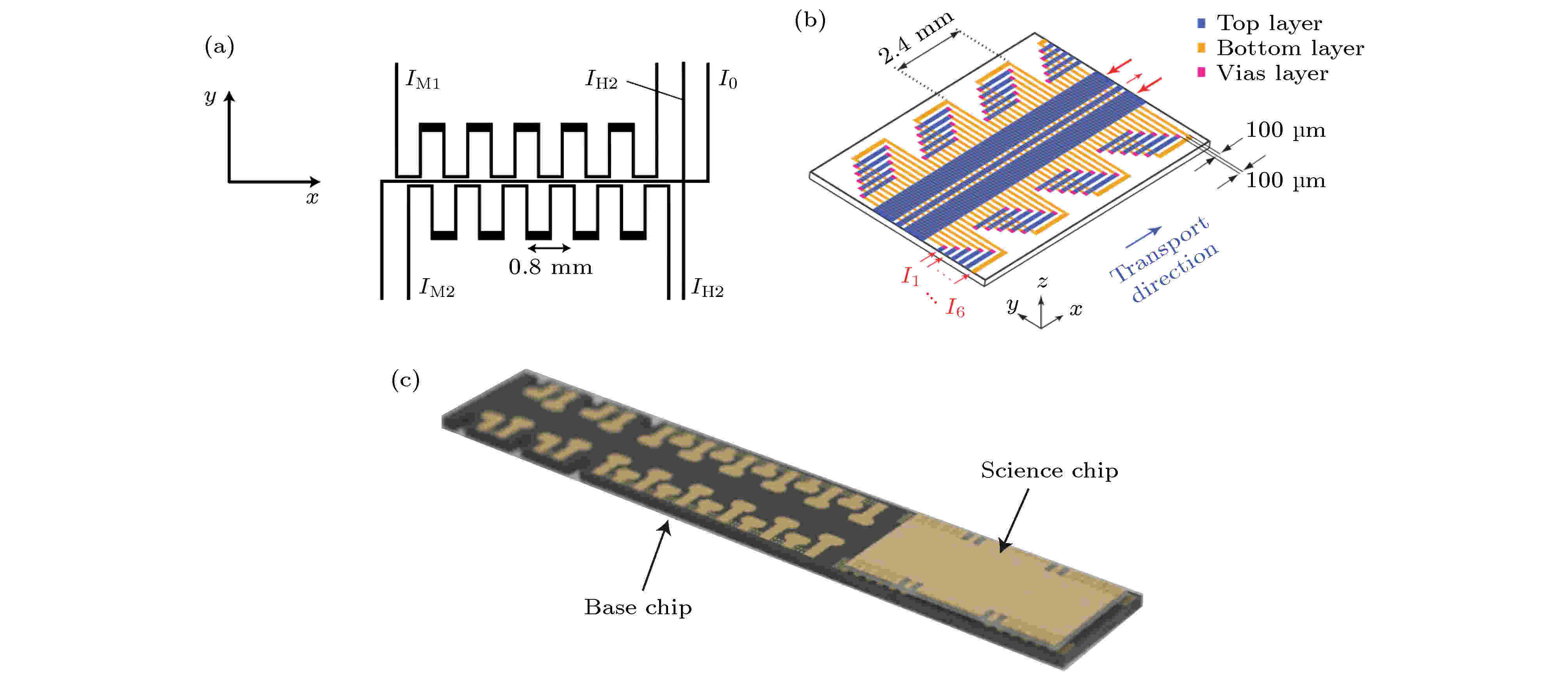

4) 复杂结构微磁阱, 如原子传送带. 图4(a)是最早实现的原子传送带结构[23]. 后续研究人员在此基础上提出改进的双层原子传送带, 可以工作在有偏置磁场和无偏置磁场两种模式下, 具有6通道独立的电流, 通过将单轴线改为3根平行线来代替外部偏置磁场的作用, 显著提升了传送的性能, 原子的线性传送距离为6 cm, 总传送距离可达24 cm, 如图4(b)所示[24]. 近期科研人员提出了基于氮化铝(AlN)基底的原子传送带结构, 如图4(c)所示. 该结构包括两个部分, 其中science chip部分包含利用金导线制作的Z形阱、U形阱和mirror-MOT, base chip部分则是多阵列铜导线的原子传送带结构. 87Rb冷原子团在该传送带中以40 mm/s的速度运动, 比前期文献报道[25]的原子运动速度5.3 mm/s几乎提高了1个数量级.

图 4 多种原子传送带结构[23-25]

图 4 多种原子传送带结构[23-25]Figure4. Multiple configurations of atom conveyor belts[23-25].

除上述的几类势阱外, 还有一类相对复杂的双势阱. 如华东师范大学印建平等[26,27]提出了双Z形和双U形载流导线的微磁阱. 双Z形磁阱由一个Z形载流导线、一根载流直导线和一个偏置磁场构成, 调节Z形载流导线和直导线中电流的相对强度可以实现从微磁双阱到单个阱的演化, 用于双样品BEC的制备以及BEC干涉实验的研究. 双U形微磁阱由两根U形载流导线组成, 它们载流方向相反, 通过调节电流的大小可以实现单磁阱到双磁阱的转变.

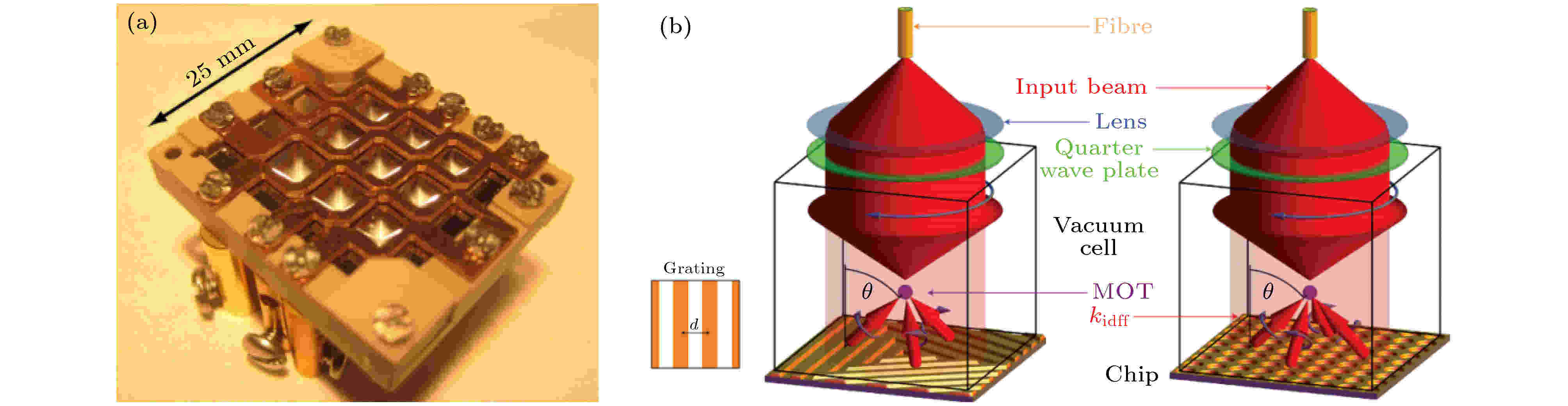

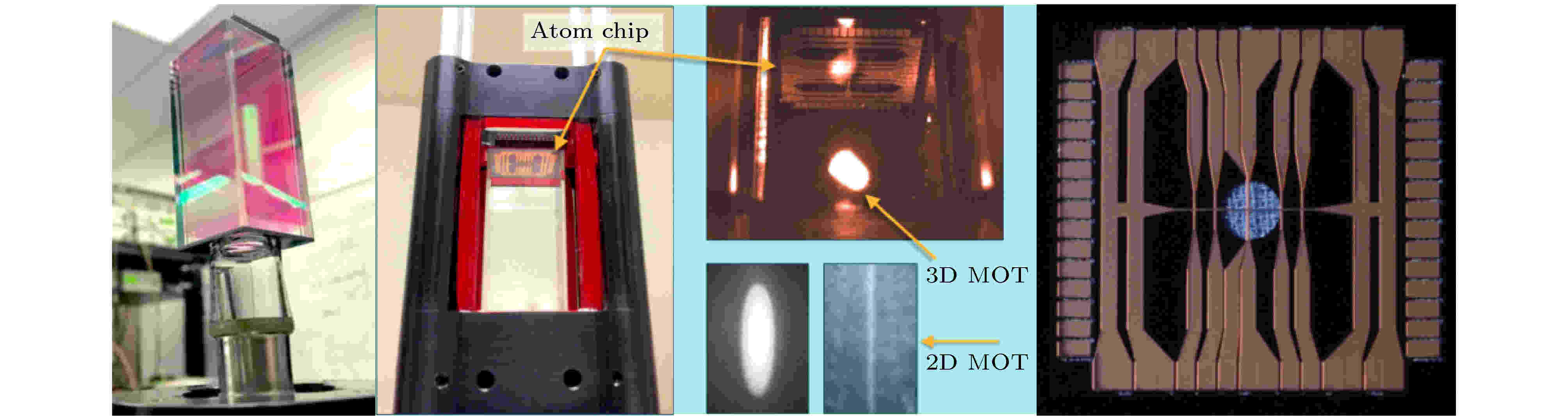

原子芯片上微磁阱产生的势阱深度有限, 且距离芯片表面一般很近, 很难直接从真空囚禁原子, 因此一般首先用磁光阱(MOT)将原子冷却和囚禁, 然后转移装载至芯片微磁阱中[28]. 传统的MOT需要3对互相垂直的激光束, 在原子芯片上应用需要发展新的方法, 避免芯片对激光的遮挡. H?nsch小组[3]最早提出了微型mirror-MOT方案, 他们将U形金载流导线刻蚀在氧化铝陶瓷基底上, 用溅射技术镀一层200 nm厚的银膜提高对激光的反射率, 成功将6束激光系统简化为4束激光系统, 实现了87Rb原子的表面囚禁. 后续国际上提出了一系列微型mirror-MOT或相似的方案, 如反射镜金字塔结构或者光栅结构, 都实现了冷原子的囚禁, 比传统的光学系统体积降低了接近100倍, 功耗降低了近1/10, 如图5(a),(b)所示[29-33]. 最近南方科技大学联合英国伯明翰大学等单位利用介质超构表面光学芯片实现了对原子的囚禁和冷却, 俘获的原子数约为107个, 原子温度约35 μK, 通过进一步的蒸发冷技术有望实现芯片上的BEC[34].

图 5 基于(a)金字塔结构[29], (b)光栅结构[33]的芯片微MOT

图 5 基于(a)金字塔结构[29], (b)光栅结构[33]的芯片微MOTFigure5. Micro-MOTs chip based on (a) micro-paramide arrays[29] and (b) gratings[33].

2

2.2.原子芯片上的导引

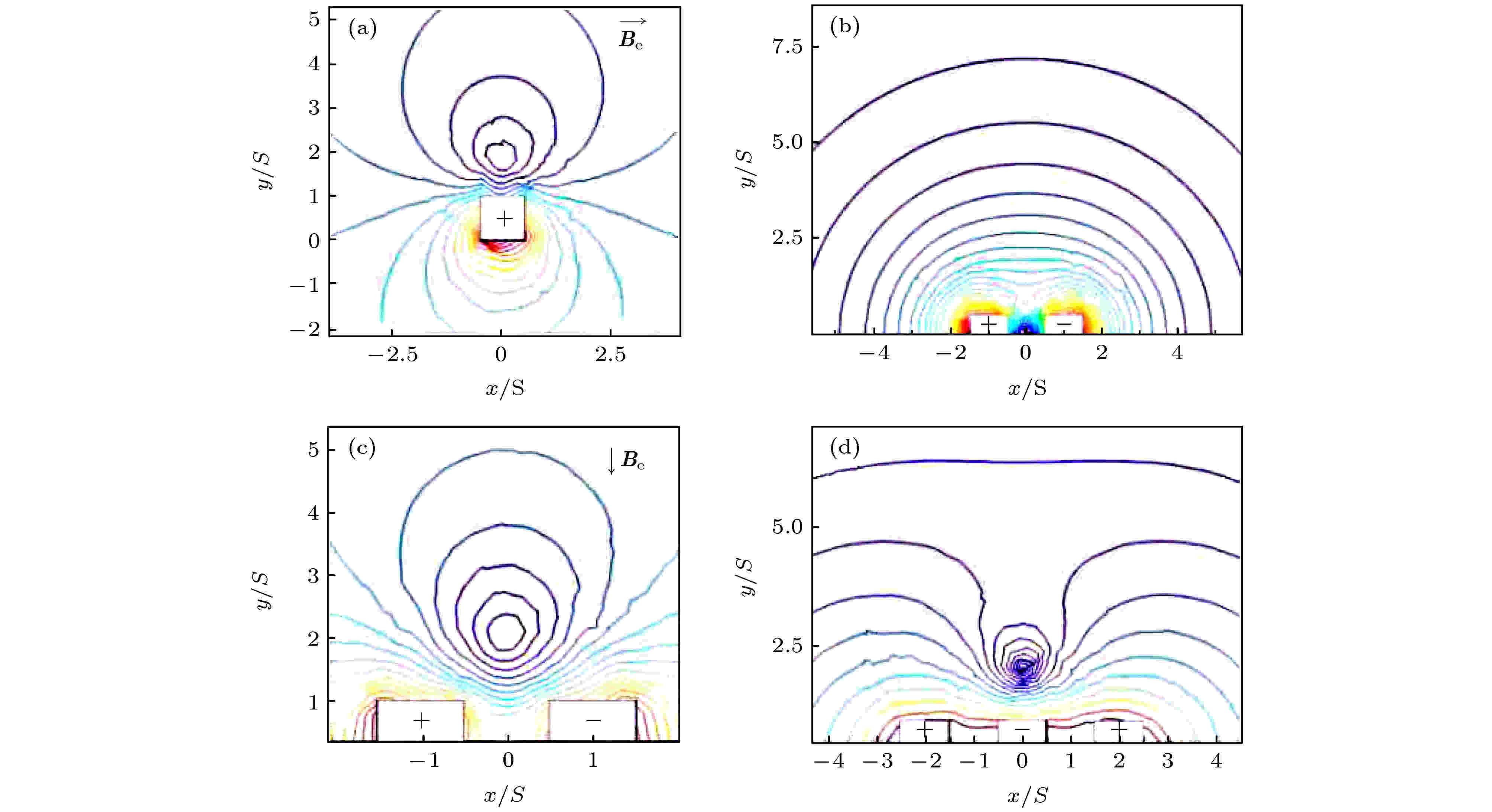

严格意义上讲, 原子导引和原子波导有一定区别: 原子导引是指原子导管的横向尺寸远大于原子的波长, 原子在导管内以粒子的形式存在, 其运动轨迹可用射线光学来处理; 原子波导是指原子导管的横向尺寸约等于原子的波长, 原子在导管中以物质波的形式存在, 属于波动原子光学的内容[11]. 一般文献中没有对二者进行特别区分, 本文统一使用原子导引这一表述.本节仍主要关注基于原子芯片上载流导线的磁导引方案. 常见的磁导引如图6所示, 包括: 1) 基于单根载流导线产生的磁场与外加偏置磁场的叠加, 如原子绕着载流导线运动的Kepler导引[1], 以及原子在二维四极场内沿着磁场最小的方向线运动的侧边导引等[22]; 2) 基于两条平行载流导线所产生的磁场与外置偏置磁场的叠加, 包括共面成对同向载流导引和共面成对异向载流导引[22]; 3) 基于多条平行导线产生的磁导引[35,36], 其优势在于可以通过载流导线自身产生偏置磁场, 不需要外加宏观线圈的辅助[37]; 4) 通过将平行载流导线弯曲成同心环或基于不同复合导线结构实现的环形导引, 具有闭合环路面积大、结构对称、能够消除共模噪声等优点. 但该导引往往存在由于电流引线引发的导引缺口. 针对于此,有科研人员提出了七线布局的双层原子芯片、双相位射频电流或者缀饰感应势等结构. 此外, 我国上海光机所还提出了基于垂直引线的三环线结构以及阿基米德螺线和TOP结合等闭合且中心无磁场零点的环形导引方案[38-40]. 2017年, 弗吉尼亚大学Horne等[41]基于微型片上线圈构成的TOP阱实验上获得了BEC环形闭合回路的Sagnac原子干涉仪, 并于2020年成功实现对转动信号的测量, 如图7所示.

图 6 (a) 侧边导引; (b) 共面成对同向载流的侧边导引; (c) 共面成对异向载流的侧边导引; (d)三线导引. 图中S为导线间距

图 6 (a) 侧边导引; (b) 共面成对同向载流的侧边导引; (c) 共面成对异向载流的侧边导引; (d)三线导引. 图中S为导线间距Figure6. (a) Side guide; (b) two-wire side with co-propagating currents; (c) two-wire side guide with opposing current directions; (d) three-wire guide. S is the distance between wires.

图 7 弗吉尼亚大学设计的MOT[41]

图 7 弗吉尼亚大学设计的MOT[41]Figure7. Magnetic trap assembly proposed by University of Virginia[41].

无论何种原子导引, 理想情况下都应具备单模、光滑、无磁场零点、低噪声和低损耗等特性. 单模特性是指物质波只占据基模, 避免物质波耦合到其他横模上; 光滑是指没有势场起伏从而抑制散射和色散; 无零点是为了避免零磁场点导致的原子损失; 噪声和损耗主要来源于电流噪声、电场强度起伏、原子自发辐射、Casimir-Polder (C-P)力和范德瓦耳斯力以及表面吸附效应等, 会缩短原子寿命、降低信噪比, 缩短相干长度和相干时间.

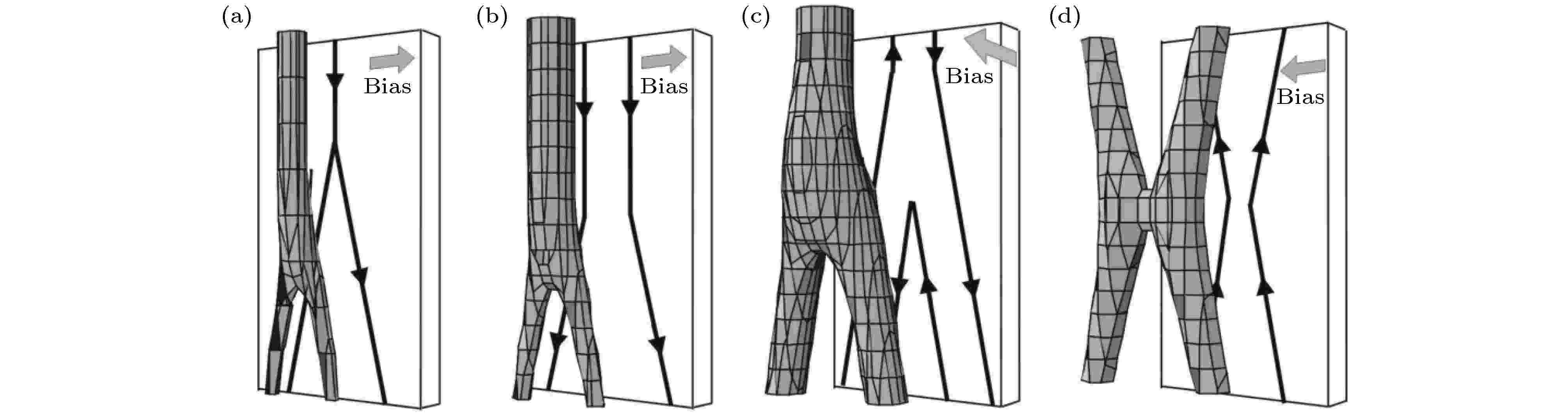

当原子团在导引中传输时, 往往还需要对其进行相干分束与合束. 最简单的分束方案是将单势阱转变为双势阱, 既可在时域中通过动态的改变势阱形状来实现, 也可以通过Y形或X形导线结构在空间中实现. 常见的时域相干分束包括双线平行分束[18]、五线平行分束[42]以及交叉导线分束等[4,43]. 基于双线平行分束Shin等[44]实现了对BEC的分束, 该方案结构简单, 但是对电流涨落和磁场噪声非常敏感. 五线平行分束在实验上利用稳定的电流驱动装置以及标准的微加工工艺很容易保证电流涨落变化小于10–4, 对于分束过程中偏置磁场的稳定性要求也大大降低, 目前已经实现了对热原子团的分束, 并可通过调整外置偏置磁场控制分束后两个原子团的数目. 由于在分束过程中存在明显的加热现象, 因此目前还没有基于此方案实现BEC分束. 交叉导线分束可以实现BEC沿弱束缚方向(I0方向)的分束, 分束后原子团的距离依赖于垂直于I0方向导线的间距, 目前已有多种交叉导线分束的方案[45,46]. 此外, Hommelhoff等[43]提出一种类似交叉导线分束的方案, 他们利用两个沿I0方向平移的U形导线来代替交叉导线结构, 通过降低I0的强度实现单势阱到双势阱的转变, 最大的势阱间距约为135 μm, 每个势阱里装载500—1500个原子.

空间中最常见的分束方案主要为X形和Y形分束. 其中典型的Y形分束结构如图8(a)所示, 可以按任意比例把原子导引到两个臂上, 但该方案导引效率不高、原子损失较大[47]. 改进后的双线结构Y形分束器如图8(b)所示, 其输入端包括两根载流导线和一个偏置磁场, 这种结构对磁场和电流涨落非常敏感, 且依然存在原子较强的向后反射的问题. 图8(c)的Y形导线结构中每个臂中的电流方向相反, 输入和输出有完全相同的特性. 除Y形导引外, Cornell小组用X形磁波导分束结构获得了50:50的分束比, 最大原子数通量达1.5 × 105 s–1, 其基本原理是利用X形空心磁管道实现弱场搜寻态的原子导引的磁分束, 如图8(d)所示[48].

图 8 原子芯片上的Y形分束和X形分束[22]

图 8 原子芯片上的Y形分束和X形分束[22]Figure8. Beam splitter for guided atoms using Y-shaped and X-shaped current carrying wires[22].

仅利用静磁阱对冷原子进行相干分束和合束非常困难, 这是因为双势阱的间距通常需要在1 μm量级才有好的隧穿和分束保真度, 但是由于芯片衬底噪声的影响, 目前双势阱可以实现的间距与这一水平仍有较大差距. 引入射频场[49]和光场[50]能显著提高相干分束与合束的性能, 也是目前常见的实验方式. Zobay和Garraway[51]在2001年首次将IP阱和射频缀饰势相结合, 其基本原理是处于静磁场中的原子会发生塞曼劈裂, 射频场与劈裂后的能级之间发生强耦合而形成新的缀饰本征态, 此时原子可以被认为处于一个等效的缀饰势中. 射频缀饰势对原子团的束缚很强, 原子团可以处于距离芯片表面相对较远的位置从而避免芯片表面吸附效应和磁场涨落对原子团的影响, 故而可以在较大的导线结构(约500 μm)上实现分束, 如图9所示[52]. 如果采用静磁场获得相似的分束效果, 导线尺寸则需要在数微米, 这无疑提高了加工的难度. 另外, 射频缀饰势还可以在实现光滑波导的同时避免磁场零点.

图 9 原子芯片上基于射频场的双势阱物质波分束[52]

图 9 原子芯片上基于射频场的双势阱物质波分束[52]Figure9. Matter-wave beam splitter by dressing RF-fields on chip[52].

基于光场的相干分束可以在保持原子内态不变的情况下只改变原子的外在动量状态, 最常用的方法是利用激光脉冲驻波对原子云的Raman-Nath衍射或Bragg衍射实现原子外态分束. 为了尽量保证分束后的两团原子波包的速度和布居数相等实现50∶50的对称分束, 可以采用双频率Bragg驻波分束方案或者双脉冲Raman-Nath驻波分束[53,54].

3.1.原子芯片的设计与制备工艺

如前所述, 通过静磁场、静电场、光场等方式均能对原子进行操控. 静磁场原理可以分别采用载流导线、永磁薄膜[55]、软磁薄膜[56]等方式实现. 其中, 永磁薄膜产生的磁场几乎不产生波动, 引起的自旋反转跃迁率几乎为0, 但其磁场强度和结构固定, 很难灵活调整; 软磁薄膜的磁场稳定且强度可调, 但其磁化容易受外场影响、不易控制; 用微电子工艺可在芯片表面制备出载流导线, 用相对较小的电流即可产生可观的磁场梯度, 磁场强度和结构形貌可以通过灵活设计载流导线的构型实现, 具有很强的优势.载流导线型原子芯片一般通过Z阱、U阱等结构实现原子团的转移, 再辅以用于蒸发冷却的H形或W形导线结构, 根据不同应用目的还需要设计特殊的导引. 在设计中需要确定势阱和导引距芯片表面的高度、磁阱的梯度及导线的载流能力等要素, 结合工艺条件进行迭代修正, 确保芯片具备可实现性. 以两根平行导线为例, 导线间隙与导线间的电阻正相关, 即导线间距越小其电阻越小; 但过小的导线间距会急剧增大剥离或刻蚀工艺的难度, 在制备过程中易产生缺陷导致短路, 故而实际中一般设定导线间隙和导线高度比大于1.

原子芯片的基底和载流导线材质以及适宜的微纳工艺技术是决定原子芯片实际性能的重要因素. 原子芯片的基底要支撑载流导线、提供导线之间的电绝缘并进行散热, 因此需要具备良好的热传导性和绝缘性, 能承受大的电场, 且在工艺上易于实现高质量、高平整度的材料制备. 由于传统的半导体工艺一般采用硅晶圆, 故而(100)晶向的单晶硅是最常见的芯片基底, 其室温下的导热系数为150 W/(m·K), 厚度一般约500 μm, 经过抛光后可获得光滑的表面. 为了确保导线间的良好绝缘, 通常会在硅基底上采用等离子体增强化学气相沉积法(PECVD)或热氧化法制备一层氧化硅(SiO2), 使基片表层电阻率大于1016 Ω·cm. 虽然PECVD制备效率高, 但生长的SiO2的表面粗糙度会高于热氧化. 由于SiO2的热导率只有1.5 W/(m·K), 所以SiO2通常只生长数百纳米[57]. AlN, GaAs等材料也是原子芯片的常用基底. 尽管AlN陶瓷室温热导率高达319 W/(m·K), 但它抛光后的表面粗糙度约为40 nm, 不但很难实现高质量大面积制备, 且往往存在微米尺度的缺陷, 对实现小于10 μm的载流导线较为不利. 单晶AlN的表面粗糙度可以到原子级, 但是成本较为昂贵. 当在原子芯片上需要构造微MOT时, 往往还会采用透明原子芯片, 此时常采用对780 nm激光具有高透过率的碳化硅(SiC)、SiO2或蓝宝石(Al2O3)等基底.

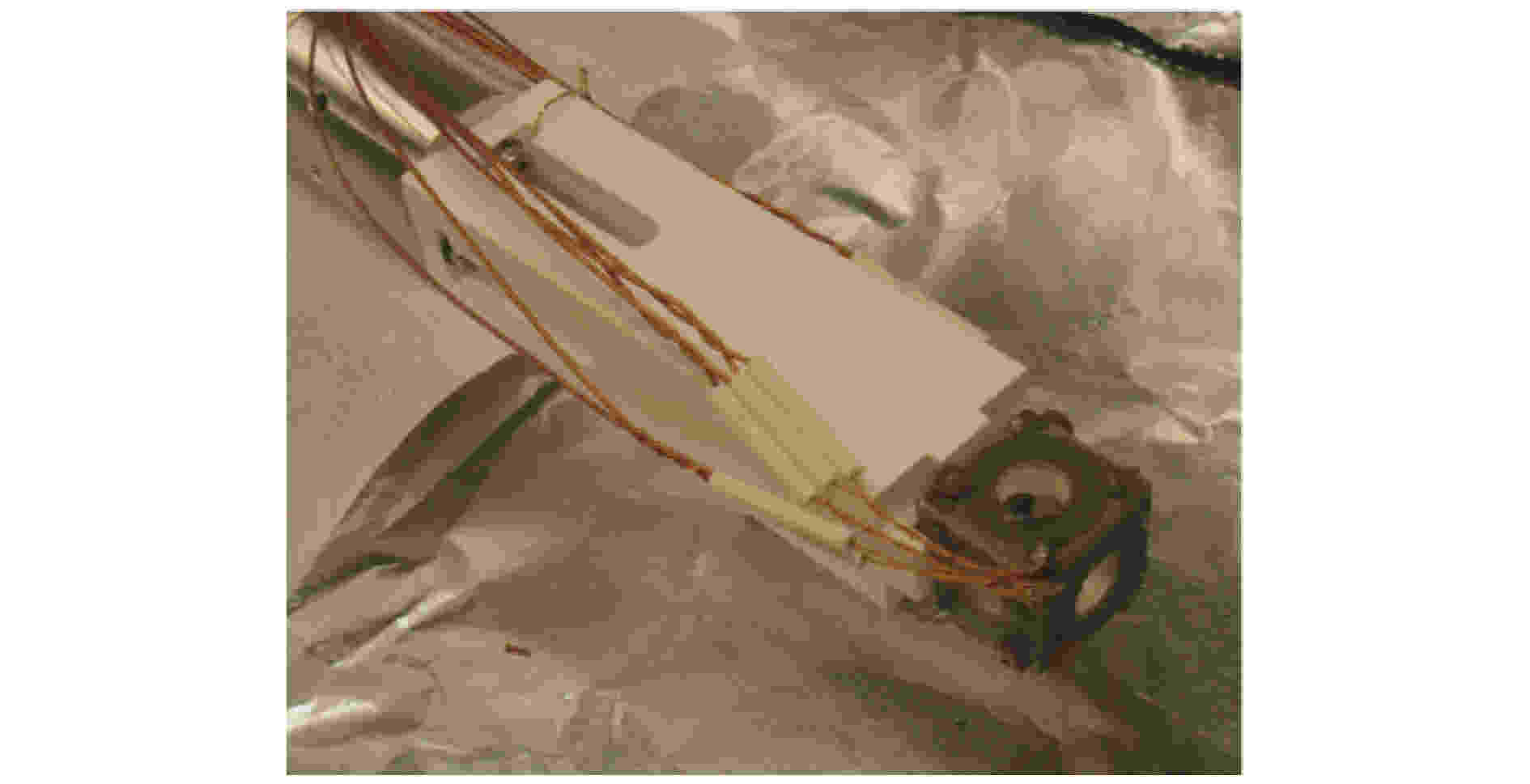

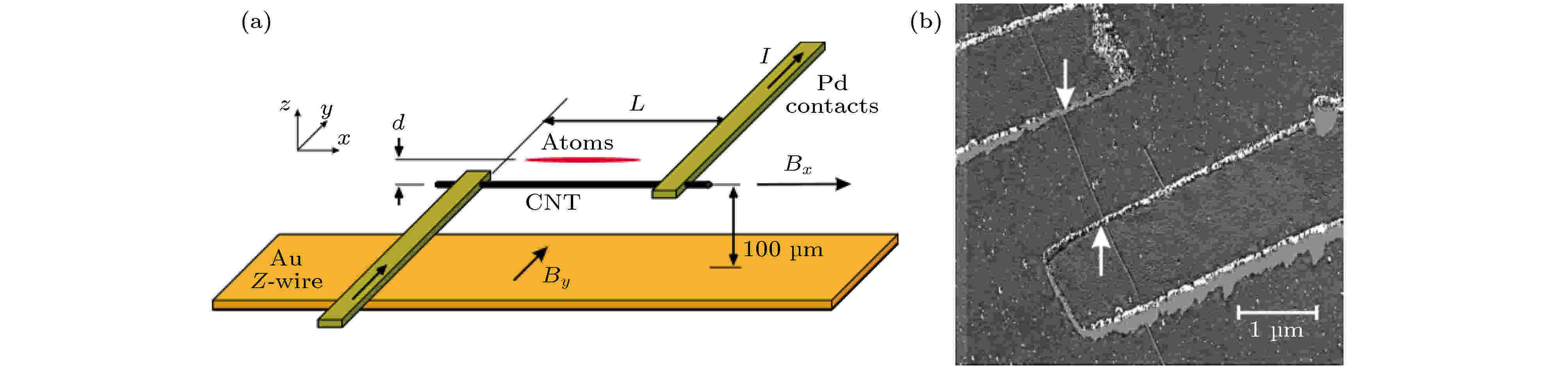

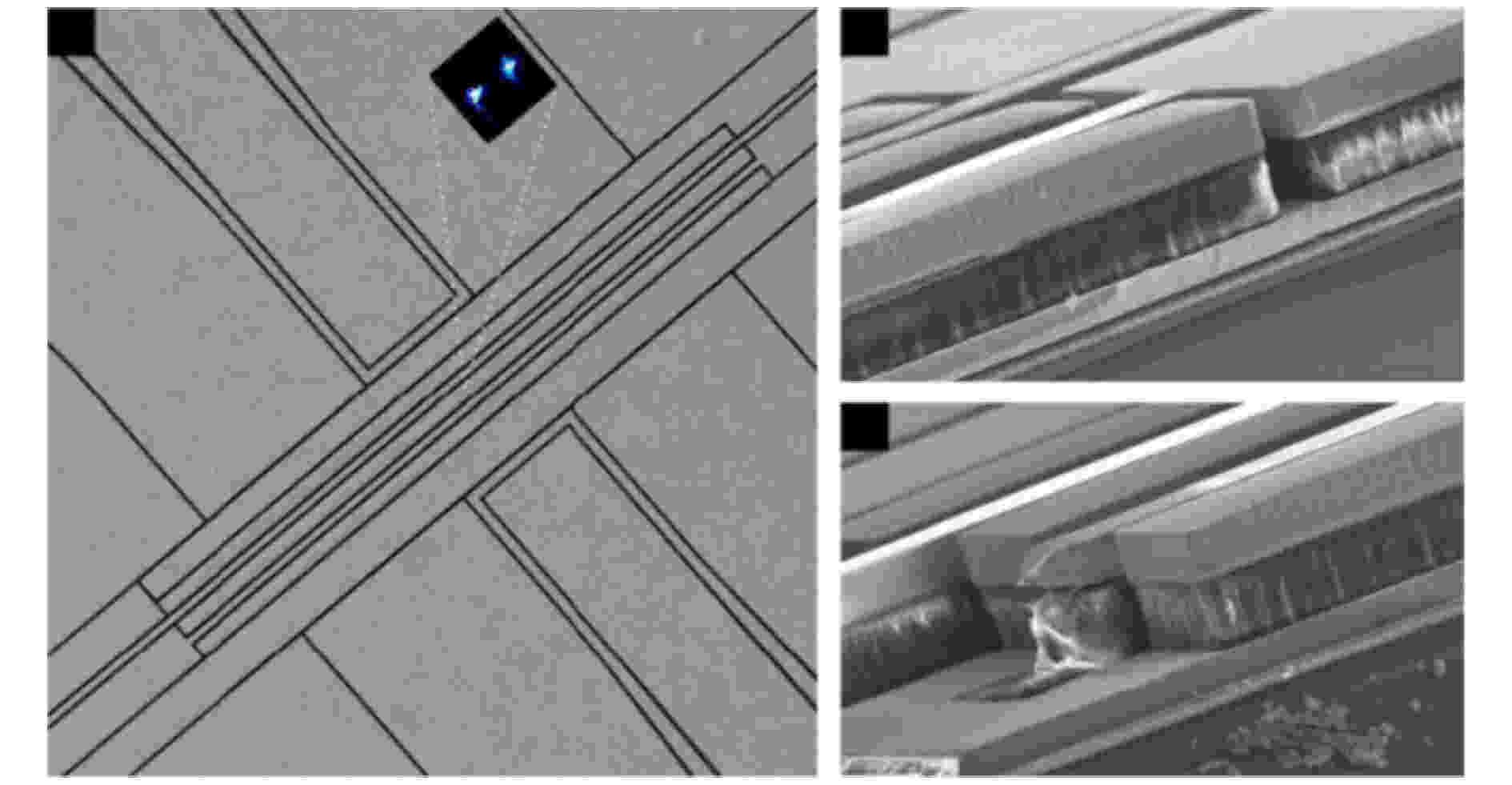

在载流导线制备过程中必须考虑导线的实际载流能力(影响磁阱梯度)、表面平整度(影响激光反射率、电流噪音及势阱起伏)及与基底的附着力(影响芯片在电流加载后发生热失配时的可靠性), 这些都与导线的材质和制备工艺相关. 载流导线一般选用高电导率的Au, Cu等金属. Au结构稳定不易氧化但成本较高且会对Rb原子产生吸附; Cu成本相对较低且在硅通孔(TSV)工艺中已较为成熟, 但Cu相对容易氧化, 如长期暴露在氧环境下则需制备防氧化的介质层, 此举也有助于防止碱金属原子污染金属层降低其反射率, 避免导线之间短路. 为了实现紧束缚的单模原子导引往往要提高导线承载的电流密度, 这通常意味着减小导线的线宽或者增大电流(常常需要在10—20 s的时间内承载几个安培的电流), 均意味着在材料电导率不变的条件下电流密度增大(>107 A/cm2)[36]、热效应增强, 超出了Cu导线的耐受范围[58]. 载流导线还应具备良好的光滑性和均匀性, 以尽量减少横向电流导致的磁阱起伏和冷原子团碎片. 因此, 探寻大电流耐受性强、质量优秀的新导线材料, 对实现高品质的原子导引具有重要的价值. 碳纳米管(CNT)是一种潜在候选, 具有高达109 A/cm2的载流密度(比普通金属高2—3个数量级)和超高的熔点[59], 因能实现电子弹道输运所以可忽略电子散射造成的电流起伏, 有望满足原子载流导线所需要具备的低噪声和弱C-P力等性能. 以色列本古里安大学等单位较早开展了基于CNT的导线型原子芯片研究, 如图10所示. 他们实验展示了基于CNT的双层原子芯片, 提出了将超冷原子从传统的磁阱转移到CNT阱中的理论方法, 认为基于CNT的原子芯片表面隧穿、热噪声引起的自旋翻转以及热效应等势阱损耗都得到了良好的抑制, 论证了CNT材料是一种非常有前景的原子导引材料[60,61]. 此外, Cu的电导率为5.7 × 107 S/m, 而CNT的电导率随手性变化, 通常在106—107 S/m之间, 如果实现CNT与Cu复合材料的载流导线, 既可获得接近于Cu的电导率, 还可以实现比Cu, Au高近两个数量级的载流容量(>108 A/cm2)[62]. 本课题组近年来开发了CNT纺丝阵列与Cu复合致密材料的制备技术, 单根导线载流能力大于107 A/cm2, 并且有望继续提高一个数量级以上满足紧束缚导引的需求[63]. 尽管CNT材料展示出良好的潜力, 但目前还未真正用于芯片上原子导引的问题在于: CNT包含单壁和多壁, 既有半导体型又有金属型和半金属型, 还有不同的手性, 很难实现CNT材料均匀、可控的制备, 未来实用必须解决CNT沿既定方向高一致性、大面积、高可控制备这一难题. 超导材料具有极好的导电性和极低的磁噪声, 且整体工作于低温条件下使得超导材料附近的噪声得到了极大抑制, 因此将其用于原子芯片提升原子寿命也得到了广泛的关注. Hohenester等[64]分析, 在1 μm超导导线势阱中冷原子寿命可达5000 s, 而相同结构的金属磁阱中的原子寿命则只有不到0.1 s. 德国蒂宾根大学Bernon等[65]实验上利用超导铌金属薄膜产生的微势阱制备了3.5 × 105个BEC(350 nK), 全自旋极化态寿命大于4 min, 基态相干时间可以达到8 s, 证实了超导体原子芯片在提升原子相干时间、实现长寿命激发方面的优势.

图 10 (a) 双层CNT原子芯片示意图; (b) 原子力显微镜(AFM)下CNT及其与Z形导线的接触[61]

图 10 (a) 双层CNT原子芯片示意图; (b) 原子力显微镜(AFM)下CNT及其与Z形导线的接触[61]Figure10. (a) Schematic representation of the two layer CNT atom chip; (b) atomic force microscope image of a CNT fabricated and contacted for use as a Z-shaped wire trap[61].

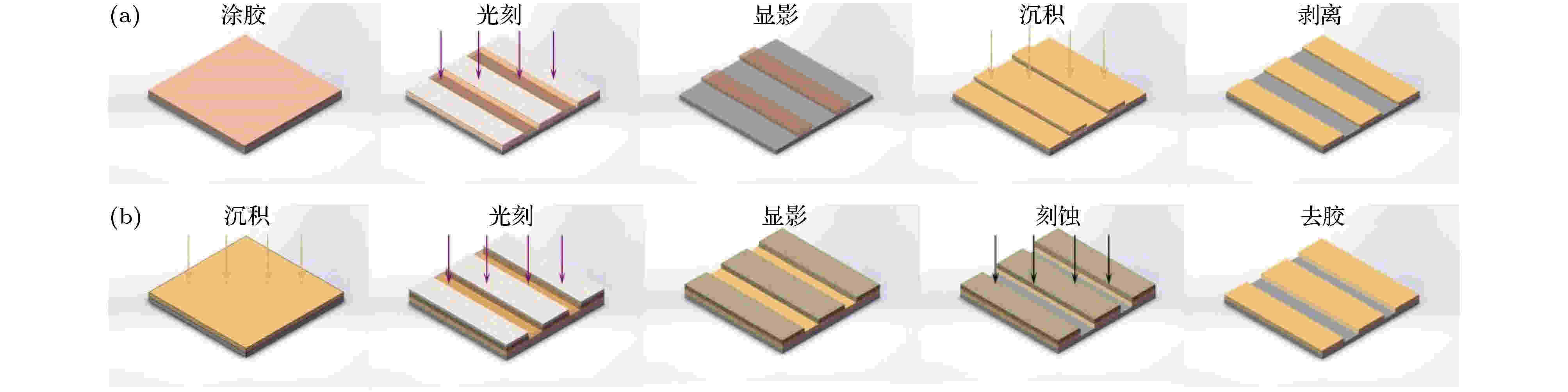

载流导线的成型工艺通常有两种: 1) 采用厚胶光刻制备图案, 生长金属层后剥离; 2) 优先生长金属层, 再制备掩膜层后进行刻蚀, 主要流程分别如图11(a),(b)所示. 其中, 载流导线可采用磁控溅射、电子束蒸发或电镀沉积等方式制备. 磁控溅射生长的薄膜致密、平整、黏附性强, 但速率缓慢、成本较高; 电子束蒸发的平整度较好, 但金属层与基片黏附性较差, 与基底存在热失配时容易脱落; 电镀沉积虽然能快速生长金属导线层, 不过内部晶体结构不均匀, 表面粗糙, 容易氧化, 不利于制备表面平整、内部均匀的原子芯片.

图 11 原子芯片上载流导线的制备方法 (a) 剥离法; (b) 刻蚀法

图 11 原子芯片上载流导线的制备方法 (a) 剥离法; (b) 刻蚀法Figure11. Fabrication methods of the on-chip current-carrying wires: (a) Stripping method; (b) etching method.

量子信息处理等应用往往需要原子芯片具有复杂的线型, 多层芯片可以避免单层芯片中的导线交叉, 势阱的设计也具有更大的灵活性. 制备多层原子芯片最简单的方法是将两个(或多个)单层芯片粘接在一起, 每个芯片工艺完全独立, 一旦出现问题可以单独置换某一芯片, 避免整体芯片的重新加工. 德国Günther等[66]在250 μm厚的基底上利用激光刻出直径约为400 μm的过孔并在其中镀金, 首先实现了两层原子芯片叠加互连. 该方法虽然简单, 但当芯片之间的距离相对较大或者导线布局较复杂时, 很难实现不同层上微结构的精确对准. 后续微纳加工工艺不断发展,涌现出厚膜混合技术、紫外光刻与电子束曝光结合等更适宜制备多层芯片的工艺方法.

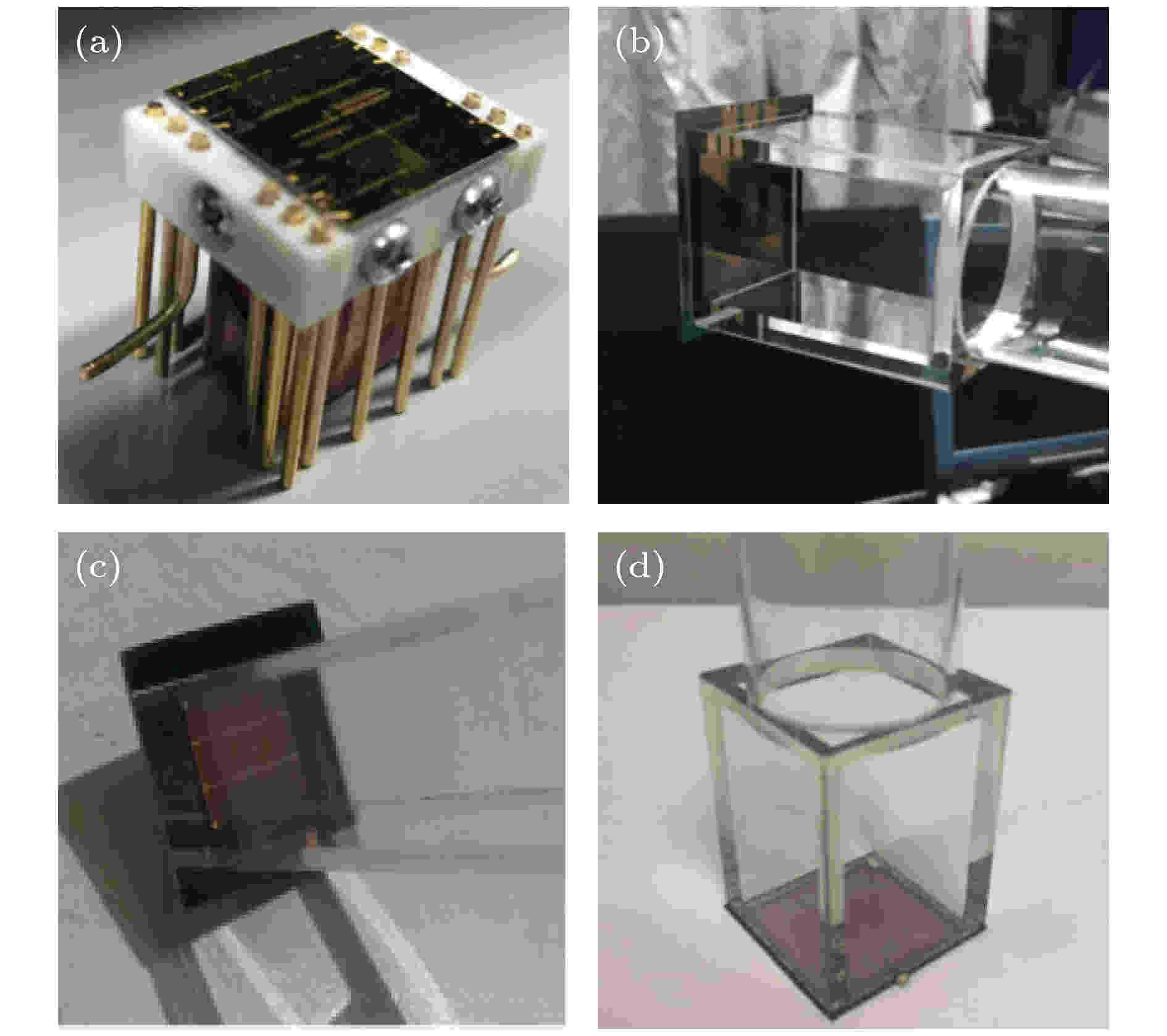

原子芯片制备完成后需要与真空腔体进行封装, 实现其在超高真空环境下的工作. 超高真空封装主要通过如下途径实现: 1) 传统的超高真空封装方式, 即采用真空法兰通过电极将电流接入原子芯片, 这种方式稳定性较高, 但空间体积占用较大; 2) 超高真空胶黏接的封装方式, 即直接将芯片与玻璃池黏合在一起. 由于真空胶的绝缘特性, 芯片电极可以由芯片上表面边缘引出, 气密性可达3.3 ×10–11 Pa·m3/s, 不过该方式存在有机胶体易老化的缺点; 3) 阳极键合的封装方式, 即通过对玻璃池与芯片施加高电压与力压强, 诱发玻璃池与芯片之间成键, 实现芯片与玻璃池的封接. 该技术封接强度高、重复性好、气密性高, 特别适用于采用TSV技术制备的原子芯片, 但存在工艺复杂、条件要求严格, 生产效率低、可能会出现开裂或自动脱落、不适宜用于较长尺寸玻璃池等问题[67]; 4) 低温玻璃焊料封接的方式. 相较阳极键合方式, 此方法工艺简单、封接强度高、密封效果好. 本课题组利用软铅焊键合的芯片与玻璃池样品气密性达8.5 × 10–13 Pa·m3/s, 真空规测试的真空度可达2.18 × 10–8 Pa, 焊缝厚度可控制在50 μm以内, 连接强度大于20 MPa. 图12(a)—(d)是采用不同封接工艺实现的原子芯片超高真空封装, 除图12(c)外均由本课题组与中国科学院上海光学精密机械研究所共同完成[68].

图 12 基于不同封装工艺的原子芯片 (a) 针对传统真空法兰电极接口的芯片封装形式; (b) 超高真空胶; (c) 阳极键合[67]; (d) 软钎焊

图 12 基于不同封装工艺的原子芯片 (a) 针对传统真空法兰电极接口的芯片封装形式; (b) 超高真空胶; (c) 阳极键合[67]; (d) 软钎焊Figure12. Atom chips based on different packaging processes: (a)Traditional vacuum package; (b) ultra-high vacuum adhesive; (c) anode adhesive[67]; (d) soft soldering.

2

3.2.原子芯片的测试

原子芯片的测试主要包括两大类.1) 基础特性测试: 包括原子芯片的基本形貌与粗糙度、导线的电阻、导线间电阻、导线载流能力、芯片表面反射率等. 这些测试可以分别通过电子显微镜、AFM、电流电压源以及角分辨光谱仪等常规设备完成.

2) 磁阱结构测试: 用于验证接入电流时芯片的表面磁场特性并主要关注两个参数, 即空间分辨率和磁场灵敏度. 目前, 能对空间磁场进行测量的有磁强计、超导量子干涉设备(SQUID)、扫描磁力探针显微镜(MFM)、低温强磁场扫描霍尔显微镜(SHPM)和扫描磁阻显微镜(SMM)等方法. SQUID的场灵敏度最高, 噪声水平可低至几fT/Hz1/2, 然而其空间分辨率大概在50—100 μm, 难以分析十几微米导线的磁场分布[69]; MFM可以对空间分辨率在十几纳米的磁场进行测试, 但场灵敏度较低[70], 并且很难对磁场的强度进行定量测量; SHPM基于霍尔效应, 能定量地对空间中的磁场强度进行扫描反映芯片在空间中的磁场分布, 目前最好的空间分辨率可达两百多纳米; SMM基于磁隧道结技术, 是一种相对简便、成本较低的方法, 空间分辨率可到25 μm, 噪声在1 kHz的时候大概为100 nT/Hz1/2, 且可以在室温下使用[71]. Quantum Design公司近期将低温共聚焦显微镜和低温AFM结合, 实现了光探测磁共振成像系统, 可同时达到纳米级空间分辨率和3 nT的磁场测试精度(100 s积分时间), 并已经用于原子芯片的磁场测试中. 尽管如此, 最便捷的方法仍然是直接在芯片上加载冷原子进行成像反演, 可以实现纳特(nT)精度、几个微米的空间分辨率, 能够满足大多数情况下的测试要求[72].

针对原子芯片上微势阱中囚禁的原子团的数目、温度、密度等性质的测试, 可采用荧光成像或吸收成像的方法探测[73]. 荧光成像法收集角有限, 测量的信号较弱, 因此需要设计高信噪比、高放大倍数、低噪声的电流电压转换电路; 吸收成像主要是测试探测光方向上的光功率变化, 具有很高的信噪比, 但对探测光的功率与频率稳定性同样有很高的要求.

2

3.3.原子芯片上冷原子的操控

在原子芯片上加载冷原子进行操控的实验系统一般包括如下部分.1) 超高真空系统. 用于产生原子气体并提供冷原子实验的超高真空环境, 一般可以分为单腔系统与双腔系统. 单腔系统不涉及原子团的转移, 结构相对双腔系统简单; 双腔系统则是在一个腔体内对原子进行抓取后推送至下一个腔室, 既能俘获足够数量的原子又能保持优秀的真空度.

2) 磁场系统. 由多个线圈组成, 主要用于屏蔽地磁场并产生二维磁光阱、三维磁光阱、偏置场所需的磁场, 同时也对真空腔中的原子团进行转移.

3) 光学系统. 用于对激光进行移频、强弱调整、偏振调整后制备冷原子并提供冷原子实验及成像, 包括3D cooling, 2D cooling, Pushing, Pumping, Imaging, Repumping等光路, 以及后期的原子分束与合束光路.

4) 时序控制系统与数据采集系统. 用于控制各个系统在时间上的协同工作, 如整体控制光路的开启与关闭、磁场线圈的开启与关闭、芯片上导线的导通与断开、相机的数据采集时间等, 最后实现对数据的收集与处理.

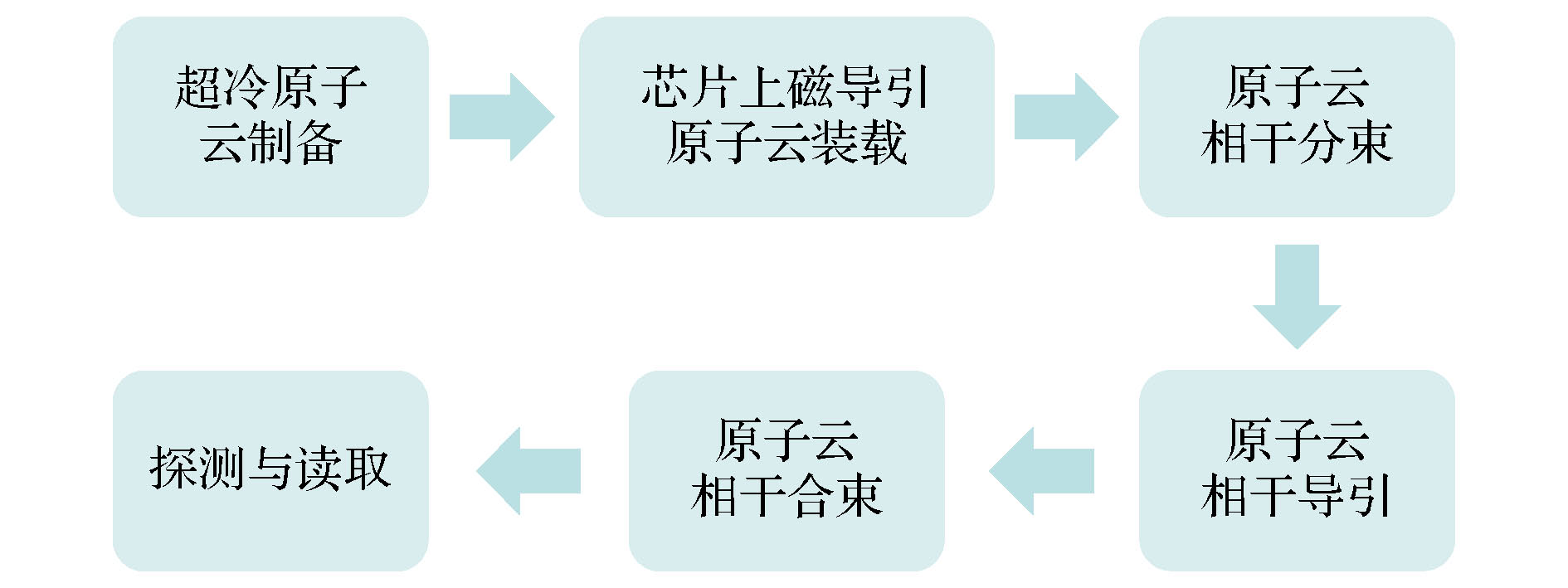

以基于冷原子干涉的原子芯片陀螺仪为例, 其工作流程如图13所示. 首先是利用激光冷却制备超冷原子云. 通过二维磁光阱、光抽运、三维磁光阱完成原子的初态制备后, 采用转移线圈将制备的冷原子团向芯片转移, 并利用mirror-MOT在芯片上对原子团进行抓取, 逐级完成冷原子向U阱、Z阱的转移, 进一步完成原子的蒸发冷却后将原子加载到用于实现冷原子干涉的波导中. 在波导中完成相干分束、传播和相干合束, 旋转信息通过测量相干合束后各动量态上的布居获得. 原子的蒸发冷却也可以在自由空间中完成后向芯片转移, 这样可以降低芯片的复杂度与实验难度, 但自由空间用于蒸发冷却的线圈的功耗与体积都较大, 还需要配备水冷, 因此可根据实验要求选择具体方案.

图 13 基于冷原子干涉的原子芯片陀螺仪基本流程

图 13 基于冷原子干涉的原子芯片陀螺仪基本流程Figure13. Basic process of gyroscope based on cold atom interference on chip.

上述过程面临着一系列挑战性科学技术难题亟待解决, 比如冷原子的高通量制备应满足冷原子数量多和制备时间短两个要求, 而目前国际上BEC的制备时间最快只有几个赫兹, 原子数量约为105个, 距离预期仍有较大差距. 将冷原子云转移到原子芯片上还涉及原子装载的效率问题, 受限于模式匹配问题目前的装载效率仅有约50%. 此外, 冷原子在导引中运动时, 还需要克服原子数损失、热噪声、退相干等不利因素. 其中, 原子数的损失主要由原子之间的碰撞、势阱的变化、势阱的噪声等因素引发; 原子的加热主要指冷原子由于芯片的热噪声、电流噪音等的激发造成的温度上升[17]; 退相干则是存在于所有的量子体系, 也是横亘于冷原子高性能实验全过程的关键问题, 是反映所制备的原子团状态和芯片质量的综合指标, 也是衡量是否能观测到原子干涉现象的直接因素. 原子芯片的典型退相干机制包括[22]: 与冷原子云自身的碰撞散射; 冷原子与原子芯片之间的相互作用; 原子导引自身的不完美; 外界环境或外界操纵激光的耦合等. 这些退相干机制大多并非单独起作用, 往往减弱了其中一种的同时可能会增强其他退相干机制. 因此, 原子芯片上退相干的有效抑制是需要不断深入研究的关键问题.

2

3.4.集成原子芯片

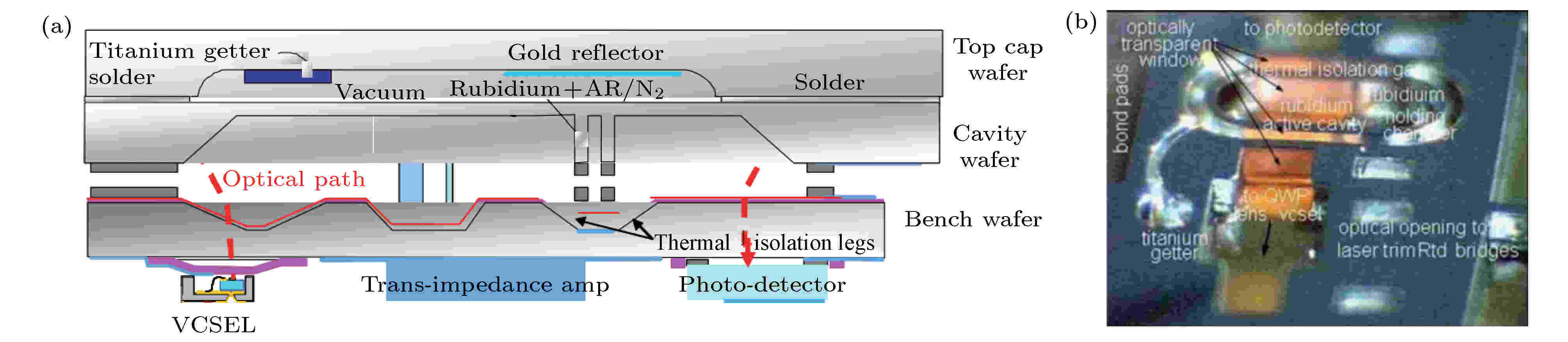

原子芯片自问世起, 科研人员的愿景一直是将其打造为高稳定、高精度、集成化的小型原子研究平台, 并应用于各类精密传感与测量等场景. 因此, 只有将载流导线等表面微结构与不同材料体系的光子/电子微纳器件混合集成, 才可能实现功能强大的集成原子芯片或者原子微系统. 2000年, Folman等[74,75]制作了第一块集成原子芯片雏形, 集成了微MOT、微磁阱和表面磁导线, 实现了中性原子的磁光囚禁、冷却、装载与导引. 随后一系列将磁或者光产生的微阱与导引等集成实现磁光混合型或者全光型原子芯片的工作见诸报端. 除在同一基底上多种微结构的集成外, 采用wire-bonding或者TSV等工艺将不同功能层进行芯片间集成的技术也得到了快速发展. 如美国Honeywell和美国国家标准与技术研究院(NIST)实现了将激光器、反射镜、微真空腔、探测器等混合集成的芯片级原子钟, 如图14所示[76]. 基于相似的技术途径他们还实现了芯片级磁力计. 图 14 Honeywell提出的水平方向集成的芯片级原子钟方案 (a) 原子物理集成部分; (b) 蒸汽室与光路的集成[76]

图 14 Honeywell提出的水平方向集成的芯片级原子钟方案 (a) 原子物理集成部分; (b) 蒸汽室与光路的集成[76]Figure14. Horizontally integrated design for a chip-scale atomic clock physics package: (a) Schematic of physics package and (b) photograph of vapor cell integrated into optical path[76].

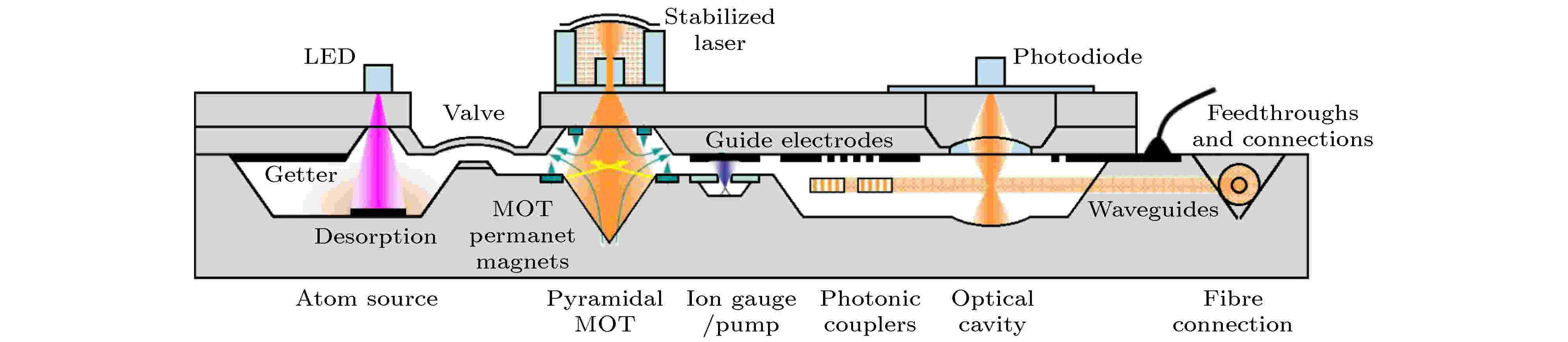

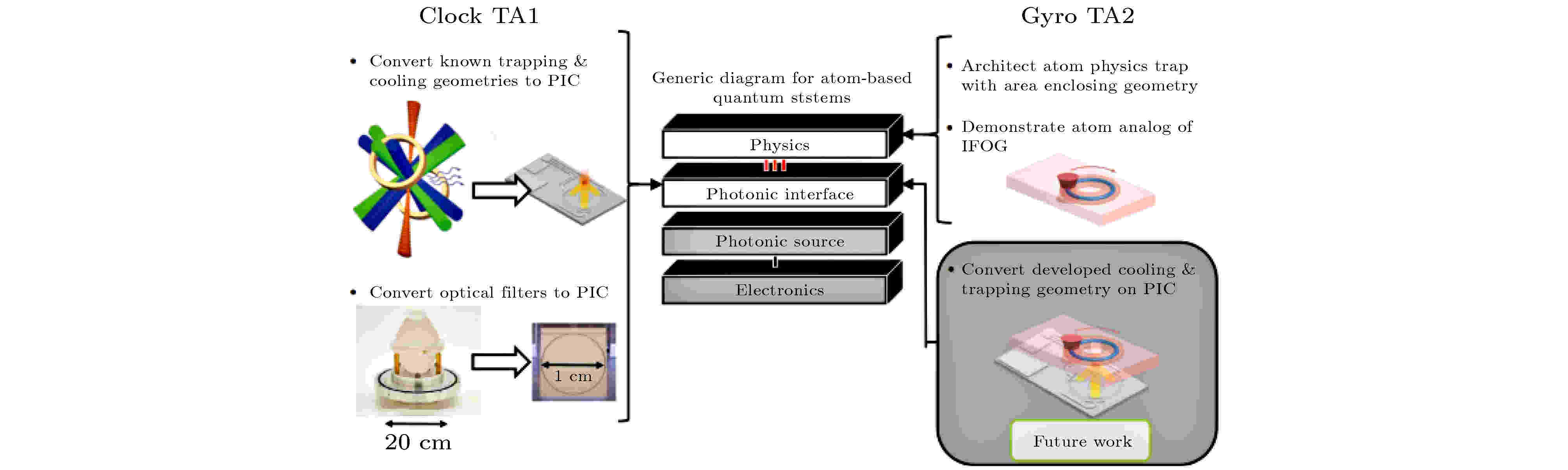

近年, 以色列本古里安大学提出了高度集成化的原子芯片量子陀螺仪构想(理念来源于南安普顿大学Freegarde团队), 如图15所示. 在深刻蚀的基底上集成了微真空系统、微原子源、微真空泵和阀门、单束激光反射式微MOT、微光源、光耦合器、波导和光电探测器等, 具备了传统大型原子系统的所有功能, 且体积只有20 mm × 24 mm × 5 mm[77]. 实现这一构想的技术挑战主要来源于几方面: 一是光学元件和真空系统的小型化、集成化; 二是在同一基底上的异质集成及混合集成; 三是根据不同的应用, 设计具有不同功能、不同技术兼容的集成原子芯片架构. 这些问题的解决需要材料、原子物理器件、原子光学等多层次、多学科技术相互促进、共同发展, 才能实现芯片上光子-电子-原子的深度耦合. 美国等国家和地区也确实在沿袭此思路推动相关工作, 如NIST提出了芯片级集成化的冷原子片上实验室(NIST-on-a-chip), 并正在逐个解决集成原子芯片中的关键使能技术, 本文在4.1节还会对此进行介绍.

图 15 高度集成化的原子芯片量子陀螺仪构想[77]

图 15 高度集成化的原子芯片量子陀螺仪构想[77]Figure15. Futuristic visions of highly integrated atom chips for quantum gyroscope[77].

4.1.各国有关原子芯片技术的计划与项目

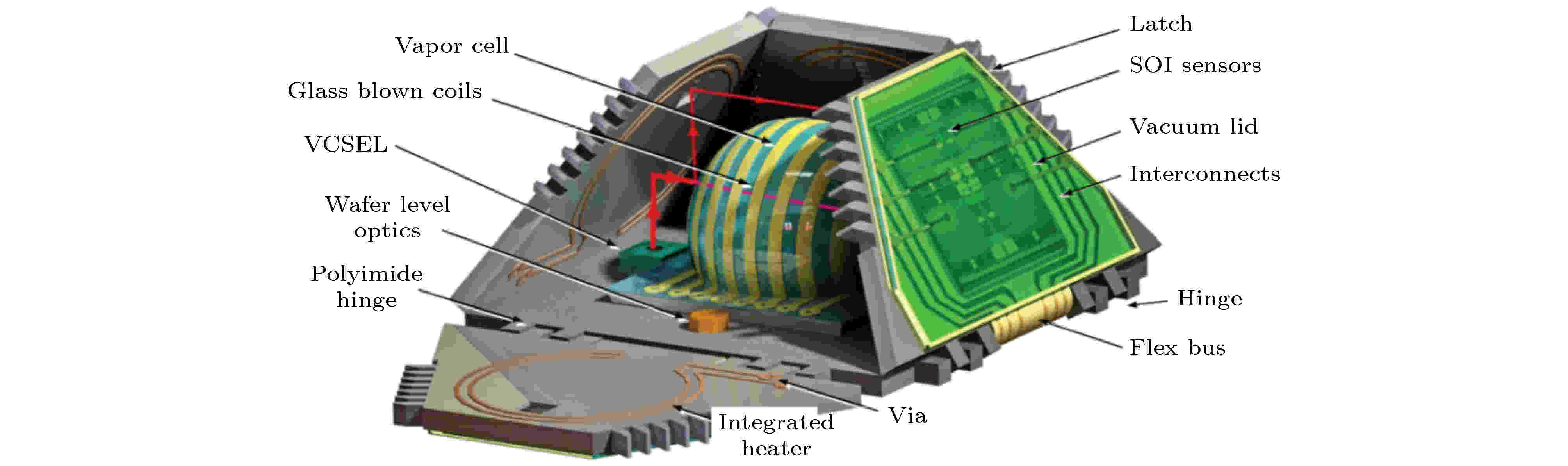

由于原子芯片满足体积(size)、重量(weight)、功耗(power)和成本(cost), 即SWAP-C的苛刻要求, 在授时、定位、导航等领域展现出独特优势, 因而近年来各国与冷原子或量子相关的研究计划几乎都包含了原子芯片相关技术.美国国防部高级研究计划局(DARPA)于2001年启动芯片级原子钟(chip-scale atomic chips, CSAC)研究, 开辟了将芯片微加工与冷原子授时相结合的技术途径. 2010年启动著名的微型定位导航授时计划(micro-technology for positioning, navigation, and timing, Micro-PNT), 主要开发自主的芯片级惯性导航和精确制导技术, 对美国发展微型化原子技术起到巨大的推动作用, 时至今日仍在运行. Micro-PNT包含5个项目, 最重要的部分为芯片级组合原子导航仪项目(chip-scale combinatorial atomic navigator, C-SCAN), 研究高性能原子惯性传感器的小型化制造、算法和协同架构, 包括核磁共振陀螺仪和原子干涉的Sagnac效应陀螺仪两种方案, 最终目标是将原子和固态惯性传感器集成在一个体积不超过20 cm3、功耗不超过1 W的微系统中, 转动精度达到10–4 (°)/h, 线性加速度精度达到10–6 g, 如图16所示[78].

图 16 C-SCAN的概念图[78]

图 16 C-SCAN的概念图[78]Figure16. Schematic scheme of C-SCAN[78].

C-SCAN的指标在实验室中已得到了验证, 但其进一步实用需要小型化、集成化的激光器、光学系统和真空系统等协同发展. 因此2015年DARPA在Micro-PNT计划中增加冷原子微系统项目(cold atom microsystems, CAMS), 主要解决低SWAP-C的原子钟、原子物质波导陀螺仪和加速计所需要的高效窄线宽激光源、高效光学调制器、微型高隔离光学开关、紧凑型低损耗光学隔离器、微电子系统、微型超高真空室和真空泵等关键技术. 2018年DARPA进一步启动原子-光子集成计划(atomic-photonic integration, A-PHI), 致力于发展紧凑型光子集成技术逐步代替空间光学系统, 一方面满足高性能芯片原子干涉陀螺仪和原子钟的使用需求, 另一方面为实现功能齐全、性能优越的便携化导航授时传感系统奠定基础, 如图17所示. 2020年底前A-PHI计划实现原子囚禁与冷却的光子集成芯片, 并且与冷原子钟的架构兼容.

图 17 美国DARPA的A-PHI计划框架

图 17 美国DARPA的A-PHI计划框架Figure17. Framework of A-PHI of DARPA.

美国NIST近年来提出了芯片级原子器件项目(chip-scale atomic device program, CSADP), 目标是开发芯片级的时钟、磁力计、干涉仪、陀螺仪等, 实现时间、频率、距离、质量和力、温度和压力、电场和磁场、电流和电压、流体体积和流量等的精密测量, 最终构筑Nist-on-a-chip, 实现精确的芯片级的量子测量技术[76]. 美国空军研究实验室(AFRL)和美国国家航空航天局(NASA)等机构在最近十余年也对面向传感的原子芯片技术持续投入, 集合了全美超过50家知名大学、研究所和公司参与, 具备了非常雄厚的技术积累.

欧洲对原子芯片技术也非常重视. 2014年法国国家研究署启动了原子芯片惯性传感项目(OnACIS), 旨在利用原子芯片实现超高精度的磁导引型原子干涉陀螺仪, 重点解决原子芯片分束结构、原子芯片基底、原子芯片干涉中的退相干问题等. 同年英国国防部设置量子罗盘项目(quantum compass), 主要研究量子导航和重力成像仪, 核心目标包括将上述系统进行芯片集成与制造. 2015年英国发布的《A roadmap for quantum technologies in the UK》也包含原子芯片的内容, 并认为基于芯片的冷原子传感在10—15 年内会逐步成熟. 近期, 英国量子技术中心(UK Quantum Technology Hub)发布了系列计划, 将半导体材料、量子器件技术、原子芯片架构与制造技术结合, 研发出用于旋转传感和磁力测量的紧凑、低噪声、超真空兼容的原子芯片. 除此, 2016年欧盟提出量子宣言计划(Quantum Manifesto), 计划利用15年左右开发可集成在手机等内部的芯片上量子传感器设备.

我国20多年前就开始从事原子芯片研究, 近些年在量子技术方面有较大投入, 部分研究计划涉及了芯片级原子钟、原子芯片陀螺仪等. 自中国科学院上海光学精密机械研究所率先实现芯片上的BEC后, 中国科学院武汉物理与数学研究所等单位相继实现了芯片上BEC的制备和不同结构的中性原子的磁导引等[17,79], 提出了利用倏逝波和表面等离子体势来囚禁原子的全光原子芯片方案、数字原子芯片方案、激光诱导虚拟磁场阱及阵列方案和原子芯片上冷原子系综量子逻辑门方案等[80]. 但相较国外, 我国专项重点支持原子芯片的研究计划仍然相对较少, 对原子芯片的基础研究与应用进行体系化的整体布局仍然较为欠缺.

2

4.2.原子芯片的应用

近年来, 基于原子芯片或芯片级加工与集成技术的冷原子钟、陀螺仪、加速度计、重力仪、磁力计等精密测量与传感器获得了广泛的关注并逐步走出实验室, 在高精密授时、惯性导航、重力测绘、脑探测等领域得到应用并且展现了优秀的性能, 如表1所示. 此外, 原子芯片可以提供低维量子气体、腔量子电动力学、原子-表面相互作用等基础研究的微纳化平台, 被称为“微芯片上的量子实验室”, 在基础物理研究也有不可忽视的潜力. 其中, 芯片级原子钟、芯片级原子磁力计等应用的核心技术是小型化的原子气室、单模激光器、探测器、光学元器件及其集成技术, 本文不对此做详细阐述.| 应用类型 | 应用领域 | ||

| 基础物理研究 | 国家安全 | 国民经济 | |

| 原子陀螺仪 | — | 航空、航天、航海、 潜艇、导弹导航 | 自动驾驶, 手机定位导航 |

| 原子加速度计 | 广义相对论等效原理验证、行星科学 | 航空、航天、航海、 潜艇、导弹导航 | 自动驾驶, 手机导航 |

| 原子干涉重力仪 | 万有引力常数测试 | 导航 | 煤、石油、天然气等资源勘探、 地下遗迹探测、手机手势识别 |

| 量子计算和量子模拟 | 基础量子物理问题研究 | 密码破译, 信息安全 | 高性能计算 |

| 芯片级原子钟 | 广义相对论等效原理验证、引力波探测、 暗物质探测、精细结构常数变化测试 | 授时, 航空航天 | 地貌测绘等 |

| 芯片级原子磁力计 | — | 潜艇探测 | 矿石探测、人体健康检测 |

表1基于原子芯片的部分应用

Table1.Applications based on atom chips.

1) 冷原子干涉陀螺仪

利用原子德布罗意波干涉效应可以测量万有引力常数、旋转角速度、加速度、重力场梯度等, 是量子传感与精密测量领域的重要手段. 特别是基于Sagnac效应的冷原子干涉陀螺仪具有超高的测量精度(理论精度可达10–12 (°)/h)、灵敏度和分辨率, 对于实现不依赖卫星等外部条件定位的全自主惯性导航具有重大意义. 相对于国内外已有较多研究报道的自由空间冷原子干涉陀螺仪, 基于原子芯片的导引型冷原子干涉陀螺仪在大大减小体积重量的同时还能缩短冷原子的制备时间, 利用光场或磁场与原子的相互作用力抵消原子重力影响, 在导引过程中原子云不容易发生扩散, 具有鲁棒性好、超高精度、可小型化、可集成化、功耗低、重量轻和抗干扰等优点.

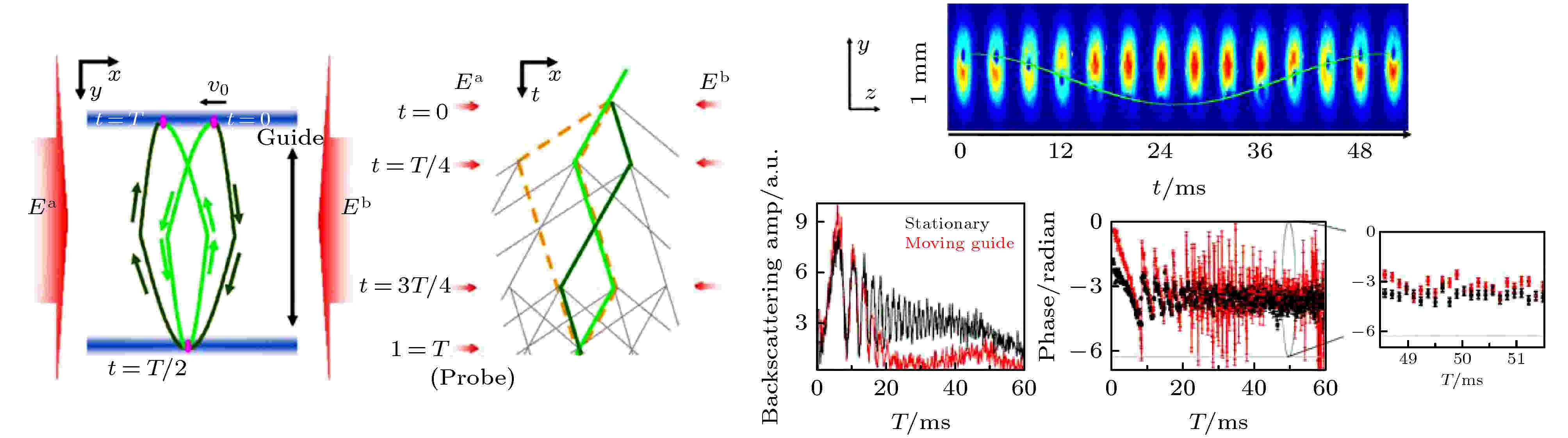

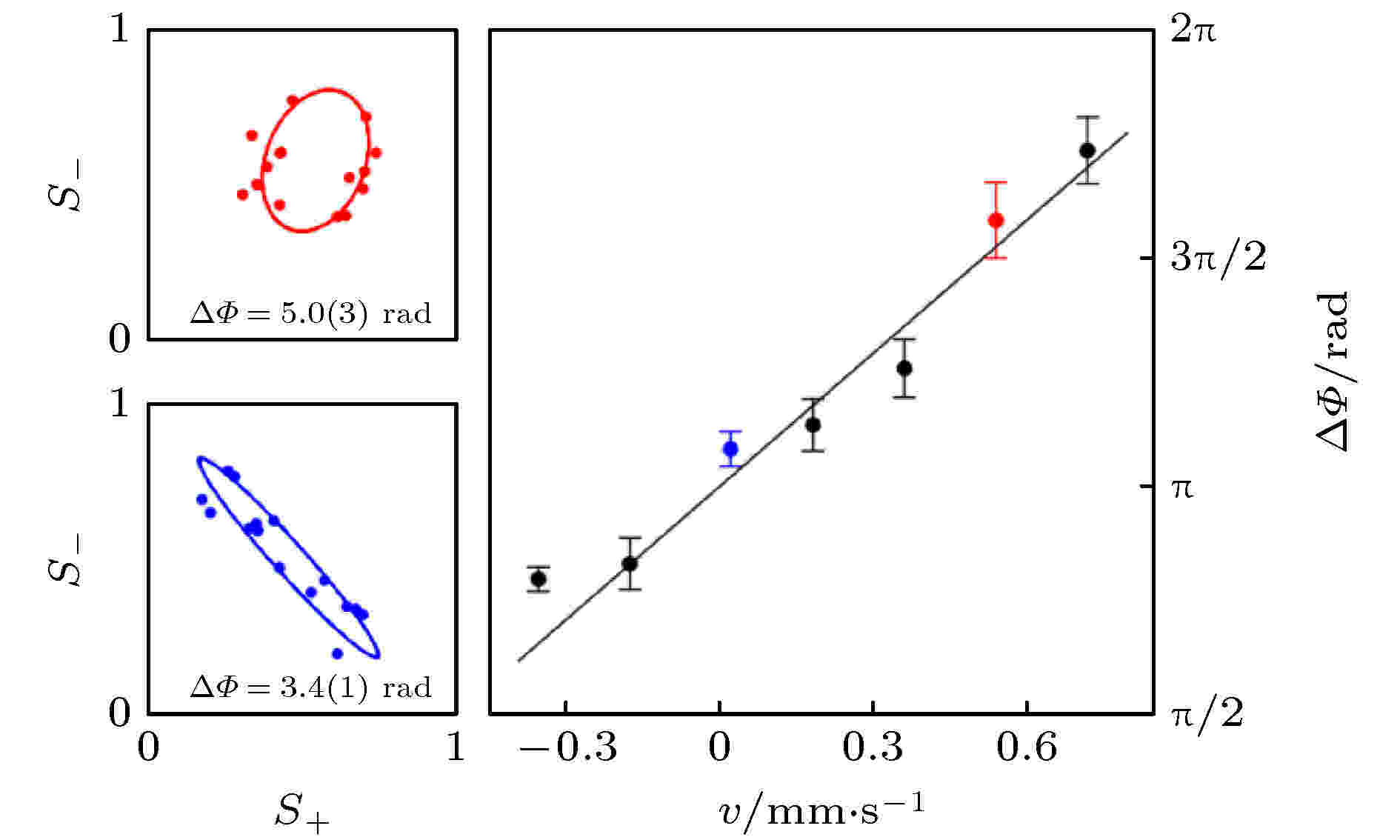

目前国际上有多家科研团队在开展原子芯片上的冷原子干涉技术, 并致力于将其用于旋转信息测量中. 2005年, 美国科罗拉多大学Wang等[54]最早实现了芯片级冷原子迈克耳孙干涉仪, 他们利用波矢沿着磁波导方向的驻波光场实现了芯片上的BEC分束、反射与合束, 并通过磁场梯度与BEC初始速度在干涉仪两路之间引入相移差异调节干涉, 在原子传播10 ms后仍能观察到20%的干涉对比度. 同年, 美国麻省理工大学Shin等[44]在原子芯片上通过使势阱沿紧束缚方向变形成纯磁双阱势实现了Na原子BEC的分束, 从而也观察到了BEC干涉. 德国海德堡大学Schumm等[81]结合静磁阱及射频诱导的绝热双阱势也在原子芯片上实现了BEC分束与物质波干涉. 2006年麻省理工大学Jo等[82]在芯片上射频诱导的双阱势中测量了两束23Na BEC的相对相位, 并通过分束过程中的排斥相互作用将相对原子数起伏压缩到比经典泊松分布小10倍, 实现了10倍于相位扩散时间的相位相干时间增强, 进而初步获得了可用于旋转角速度测量的等效闭合回路. 随后哈佛大学Wu等[83]利用运动的直线型宏观磁导引实现了等效“8”字形的闭合回路冷原子干涉仪, 环路面积0.2 mm2. 该团队预计改进后在厘米级的干涉器件上能实现每秒回路面积达1000 mm2, 转动角速度测量灵敏度达到1 × 10–9 rad/(s·Hz1/2), 如图18所示. 2009年, 美国弗吉尼亚大学Burke等[84]提出基于线性磁阱波导的二维Sagnac效应干涉仪, 通过移动线性磁阱中心来诱导原子沿一个方向振荡, 实现了等效面积0.05 mm2的闭合回路, 闭合回路面积可进一步扩展, 但受到初始速率波动、势阱形貌等因素限制, 未能实现旋转角速度测试. 2012年华南师范大学Yan等[85]提出一种利用对称态依赖的微波电势的芯片上导引型原子陀螺仪理论方案, 在磁导引的自由传播方向上对内态不同的原子进行分离和复合, 并随磁导引的来回移动沿另一个方向平移原子, 有望实现大面积闭合回路的芯片级原子陀螺仪. 2013年, 德国Muntinga等[86]在微重力环境下, 利用“π/2-π-π/2”型Bragg激光脉冲作用于原子芯片微磁阱中下落的BEC上, 实现了原子芯片上的Mach-Zehnder干涉仪. 最新报道他们已经研制了小型化装置, 估计每1.6 s可以产生4 × 105束流的BEC, 微重力环境下l Hz带宽可产生l × 105的BEC原子, 改进真空系统后有望将带宽提升到10 Hz[87]. 2017年美国加州大学伯克利分校Wu等[88]报道了基于金字塔型单激光微MOT(25.4 mm × 25.4 mm × 25.4 mm)的多轴光脉冲原子干涉仪, 利用原子与光相互作用产生的反冲动量实现物质波的相干分束与合束, 实现了对加速度测量精度6 μm/(s2·Hz1/2)、转动角速度测量灵敏度300 μrad/(s·Hz1/2)、倾角测量精度4 μrad/Hz1/2的综合指标. 2020年, 美国弗吉尼亚大学Moan等[89]在TOP阱中操控分束后的BEC (分束前冷原子数目大概104个, 温度约为100 nK), 使其在柱对称环形导引中以相反的方向匀速闭合运动产生Sagnac干涉, 环路面积约为0.5 mm2. 通过使用同步反向旋转干涉仪有效地抑制共模噪声, 首次实验验证了在环形闭合导引上利用干涉相位的变化对转动信息的响应, 干涉可见度达到50%, 旋转测量灵敏度达到8 × 10–5 rad/s, 接近地球自转水平, 如图19所示. 作者认为采用该方案有效闭合面积可以扩展到1 cm2以上, 对转动角速度的测量精度预计可达10–7 rad/(s·Hz1/2)的水平, 有助于推动可实用的芯片导引的原子陀螺仪发展.

图 18 哈佛大学提出的直线形宏观磁导引等效“8”字形的闭合回路冷原子干涉陀螺仪[83]

图 18 哈佛大学提出的直线形宏观磁导引等效“8”字形的闭合回路冷原子干涉陀螺仪[83]Figure18. Schematic of a moving-guide with a ‘folded figure 8’ configuration for creating an atom gyroscope with multiple-turn interfering paths by Harvard University[83].

图 19 美国弗吉尼亚大学基于芯片上闭合环形原子波导实现BEC干涉与转动测量[89]

图 19 美国弗吉尼亚大学基于芯片上闭合环形原子波导实现BEC干涉与转动测量[89]Figure19. The rotational information experimental results of BEC atomic interferometry based on Sagnac effects by University of Virginia[89].

尽管弗吉尼亚大学实现了环形闭合磁导引BEC干涉仪及其对转动的测试是里程碑式的成果, 但该实验采用6个微环形磁线圈, 其构成的柱对称环形磁导引势阱产生的束缚较弱, 原子数目较少, 灵敏度不高, 导引中的BEC原子间的碰撞散射问题一定程度上被弱化. 实际应用中对冷原子干涉陀螺仪的灵敏度要求往往非常高, 面临的环境干扰也较为恶劣, 这就需要将更多原子囚禁到芯片表面的紧束缚势阱中, 此时大密度冷原子团内原子间相互作用产生的退相干效应是不可忽视的. 此外, 除了在环形导引芯片实现稳定的原子干涉与转动测量本身难度就很大之外, 冷原子干涉陀螺仪往往存在带宽和动态范围小的缺点, 还需要通过发展新的原理方案或与其他传统陀螺仪复合的技术方案解决[90].

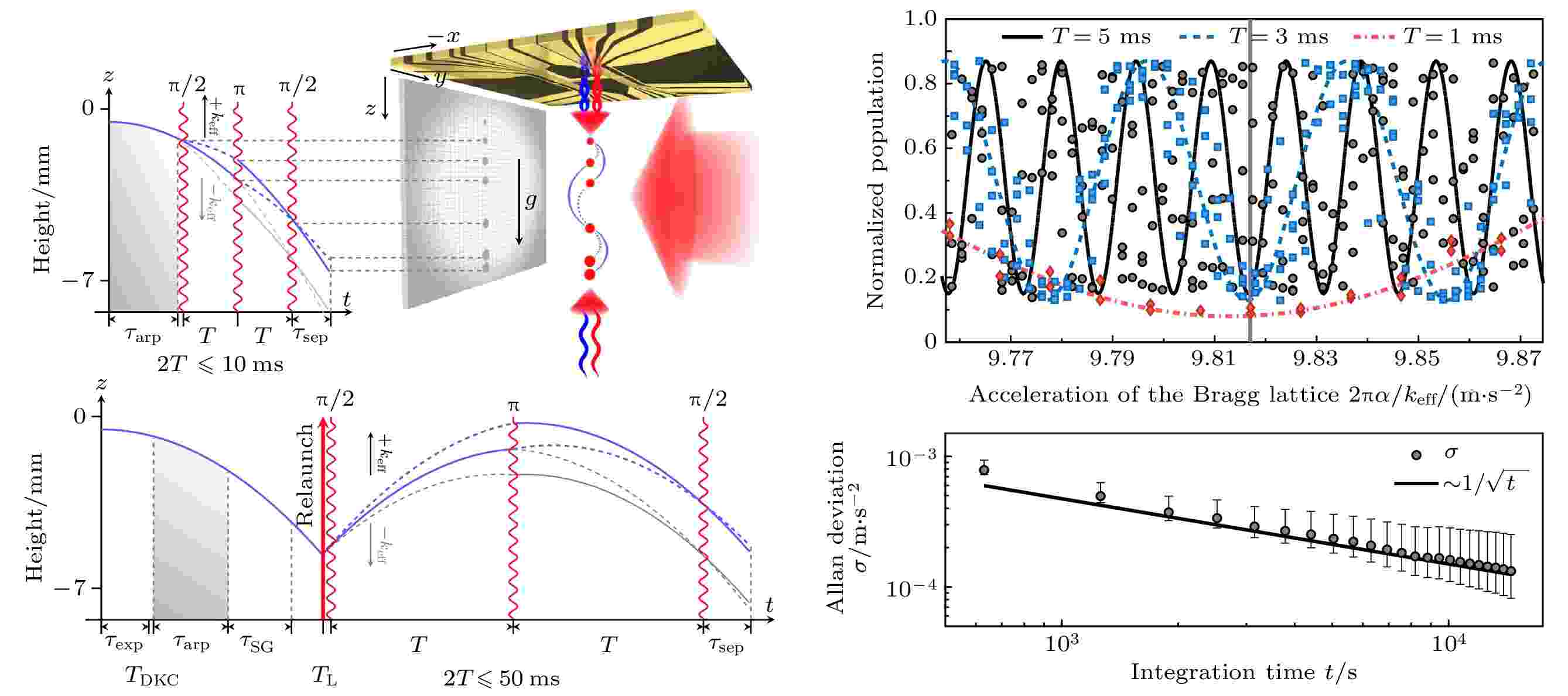

2) 冷原子干涉重力仪

原子芯片上冷原子干涉的另一个重要应用是实现重力仪. 2016年德国汉诺威大学的Abend等[91]报道了基于原子芯片的BEC喷泉式重力仪, 如图20所示. 他们利用原子芯片来进行BEC态制备并将其作为反射镜形成脉冲晶格来驱动布洛赫振荡与双布喇格衍射从而形成马赫-曾德干涉仪, 最终在芯片表面1 cm3空间内实现了精度达到亚μGal (1 μGal = 10 nm/s2)的重力测量, 为高精度绝对重力测量提供了小型化的技术途径. 2019年, 加州大学伯克利分校的Wu等[92]利用中心含通孔的金字塔形MOT将原子冷却到约2 μK, 使铯原子团沿MOT中心通孔自由下落到荧光探测区后再被反射从而构成马赫-曾德干涉仪, 实现了移动式原子干涉重力仪, 灵敏度达到37 μGal/Hz–1/2、长期稳定性2 μGal. 他们用这套系统揭示了海洋潮汐载荷效应、记录了数次远距离的地震, 并以大约0.04 mGal的不确定度现场测量了伯克利山的重力以及地下岩石的密度.

图 20 基于原子芯片的喷泉式重力仪[91]

图 20 基于原子芯片的喷泉式重力仪[91]Figure20. Atom-chip fountain gravimeter[91].

3) 量子信息处理、计算与模拟相关应用

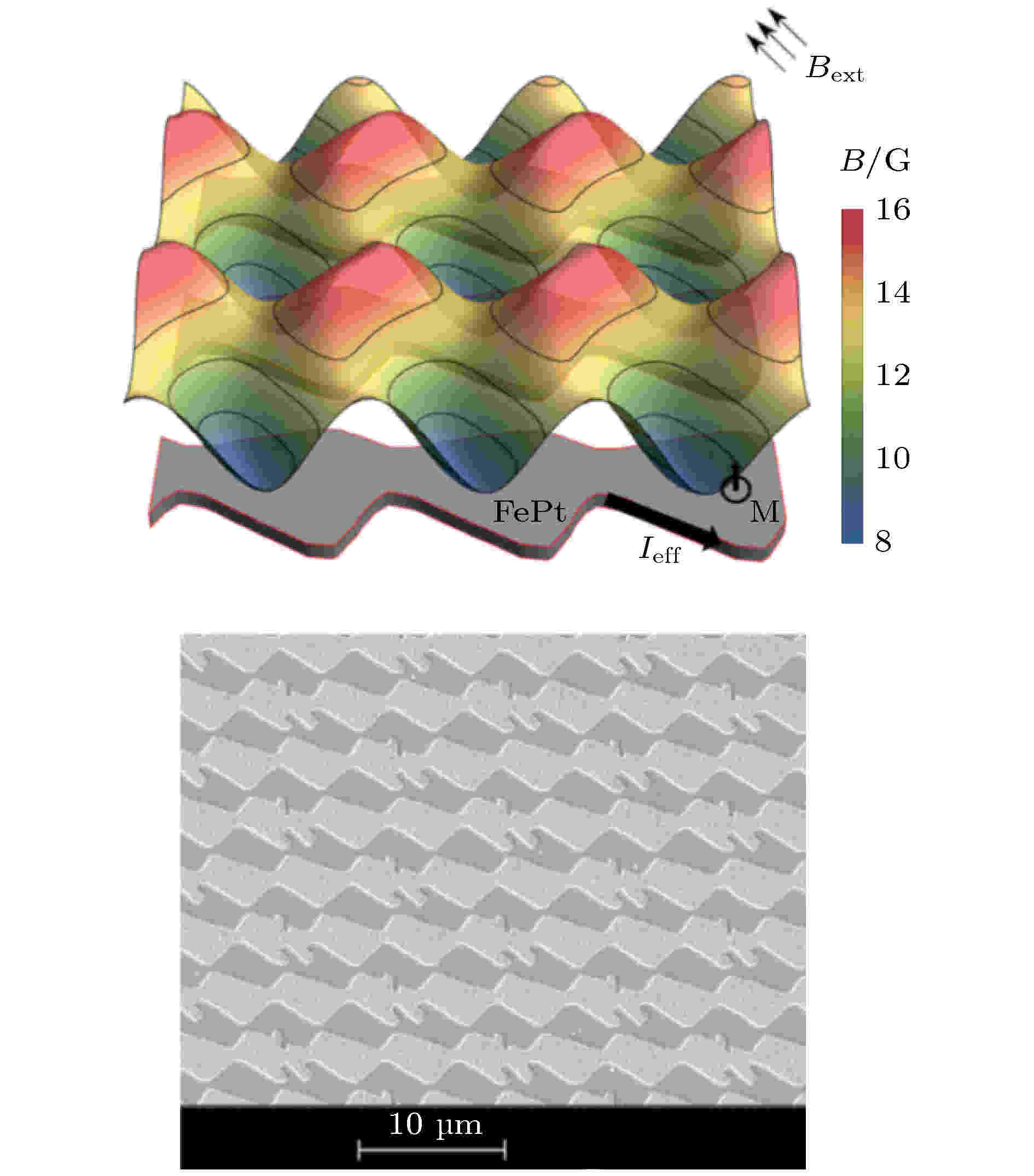

原子芯片为原子光学与量子信息处理、量子计算与量子模拟相结合提供了发展契机. 2002年, 德国海德堡大学Schmiedmayer等[93]报道了基于原子芯片的中性原子量子信息处理方案: 芯片上的交叉导线在偏置场作用下形成静磁阱, 通过调节电流、磁场相关参数可以控制每个阱中装载的原子数目, 对这些原子态进行量子编码就可以实现量子计算, 这是在芯片上实现的第一个量子计算方案. 2007年, 帝国理工学院Trupke等[94]报道了基于原子芯片和光学微腔集成的单原子量子计算方案, 并从理论上指出可以通过测量从光学微腔泄漏的光子来实现原子间的纠缠, 从而实现简单且兼具高鲁棒性的量子计算. 2012年, 普林斯顿大学Houck等[95]对基于芯片级超导回路的量子模拟理论与实验进行综述, 并报道了基于超导回路腔量子电动力学阵列的量子模拟方案. 阿姆斯特丹大学La等[96]近期报道了用于量子模拟的FePt永磁体薄膜蜂巢纳米结构磁晶格原子芯片架构, 如图21所示, 但他们尚未在芯片上实现原子操控和量子模拟功能. 2019年, 德国联邦物理技术研究院和汉诺威大学合作报道了基于芯片上多层离子阱的可扩展量子计算和量子模拟方案, 利用激光冷却在芯片表面35 μm处实现了对9Be+离子的操控, 如图22所示[97]. 总体上, 当前基于原子芯片的量子计算与量子模拟研究还较为初步, 已有报道的工作主要为理论方案研究, 实验工作主要集中于作为量子比特的晶格结构设计与制备.

图 21 用于量子模拟的FePt永磁体纳米磁晶格原子芯片[96]

图 21 用于量子模拟的FePt永磁体纳米磁晶格原子芯片[96]Figure21. The magnetic potential in arbitrary units above an magnetized patterned layer of FePt[96].

图 22 联邦物理技术研究院和汉诺威大学合作报道的离子阱芯片[97]

图 22 联邦物理技术研究院和汉诺威大学合作报道的离子阱芯片[97]Figure22. Multilayer ion trap chip by Germany[97].

4) 其他精密测量应用与基础研究

冷原子的状态与原子芯片上导线产生的磁场息息相关, 因此可以利用监测冷原子的状态来进行高灵敏度的电场和磁场传感. 瑞士的Treutlein团队[98]使用原子芯片上的BEC作为扫描探针, 以微米的分辨率绘制出芯片表面的微波场, 场灵敏度达77 pT/Hz1/2. 此外, 里德伯原子具有大极化率、低场电离阈值和大电偶极矩, 对外部电磁场十分敏感, 可以用来测量微波电场强度的微弱变化, 目前利用原子芯片技术已经获得了优于0.04 V/cm的测量精度, 但比自由空间的里德伯原子测量微波电场的性能仍然有数个数量级的差距[99].

在加深对量子力学的认知、推动基础物理研究方面, 冷原子芯片也逐步发挥着重要的作用. 2010年, 慕尼黑马克思-普朗克实验室第一次在原子芯片上实现多体量子纠缠——自旋压缩态. 这一成果对实现更高精度的芯片级冷原子钟和冷原子干涉仪提供了重要指导, 也有助于理解多体量子关联[100]. 另外, 操控微重力下的超冷原子可以检验爱因斯坦等效原理、研究量子力学在宏观尺度上的有效性以及探究暗能量和暗物质. 近日, 加州理工学院喷气推进实验室(JPL)和NASA的研究人员在《Nature》上发表了重要论文, 借助国际空间站的冷原子实验室(cold atom laboratory), 他们在原子芯片上利用射频蒸发冷却实现了BEC, 获得了20 s的超长寿命以及230 pK的原子温度, 证明了微重力环境对冷原子实验的优势, 如图23所示[101]. 除上述进展外, 原子芯片对于研究量子物理中退相干、无序、非线性和低维物理中的原子散射等基础问题也提供了新的视角和研究手段, 例如原子芯片与最近发展起来的数字微镜DMD技术相结合可实现对一维势阱的有效调控, 为未来一维体系中研究诸如无序导致的Anderson局域、非晶体系以及其他晶格模型的精确量子模拟提供了新的平台[102].

图 23 JPL和NASA发射到空间站的原子芯片[103,104]

图 23 JPL和NASA发射到空间站的原子芯片[103,104]Figure23. Atom chip launch to the space station by JPL and NASA[103,104].

5.1.亟待解决的问题

经过不懈的努力, 原子芯片研究取得了长足的进步, 成为原子光学与量子光学的理想研究平台之一, 但目前仍存在一系列科学技术难题亟待解决.1) 理论方面: 第一是重点研究原子芯片上的各类原子损耗、热噪声及相干性问题, 揭示芯片材质、几何形貌、原子云特性以及环境因素与相干性的关联, 阐明冷原子内态、外态相干性在初态制备、装载、分束、导引、合束等操控过程以及测量中的演变, 丰富原子芯片表面效应以及冷原子中量子少体与多体物理的基本物理认知; 第二是着力拓展针对不同应用目的发展原子芯片操控冷原子的新方法和新理论; 第三是从量子力学的基本测量原理出发, 研究各种探测的理论方案, 为基于原子芯片的量子传感与精密测量性能提升提供理论依据.

2) 芯片设计与实现技术方面: 一方面需要提出满足不同需求的紧束缚微势阱以及单模原子导引的优化设计方案, 能够在理论上实现高密度BEC的囚禁与相干操控; 另一方面需要研制高载流能力、高电导率的高质量载流导线, 以及具有高散热性和高质量绝缘层的基底, 同时还需要开发微米尺度甚至纳米尺度的原子芯片新工艺、解决微纳尺度结构的精准构造、纳米尺度薄膜的高精度制备以及多层芯片间微结构的对准等工艺技术. 针对集成原子芯片的发展需求, 还应发展复杂原子芯片的设计方法, 并推动微纳尺度窄线宽激光器、微磁/微光/磁光阱、微型化冷原子气室和探测系统及其他新颖原子光学器件的发展, 探索原子光学器件混合集成或者单片集成技术以及封装互联技术[11].

3) 原子芯片实验方面: 根据加速度计与陀螺仪等实际应用需求, 芯片上冷原子的产生频率应至少到100 Hz以上, 因此原子芯片上高通量高效率冷原子制备是与应用紧密相关的重要问题. 另外, 实验中常常将自由空间冷却的原子云转移装载到原子芯片上, 此时则需要解决装载过程中势阱的尺寸匹配、模式匹配、中心位置重合、形状和大小匹配等技术难题. 在原子操控过程中如何在实际应用环境中保持良好的相干性, 削弱热噪声和原子损耗的影响, 同时实现对芯片上的原子及其量子态的高灵敏度、高精度探测也是非常重要的研究课题.

2

5.2.未来展望

得益于基础物理与材料、微纳加工与集成技术的突破, 尽管原子芯片至今只有20余年的历史, 但已经获得巨大的突破: 从操控中性原子到里德伯原子、分子、离子, 从载流导线、永磁体到偶极阱和表面等离激元, 从金属、硅等材料到磁性材料、超导体、CNT等, 从外部检测到片上单原子检测, 从单层芯片到多层芯片乃至集成芯片, 从单体到多体物理问题, 从表面科学到量子力学基础研究······原子芯片逐步具备取代大型的传统装置的能力, 提供了原子-光子-电子相互作用的片上接口, 在诸多领域得到成功的应用并展示出独一无二的优势. 未来, 原子芯片有望根据需求定制设计, 集成冷原子源、原子单模相干导引、纳米尺度势阱、移动势和原子态探测器等模块, 成为功能强大的原子量子态操控芯片化平台, 助力量子精密测量、量子传感、量子信息处理等技术革新性跨越以及量子物理基础认知的更新.感谢兰州大学物理学院安钧鸿教授和中国科学院物理研究所王如泉研究员提出的宝贵建议, 感谢上海光学精密机械研究所周蜀渝副研究员以及张海潮研究员长期以来的大力帮助!