RRAM的优点之一是它的高集成度,这意味着某个阻变单元产生的焦耳热对其相邻阻变单元将产生影响。由于RRAM对热敏感,这种热影响所导致的热串扰问题会使RRAM的保持(retention)特性变差。为了延长RRAM的保持时间,人们在材料和电路层面上做了很多改善[1-4],而在算法层面的研究相对比较缺乏。

本文论述了一种热通量压缩(Thermal Flux Compression,TFC)算法,通过该算法降低了RRAM写入过程中产生的焦耳热,减弱了RRAM中的热串扰问题,从而增加了RRAM的保持时间,增强了RRAM的可靠性。

1 焦耳热对RRAM的影响 在RRAM的写过程中,导电细丝的形成和断裂是其阻值发生变化的根本原因[5-11],而焦耳热在导电细丝的形成和断裂过程中起到了关键作用[12-14],特别是在复位(Reset)过程中由于阻变单元处于低阻态(Low Resistance State,LRS),流过其上的电流较之于高阻态(High Resistance State,HRS)时更大,产生了更多的焦耳热[15],同时也正是焦耳热促进了阻变单元从LRS转变为HRS[16]。

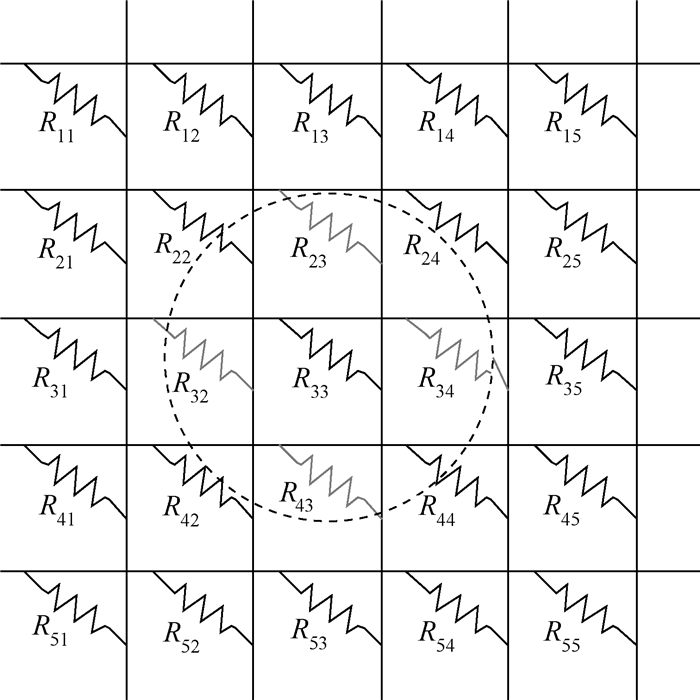

RRAM最大的优点之一就是高集成度,在高集成度的条件下,特别是三维集成下,相邻阻变单元靠得非常近[17-19],由于热具有传导性,并且焦耳热在阻变单元的置位(Set)和Reset过程中扮演了重要的角色,过多的焦耳热会导致阻变单元发生错误翻转,即相当于发生了过写(Over Write)[12]。当某一个阻变单元发生频繁写操作时,特别是发生Reset操作时,其产生的热会发生累积并传导到相邻的阻变单元,这样该阻变单元产生的热就会影响相邻单元的阻态,导致热串扰问题。如图 1所示,当阻变单元R33发生Reset操作时阻变单元的温度瞬间可达到1 000 K左右[14-15],其产生的热量将会传导到相邻单元,诸如R23、R32、R34和R43等阻变单元都会受到焦耳热的影响。当R33进行频繁的Reset操作时,其相邻的阻变单元就如同置于高温烘焙的条件下,其保持特性将会急剧下降[20-21]。RRAM中的热串扰问题最终会导致阻变单元的阻态发生错误的翻转,降低了RRAM的可靠性,这种情况在高集成度,特别是三维工艺下尤其严重。

|

| 图 1 RRAM中的热串扰问题 Fig. 1 Thermal crosstalk in RRAM |

| 图选项 |

2 TFC算法 定义写入数据流从软件层发出通过存储器写电路后最终在RRAM中真实产生的焦耳热热量为写入数据流过程的“热通量”,注意这里的“热通量”和通常意义上的热通量不是同一个概念,这里所述的“热通量”为一个标量,下文所述“热通量”均为该概念。

不同于Flash,RRAM写前不需要进行擦除操作,因此当对处在LRS的阻变单元进行Set操作时,即对“1”进行写“1”操作会发生不必要的过写操作,对“0”写“0”同理。过写操作不仅会造成功耗的浪费,更严重的是可能会发生Over Set和Over Reset导致阻态错误翻转,其根本原因也是过多的焦耳热造成的[17]。RRAM的写电路使用了自适应写模式(Self-Adaptive Write Mode,SAWM)[4]技术后可以消除上述问题,当阻变单元存储为“1”时,若对其进行写“1”操作,写电路会立即关断写脉冲,对“0”写“0”同理,即只有写过程中需要发生阻态翻转,写电路才会对阻变单元加相应的写电压,阻变单元才会产生焦耳热,这就是“热通量”是真实产生的焦耳热热量的含义。因此不同于Flash,RRAM写入数据产生的热通量不仅和写入数据流本身有关,还和原始存储数据有关。

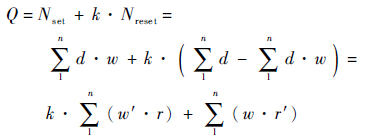

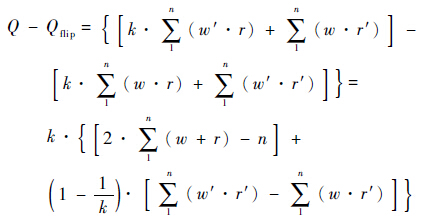

设n位写入数据流为w[n:1],简记为w,存储器中原始存储的数据为r[n:1],简记为r,n位全“1”数据流为e,Set操作产生的焦耳热量为单位1,Reset操作产生的焦耳热量为k(k>1),写入数据流和存储器中原始存储的数据的差异向量定义为d,w的各位取反为w′,r的各位取反为r′,Set的操作数记为Nset,Reset的操作数记为Nreset,Q为写入数据流后产生的热通量(记单个Set操作单元产生的热量为1),各位异或操作记为“+”,则有

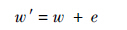

| (1) |

| (2) |

| (3) |

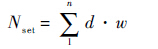

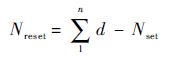

Nset和Nreset分别为

| (4) |

| (5) |

最终得到写入数据流的热通量为

| (6) |

显然当r不变时,Q值取决于w,定义w的各位取反为对w进行的一次翻转编码。对写入数据流向量w进行各位取反即翻转编码后,通过同样的推导可得到写入数据流翻转编码后的热通量为

| (7) |

因此可得翻转编码判别式

| (8) |

式(8)若大于0,说明经过翻转编码后热通量减小了,热累积效应得到减弱;否则说明翻转编码增加了热通量。式(8)中第1个中括号内的表达式代表写入的数据流和原始存储数据的差异数量,如果超过了一半则该中括号内表达式的计算结果为正,否则为负;第2个中括号内表达式代表写入翻转编码的数据流后存储单元中发生“0”到“1”变化的数量和写入未翻转数据流后存储单元发生“0”到“1”变化的数量之差,即翻转编码后真实的Set操作的增加数,该值也可能为负。称(1-1/k)为flip因子,由于k>1,显然flip因子为正实数。综上,式(8)说明对于一个写入数据流,若其与对应的原始数据的差异越大,且翻转数据流后真实Set操作增加的越多,那么翻转数据流后降低的焦耳热就越多。

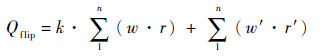

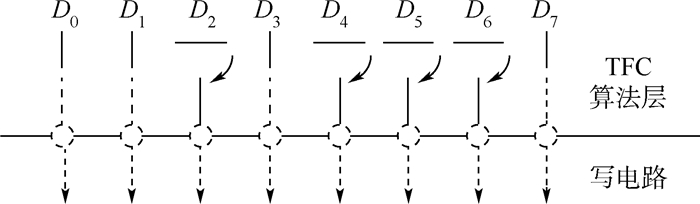

在上述数学分析的基础上,在RRAM写电路之前加入TFC算法层。在写电路进行写操作之前,TFC算法层会读取写操作地址对应存储器中的阻变单元的数据r,根据r和写入数据流w进行式(8)的计算决定是否对写入数据流进行翻转编码。如图 2所示,假设64位写入数据流被分成了8个数据块D0~D7,每个数据块对应8 bit数据,TFC算法层会并行对8个数据块进行翻转编码判别式的计算,若判别式小于0,则允许数据块直接通过TFC算法层进入写电路如D0、D1、D3和D7,否则需要对数据块进行翻转编码操作如D2、D4、D5和D6,翻转后的数据块才能够通过TFC算法层。

|

| 图 2 TFC算法示意图 Fig. 2 Schematic diagram of TFC algorithm |

| 图选项 |

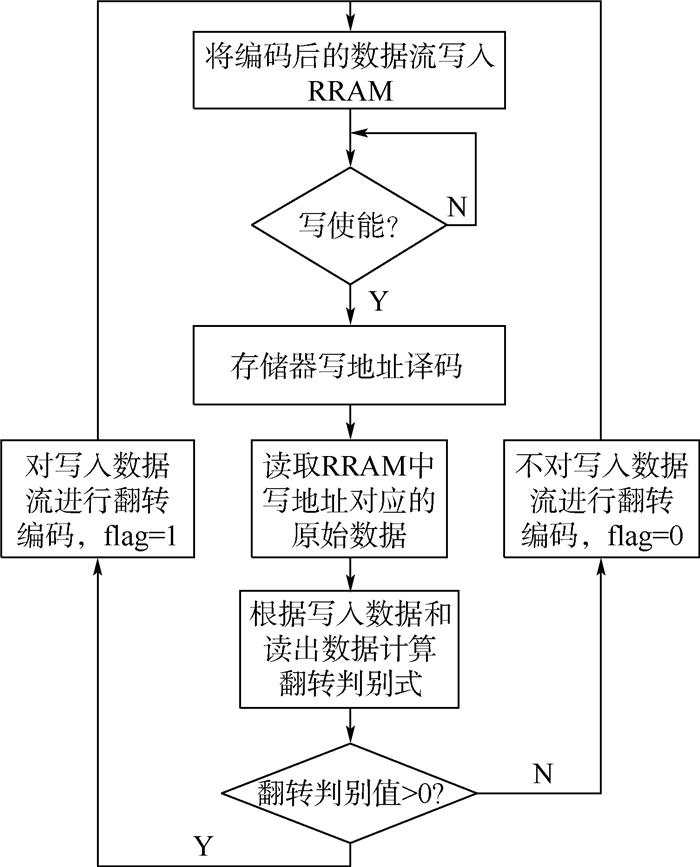

图 3为TFC算法流程图,具体实施方法如下:

|

| 图 3 TFC算法流程图 Fig. 3 Flowchart of TFC algorithm |

| 图选项 |

1) 在RRAM存储器外围写使能的情况下,TFC算法层并不立即传输写使能信号给写电路,而是让写电路首先进行写地址译码,定位要操作的阻变存储器单元。

2) TFC算法层接管上层给出的写使能信号:缓存上层给出的写使能,写电路不工作,并使能读电路。

3) TFC算法层读取1)中定位的阻变存储器单元的数据。

4) TFC算法层对写入数据流和读出数据流进行分析,计算翻转判别式。

5) TFC算法层根据翻转判别式的计算结果选择是否对写入数据流进行翻转编码操作,并配置flag位。

6) TFC算法层关闭读电路使能,重新将上层的写使能信号发送给写电路,并将最终的写入数据流和flag传递给写电路。

7) 写电路完成数据流和flag写入操作。

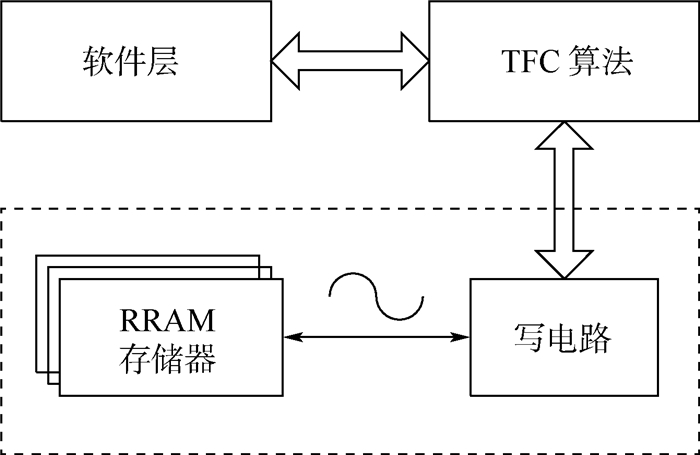

TFC算法在原始写入数据流和翻转编码后的数据流之中选择产生热通量较小的一个通过算法层,从而降低了RRAM写入过程中产生的焦耳热。TFC算法要付出的代价是对每一个数据块都要加一个标志位,用以表明该块是否进行了翻转编码,以便将来读取数据时能够正确译码。另外TFC算法在传统的写过程中加入了读过程,这会导致写过程速度有所降低,所幸的是RRAM的读过程时间只有写过程的1/40左右[22],因此其对写过程的速度影响很小,TFC算法本身的时延代价将在第3节中讨论。TFC算法的可移植性好,如图 4所示,TFC算法可以在软件层中实现,可以嵌入到操作系统的缓冲区算法中;也可以在硬件层中实现,可以在写电路之前加入一层数字电路实现的TFC算法层,TFC算法可以根据实际情况选择在不同的层面实现。

|

| 图 4 TFC算法在系统中的位置 Fig. 4 Position of TFC algorithm in system |

| 图选项 |

3 仿真结果和讨论 TFC算法采用Verilog硬件描述语言实现,并在vcs上进行了功能验证,使用MATLAB进行了数据处理。以下是详细分析过程。

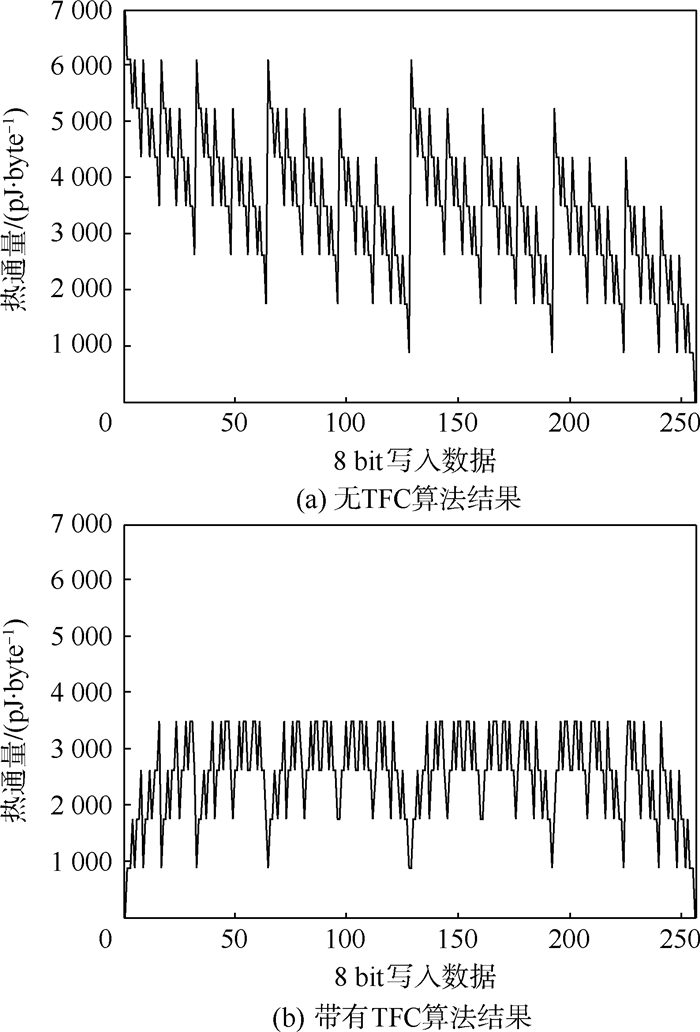

热通量的计算是TFC算法的核心,它是读出数据r、写入数据w、Reset操作焦耳热权重k和数据块位宽n的函数,首先固定变量k和n,之后再对它们进行讨论。选取数据块以字节为单位,即n=8,k则参考文献[4]中给出的Reset和Set操作所产生的焦耳热进行计算得到,即Reset操作焦耳热为871 pJ/bit,Set操作焦耳热为159 pJ/bit,则k≈5.48。

图 5是RRAM forming后遍历写入256个8 bit数据得到的热通量仿真结果。图 5(a)是无TFC算法的结果,热通量分布主要集中在1 000~6 000 pJ/byte范围内,且3 500 pJ/byte以上部分占据了50%左右;图 5(b)是带有TFC算法的结果,热通量主要分布在3 500 pJ/byte以下。从图 5(a)和图 5(b)的对比来看TFC算法有效地压缩了热通量。

|

| 图 5 RRAM forming后写入8 bit数据热通量值 Fig. 5 Thermal flux value with writing 8 bit data after forming in RRAM |

| 图选项 |

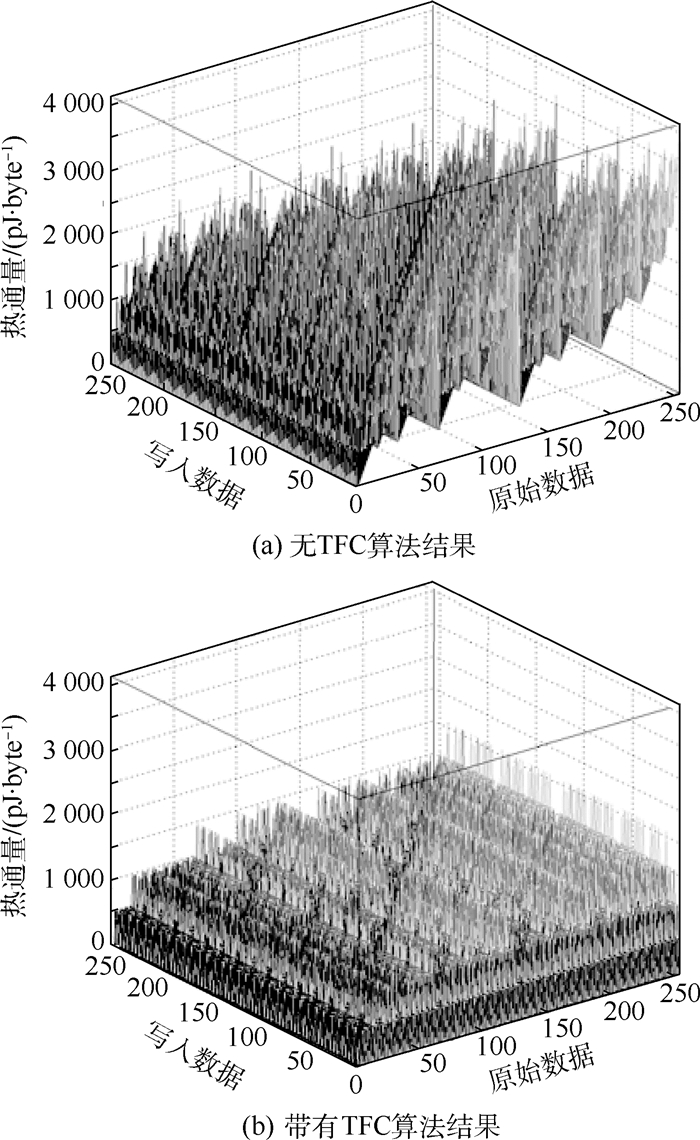

图 6是对RRAM存储的原始数据(opriginal data)和写入数据(write data)以字节为单位数据块进行的全遍历热通量计算仿真。图 6(a)是无TFC算法的仿真结果,图 6(b)是带有TFC算法的仿真结果,显然和图 6(a)相比,图 6(b)中的热通量整体得到了压缩,且TFC算法优化后的热通量最大值不超过4 000 pJ/byte。

|

| 图 6 单字节数据块遍历写入热通量值分布图 Fig. 6 Distribution diagram of thermal flux value of ergodic write in single byte block style |

| 图选项 |

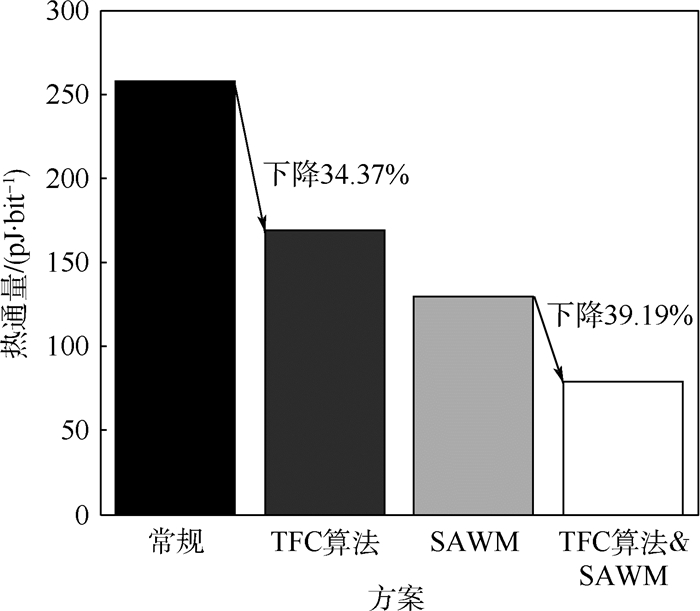

图 7是对单字节数据块遍历写入热通量求单比特热通量平均值的仿真计算结果。计算结果表明带有TFC算法的RRAM写入方案比无TFC算法的写入方案产生的热通量平均减少34.37%;当写电路使用SAWM[4]后,写电路会减少40%左右的热通量,而TFC算法在这个基础上还能够在算法层平均减少39.19%的热通量,从而在整体上更大程度地减少了RRAM存储器中的焦耳热热量。因此不管写电路是否使用了SAWM技术,TFC算法都能够减少30%以上的热通量。

|

| 图 7 TFC算法热通量压缩量图 Fig. 7 Diagram of compression amount of thermal flux with TFC algorithm |

| 图选项 |

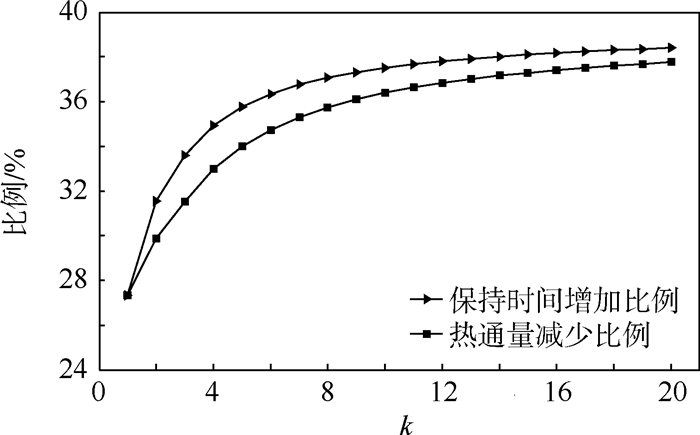

在SAWM基础上使用TFC算法之所以能够减少更多的热通量是因为SAWM使得k值变得更大,在SAWM下,k值约为354.11,而无SAWM情况下k值约为5.48。如图 8所示,对于单字节数据块平均热通量降低百分比在k值大于2之后便超过了30%。由此可见,虽然RRAM由于材料的不同、写入方式的不同等因素会导致k值的不同,但是TFC算法具有良好的适应性,k值大于2的RRAM存储器使用TFC算法就可以平均减少30%以上的热通量。图 6也说明了该问题,虽然写电路使用SAWM技术后k值达到了354.11,而没有使用SAWM的情况下k值只有5.48,k值降低了98.45%,但是TFC算法的热通量压缩比例只是减少了4%左右。

|

| 图 8 保持时间增加比例和热通量减少比例随k值变化曲线图 Fig. 8 Graph of variation curves of retention time increased percentage and thermal flux reduced percentage with k |

| 图选项 |

由于在RRAM中阻变单元焦耳热相互影响的数学模型极其复杂,阻变单元的写入方式各有不同,在RRAM中精确计算热串扰对保持的影响是一项极其困难的任务,因此本文使用一种估计方法:正如前文所述,在RRAM的热串扰问题中,起主导因素的是Reset操作,在有限的保持时间内Reset操作对相邻阻变单元影响的次数越多代表了这些相邻单元的保持时间损失得越多,因此减少Reset操作数的比例相当于增加的保持时间的比例。在使用这种估计方法的前提下,图 8绘出了在使用TFC算法后保持时间增加的比例和参数k的关系,当k值大于4之后保持时间提升在35%以上,而k值大于4的条件几乎所有的RRAM存储器可以满足。

上述仿真都是基于单字节数据块的结果,即n=8,设计者可以根据实际需要调整这个值。显然n越小保持时间增加比例和热通量减少比例越多。当n=4、k=8时,保持时间增加比例和热通量减少比例可以达到50%以上,但是要付出的代价是每4个比特数据就需要一个flag来表明这些比特位是否进行了翻转编码操作,相当于存储器需要使用20%的存储空间来存储标志位信息,而以字节为单位数据块的方式则只需要1/9的存储空间。由于RRAM的集成度很高,存储空间一般不是问题,但是设计者还是应该根据系统实现的实际情况来配置n的值。

最后,TFC算法本身会在一定程度上增加写过程的时延,如表 1所示是在SMIC 55 nm工艺下对TFC算法的RTL代码进行综合后得到的时延和面积结果,可见TFC算法的时延在5 ns左右,这对于写时间在400~900 ns范围[22]的写过程来说其造成的时延影响是很小的。

表 1 基于SMIC 55 nm工艺的TFC算法时延和面积结果 Table 1 Latency and area results of TFC algorithm based on SMIC 55 nm technology

| 位宽/bit | 时延/ns | 面积/μm2 |

| 8 | 4.80 | 56.3 |

| 16 | 4.99 | 112.6 |

| 32 | 4.87 | 225.3 |

| 64 | 5.32 | 450.6 |

表选项

4 结 论 本文在讨论了焦耳热对RRAM存储器影响的基础上,提出了一种TFC算法,分析和仿真的结果表明:

1) TFC算法具有较强的可实现性,既可以在软件层也可以在硬件层实现。

2) TFC算法具有较好的可移植性,其对不同种类的RRAM、不同的RRAM写方式,即不同k值的RRAM存储器都有较好的适用性。

3) 系统设计者可以根据实际需求在可靠性和存储空间之间进行权衡,以便更优化地配置TFC算法中参数n的值。

4) 当n取为8时,TFC算法平均可降低30%~40%的写入焦耳热,阻变单元的保持时间估值平均可增加35%以上。

5) TFC算法同时也降低了RRAM 30%以上的写操作功耗。

参考文献

| [1] | CHEN Y Y,KOMURA M,DEGRAEVE R,et al.Improvement of data retention in HfO2/Hf 1T1R RRAM cell under low operating current[C]//2013 IEEE International Electron Devices Meeting (IEDM 2013).Piscataway,NJ:IEEE Press,2013:10.1.1-10.1.4. |

| Click to display the text | |

| [2] | CHEN Y S,LEE H Y,CHEN P S,et al.Highly scalable hafnium oxide memory with improvements of resistive distribution and read disturb immunity[C]//2009 IEEE International Electron Devices Meeting (IEDM 2010).Piscataway,NJ:IEEE Press,2010:5.5.1-5.5.4. |

| Click to display the text | |

| [3] | CAGLI C,IELMINI D,NARDI F,et al.Evidence for threshold switching in the set process of NiO-based RRAM and physical modeling for set,reset,retention and disturb prediction[C]//2008 IEEE International Electron Devices Meeting(IEDM 2008).Piscataway,NJ:IEEE Press,2008:1-4. |

| Click to display the text | |

| [4] | XUE X, JIAN W, YANG J, et al. A 0.13 μm 8 Mb logic-based CuxSiyO ReRAM with self-adaptive operation for yield enhancement and power reduction[J]. IEEE Journal of Solid-State Circuits,2013, 48(5): 1315–1322. |

| Click to display the text | |

| [5] | LARCHER L, PUGLISI F M, PAVAN P, et al. A compact model of program window in HfOx RRAM devices for conductive filament characteristics analysis[J]. IEEE Transactions on Electron Devices,2014, 61(8): 2668–2673. |

| Click to display the text | |

| [6] | YU S.Overview of resistive switching memory (RRAM) switching mechanism and device modeling[C]//2014 IEEE International Symposium on Circuits & Systems(ISCAS 2014).Piscataway,NJ:IEEE Press,2014:2017-2020. |

| Click to display the text | |

| [7] | JIANG Z,YU S,WU Y,et al.Verilog-A compact model for oxide-based resistive random access memory (RRAM)[C]//International Conference on Simulation of Semiconductor Processes & Devices(SISPAD).Piscataway,NJ:IEEE Press,2014:41-44. |

| Click to display the text | |

| [8] | NARDI F, BALATTI S, LARENTIS S, et al. Complementary switching in oxide-based bipolar resistive-switching random memory[J]. IEEE Transactions on Electron Devices,2013, 60(1): 70–77. |

| Click to display the text | |

| [9] | IELMINI D, NARDI F, BALATTI S. Evidence for voltage-driven set/reset processes in bipolar switching RRAM[J]. IEEE Transactions on Electron Devices,2012, 59(8): 2049–2056. |

| Click to display the text | |

| [10] | NARDI F, LARENTIS S, BALATTI S, et al. Resistive switching by voltage-driven ion migration in bipolar RRAM-Part I:Experimental study[J]. IEEE Transactions on Electron Devices,2012, 59(9): 2461–2467. |

| Click to display the text | |

| [11] | LARENTIS S, NARDI F, BALATTI S, et al. Resistive switching by voltage-driven ion migration in bipolar RRAM-Part II:Modeling[J]. IEEE Transactions on Electron Devices,2012, 59(9): 2468–2475. |

| Click to display the text | |

| [12] | CHEN Z,HUANG P,LI H T,et al.Optimization of uniformity in resistive switching memory by reducing thermal effect[C]//201412th IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT).Piscataway,NJ:IEEE Press,2014:1-3. |

| Click to display the text | |

| [13] | LIU H T, LV H B, YANG B H, et al. Uniformity improvement in 1T1R RRAM with gate voltage ramp programming[J]. IEEE Electron Device Letters,2014, 35(12): 1224–1226. |

| Click to display the text | |

| [14] | YALON E, RIESS I, RITTER D. Heat dissipation in resistive switching devices:Comparison of thermal simulations and experimental results[J]. IEEE Transactions on Electron Devices,2014, 61(4): 1137–1144. |

| Click to display the text | |

| [15] | NINOMIYA T, MURAOKA S, WEI Z, et al. Improvement of data retention during long-term use by suppressing conductive filament expansion in TaOx bipolar-ReRAM[J]. IEEE Electron Device Letters,2013, 34(6): 762–764. |

| Click to display the text | |

| [16] | RUSSO U, IELMINI D, CAGLI C, et al. Self-accelerated thermal dissolution model for reset programming in unipolar resistive-switching memory (RRAM) devices[J]. IEEE Transactions on Electron Devices,2009, 56(2): 193–200. |

| Click to display the text | |

| [17] | LI H T,CHEN H Y,CHEN Z,et al.Write disturb analyses on half-selected cells of cross-point RRAM arrays[C]//2014 IEEE International Reliability Physics Symposium(IRPS 2014).Piscataway,NJ:IEEE Press,2014:MY.3.1-MY.3.4. |

| Click to display the text | |

| [18] | ZULOAGA S,LIU R,CHEN P Y,et al.Scaling 2-layer RRAM cross-point array towards 10 nm node:A device-circuit co-design[C]//2015 IEEE International Symposium on Circuits and Systems (ISCAS 2015).Piscataway,NJ:IEEE Press,2015:193-196. |

| Click to display the text | |

| [19] | LI Y,CHEN W,LU W,et al.Impact of coupling capacitance on read operation of RRAM devices in 1D1R crossbar architectures[C]//2014 IEEE 57th International Midwest Symposium on Circuits and Systems (MWSCAS 2014).Piscataway,NJ:IEEE Press,2014:989-992. |

| Click to display the text | |

| [20] | GAO B,KANG J F,ZHANG H W,et al.Oxide-based RRAM:Physical based retention projection[C]//2010 Proceedings of the European Solid-State Device Research Conference (ESSDERC 2010).Piscataway,NJ:IEEE Press,2010:392-395. |

| Click to display the text | |

| [21] | ZHANG L,HUANG R,HSU Y Y,et al.Statistical analysis of retention behavior and lifetime prediction of HfOBx-based RRAM[C]//2011 IEEE International Reliability Physics Symposium (IRPS 2011).Piscataway,NJ:IEEE Press,2011:MY.8.1-MY.8.5. |

| Click to display the text | |

| [22] | KIM S Y, BAEK J M, SEO D J, et al. Power-efficient fast write and hidden refresh of ReRAM using an ADC-based sense amplifier[J]. IEEE Transactions on Circuits and Systems II:Express Briefs,2013, 60(11): 776–780. |

| Click to display the text | |