,1,2,*1.

,1,2,*1. 2.

High-Throughput Many-Core Processor Design

Ye Xiaochun1, Li Wenming1, Zhang Yang1, Zhang Hao1, Wang Da1, Fan Dongrui ,1,2,*1.

,1,2,*1. 2.

通讯作者: * 范东睿(E-mail:fandr@ict.ac.cn)

收稿日期:2019-11-30网络出版日期:2020-02-20

| 基金资助: |

Received:2019-11-30Online:2020-02-20

作者简介 About authors

叶笑春,中国科学院计算机技术研究所,博士,副研究员,计算机学会会员,主要研究领域为高通量处理器体系结构及软件模拟技术。

本文主要承担的工作为众核处理器架构设计和文章修改。

Ye Xiaochun, Ph.D., is an associate professor. Member of China Computer Federation. His research interests include high throughput processor architecture and software simulation.

The main contributions to this paper is the design of many-core architecture and paper revision.

E-mail: yexiaochun@ict.ac.cn

李文明,中国科学院计算机技术研究所,博士,副研究员,计算机学会会员,主要研究领域为高通量处理器设计及软件模拟技术。

本文主要承担的工作为高密度路网设计、片上存储设计及文章编写。

Li Wenming, Ph.D., is an associate professor. Member of China Computer Federation. His research interests include high throughput computing architecture and software simulation.

The main contributions to this paper is the design of high-density NoC, on-chip memory and paper writing.

E-mail: liwenming@ict.ac.cn

张洋,中国科学院计算机技术研究所,博士,工程师,计算机学会会员,主要研究领域为高通量处理器设计及实时系统。

本文主要承担的工作为任务实时性调度机制设计及实验分析。

Zhang Yang, Ph.D., is an engineer. Member of China Computer Federation. His research interests include high throughput computer architecture, real-time system.

The main contributions to this paper is the design of real-time scheduler and experiments analysis.

E-mail: zhangyang@ict.ac.cn

张浩,中国科学院计算机技术研究所,博士,高级工程师,计算机学会会员,主要研究领域为高通量计算机体系结构。

本文主要承担的工作为结构设计的可行性分析及实验设计。

Zhang Hao, Ph.D., is an associate professor. Member of China Computer Federation. His research interests include high throughput computer architecture.

The main contributions to this paper is conducting the feasibility analysis and experiments design.

E-mail: zhanghao@ict.ac.cn

王达,中国科学院计算机技术研究所,博士,副研究员,计算机学会会员,主要研究领域为处理器微体系结构。

本文主要承担的工作为处理器核内多线程微结构设计及线程实时性任务调度结构设计。

Wang Da, Ph.D., is an associate professor. Member of China Computer Federation. Her research interest focuses on processor microarchitecture design.

The main contributions to this paper is the design of multi-threaded microstructure and real-time task scheduling architecture.

E-mail: wangda@ict.ac.cn

范东睿,中国科学院计算机技术研究所,博士,研究员,博士生导师,计算机学会高级会员,主要研究方向为高通量/高性能处理器体系结构。

本文主要承担的工作为研究项目负责人及整体架构设计。

Fan Dongrui, Ph.D., is a professor. Senior Member of China Computer Federation. His research interests include high throughput and High performance many-core processor microarchitecture.

The main contributions to this paper is the leader of the project and design of the overall architecture. E-mail:fandr@ict.ac.cn

摘要

【目的】随着云计算、物联网以及人工智能等新型高通量应用的迅速兴起,高性能计算的主要应用从传统的科学与工程计算为主逐步演变为以新兴数据处理为核心,这给传统处理器带来了巨大的挑战,而高通量众核处理器作为面向此类应用的新型处理器结构成为重要的研究方向。【方法】针对上述问题,本文分析了高通量典型应用特征,从数据处理端、传输端以及存储端三个核心环节开展了高通量众核处理器关键技术设计探讨,包括实时任务动态调度、高密度片上网络设计、片上存储层次优化等。【结果】实验结果显示上述机制可以有效确保任务的服务质量,提升网络的数据吞吐率,以及简化片上存储层次。【结论】随着万物互联时代对高并发强实时处理的迫切需求,高通量众核处理器有望成为未来数据中心的核心处理引擎。

关键词:

Abstract

[Objective] With the rapid growth of new high-throughput applications such as cloud computing, the Internet of Things, and artificial intelligence, the main applications of high-performance computing have gradually evolved from traditional scientific and engineering computing to emerging data processing, which brought huge challenges to traditional processors. High-throughput many-core processors are becoming a new type of processor architecture dealing with such applications and therefore an important research direction. [Method] In view of the above problems, this paper analyzes the typical characteristics of high-throughput applications, and discusses the key design of high-throughput many-core processors from the three core aspects of data processing, transmission, and storage. The design includes real-time task dynamic scheduling, high-density on-chip network design and on-chip storage hierarchy optimization, etc. [Results] The experimental results show that the above mechanism can effectively ensure the service quality of tasks, improve the data throughput rates, and simplify the on-chip memory hierarchy. [Conclusion] With the urgent demand for high concurrency and strong real-time processing in the era of Internet of Everything, high-throughput many-core processors are expected to become the main processing engine in future data centers.

Keywords:

PDF (11092KB)元数据多维度评价相关文章导出EndNote|Ris|Bibtex收藏本文

本文引用格式

叶笑春, 李文明, 张洋, 张浩, 王达, 范东睿. 高通量众核处理器设计. 数据与计算发展前沿[J], 2020, 2(1): 70-84 doi:10.11871/jfdc.issn.2096-742X.2020.01.006

Ye Xiaochun.

引言

随着云计算、物联网以及人工智能等技术的迅猛发展,大型数据中心的并发请求数量迅速发展到亿级以上。经统计,百度日处理的搜索量已经超过100亿次,平均每秒11万次以上;淘宝的后台数据库在2019年双十一的峰值访问速度约为7万次每秒,全天合计为56亿次读请求;Facebook每天有14.9亿活跃用户,每天上传超过1亿张图片。根据国际数据公司(IDC)2019年发布的白皮书《2025 年中国将拥有全球最大的数据圈》,全球数据圈将从2018年的33ZB增至2025年的175ZB,我们的世界将会在2025年被数据所“淹没”[1]。为了应对如此大规模的海量数据,据预测,到2020年将新增互联网数据中心机柜18.54万台,较2016年的5.82万台的保有量增加接近319% [2]。更甚的是,诸如微博、团购、“秒杀”等网络应用的出现,给大规模数据的实时处理及QoS(服务质量)提出了更高的要求。因此,互联网技术的普及应用带来的种种新特性给当前的高性能处理器芯片和计算机系统带来了巨大的挑战。这种由网络发展带来的新型应用,已经成为数据中心的主要负载,其特征也从传统的浮点计算为主变成处理大量高并发的用户服务请求以及海量数据分析,强调任务的高并发、用户服务请求的强实时以及数据的高吞吐处理能力。这类应用的目标已不再是传统的评价超级计算机性能的LINPACK速度[3],而是高通量,即提高单位时间内处理的并发任务的数量。这种由互联网发展带来的新型应用负载,我们称之为“高通量应用”。高通量应用和传统的高性能应用存在本质上的区别,表1 对高通量应用负载特性和高性能负载特性进行了对比。从表中可以看出,面向网络服务的新型高通量应用在很多方面和面向科学计算的高性能应用存在着不同之处。传统高性能计算主要针对科学计算应用,程序往往具有较好的局部性,属于计算密集型应用,其所追求的目标是追求高速度。而高通量应用面向的是新型网络服务,任务并发度大且对实时性有较高要求,其数据量大且程序局部性较差,属于请求密集型应用。这类应用追求的目标是高通量,即提高单位时间内处理的并发任务数目[4,5,6,7]。由于高性能计算由来已久,目前的主流通用计算机和高端计算系统的发展都深受其影响,这也使得当前主流处理器体系结构在针对网络服务这种高并发、高实时、低延迟的高通量应用时表现出诸多不足,已有的诸多研究成果也表明高通量应用与传统处理器架构的不适应性[8,9,10,11,12,13,14,15,16,17]。

Table 1

表1

表1高通量计算与传统高性能计算的对比

Table 1

| 典型应用 | 程序特征 | 设计目标 | |

|---|---|---|---|

| 传统高性能计算 | 科学与工程计算应用 | 任务单一,负载变化小,计算量大,计算局部性好 | 高速度(算得快) |

| 新型高通量计算 | 互联网数据中心应用 | 任务多样,流式计算特征,数据量大,实时性要求高 | 高通量(算得多) |

新窗口打开|下载CSV

针对数据中心面临的挑战,设计实现高能效大规模众核处理器结构是应对高通量应用的有效手段,也已经成为国内外学术界和产业界的研究热点。比较有代表性的研究成果包括,P. Lotfi-Kamran等人提出了Scale-out Processor设计理念,以性能密度(performance-density)为衡量标准提出了共享LLC众核Pod单元,并利用多个Pods搭建整个Scale-Out Processor,通过寻求单位芯片面积上的最优计算性能,尽可能提高单芯片上的数据吞吐能力[10]。同时还提出了提高片上LLC访存效率的NOC-Out众核拓扑结构,通过将LLC中心化并设置专用访问数据通路,提高数据访问效率[11]。Hardavellas等人从数据中心处理器能效比的角度出发,通过采用异构专用众核以及动态控制异构逻辑单元电压,来提高处理器芯片的高性能和高能效比,使其更加适用于数据中心应用场景[12]。Jongse等人提出了面向机器学习的Scale-Out处理器,将处理的通用性、数据通量及能效等进行了综合考量设计[13]。Akshitha等人通过分析数据中心典型微服务算法特征,为面向数据中心高通量众核处理器提供了设计思路[14]。Artemiy等人分析和权衡了在多种并存的数据中心应用下处理器在面向QoS和处理通量之间的关系和设计思路[15]。国内也有许多面向数据中心的众核处理器结果设计,例如,申威处理器(SW26010)以及飞腾处理器(FT2000)等,都在数据中心得到广泛的应用,取得了优异的成绩。当然,还存在其他众多针对数据中心应用的体系结构研究成果,均取得了较好的性能及能效比提升。虽然在面向数据中心应用的众核体系结构设计中已经出现诸多的研究成果,取得了较好的效果。但是,随着高通量应用的数据量、并发请求数量以及对实时性的需求的急速增加,需要更为有效的高通量众核处理器结构优化设计,提高处理器在数据处理端、数据传输端以及数据存储端的吞吐能力、并发处理能力以及实时响应能力。

目前传统计算机系统的设计并不能很好地满足高通量应用的新特性,主要体现在以下几个方面:

(1)数据格式与处理器数据结构不匹配

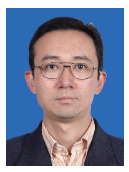

在高通量应用中相当一部分的访存粒度小于8 Bytes。如图1所示,对于K-Means来说,近90%的访存粒度为4Bytes,而对于Grep来说,1Byte的访存粒度近90%。相比而言,在传统高性能计算测试程序集SPLASH-2 [18]应用中,8 Bytes访存粒度占绝大部分。可见对于高通量应用来说,访存粒度明显小于传统应用。这种细粒度的数据请求与传统高宽度的数据通路不匹配,造成硬件资源的利用率下降。

图1

新窗口打开|下载原图ZIP|生成PPT

新窗口打开|下载原图ZIP|生成PPT图1高通量应用(左)及传统SPLASH-2应用(右)访存粒度分布示意图

Fig.1Distribution of memory access granularity in HTC applications (left) and conventional applications (right)

(2)数据流动与处理器数据通路不匹配

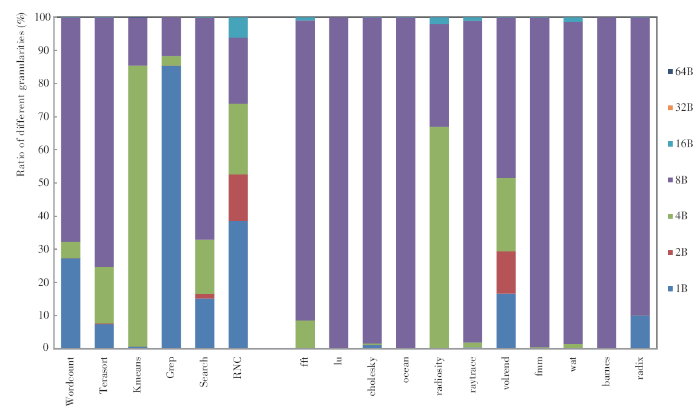

典型的高通量应用其数据重用性低,数据处理通常以一系列处理阶段分步骤完成,而通用处理器以L1、L2、L3分级缓存集中处理的方式明显与数据流动加工的天然过程不匹配。实验选用WordCount, TeraSort, Search三个典型的基于MapReduce的高通量应用作为基准测试程序。实验硬件平台选用Intel Xeon E5645多核处理器对上述高通量应用的访存行为进行相关测试。

由实验结果图2可知,对于一级Cache来说,具有非常好的命中率。对于二级Cache来说,由于数据的局部性(数据空间局部性为流式局部性,数据按地址顺序使用一次即被抛弃)被一级Cache所消耗,因此导致二级Cache的命中率很低,而LLC的相联度大并且容量也大,反而比L2有更多命中,但是绝对命中率也并不理想。实验结果体现出传统多级Cache在高通量应用场景下的不适应性。

图2

新窗口打开|下载原图ZIP|生成PPT

新窗口打开|下载原图ZIP|生成PPT图2传统多核处理器Cache结构在典型高通量测试程序下的性能统计。(a)展示了各级cache在不同用例下的失效率随线程数增加变化情况;(b)展示了各级cache在不同用例下的平均访问延迟随并发线程数的变化情况。

Fig. 2Cache performance in traditional multi-core processor under WordCount, TeraSort and Search Quest applications. (a)shows the miss ratio of cache hierarches with different number of concurrent threads under different applications; (b)shows average access latency of cache heartaches with different number of concurrent threads under different applications.

(3)数据实时处理需求与处理器结构预测性不匹配

大量互联网应用场景对云端数据处理有实时性需求,网络游戏与网络安全中也有实时编码解码需求,而目前处理器大量采用的复杂调度方法,如乱序执行、复杂流水线设计等,都使得整体结构的最坏执行时间(WCET)不可预测。在面对不断发展的新型应用的需求下,当前主流计算机系统的数据处理能力和并发服务能力已难以满足大规模数据中心需求。为了确保服务质量,当前数据中心很多关键部件的利用率都处在较低的水平,例如,对微软的Bing搜索、Hotmail和并行数据分析引擎Cosmos服务器的运行情况分析,发现在处理器有67~97%使用率的压力测试中,内存带宽的使用率只有2~6%[17]。谷歌数据中心也有类似情况,据统计,2013年,谷歌在线应用数据中心的平均CPU利用率只有30%左右[20],而更多的其它企业甚至还更低[21]。

综上所述,传统的高性能计算机已难以高效处理互联网时代新产生的高通量应用,亟需设计一套针对高通量应用的新型体系结构来面对互联网时代的挑战。

1 高通量计算

1.1 什么是高通量计算

高通量计算是适用于互联网新兴应用负载特征,在强时间约束下处理高吞吐量请求的一种新型高性能计算。传统的高性能计算主要是“算得快”,旨在更快地解决更大的问题,典型负载是诸如LINPACK、FFT之类的科学计算应用。而高通量计算则是“算得多”,即并发处理的数据多、请求多,典型负载如无线通信控制系统、互联网服务等。对于此问题,我们可以用赛车项目中的“正计时”和“倒计时”两个概念来形象地说明高性能和高通量之间的区别。高性能计算是指在“正计时”的时间内“更快”地完成某个任务负载。而高通量计算是指在“倒计时”的时间内尽可能高并发地完成“更多”的任务负载,强调单位时间内能够处理更多的任务。1.2 高通量处理器设计思路

高通量计算定位于提高数据的并发处理能力,因此在高通量处理器设计中,数据通路的高效控制是一个核心问题,高通量处理器的设计目标是在通量场景下全局全时地保证数据通路的有序控制。基于此,高通量处理器在数据通路的三个核心环节,即数据存储、数据传输和数据处理方面都提出了新的设计需求:(1)数据处理:需要设计高并发执行、实时性可控的处理机制;

(2)数据传输:需要设计支持离散细粒度访存的高吞吐片上网络;

(3)数据存储:需要设计可有效应对高通量流式数据访问特征的存储系统。

在高通量处理器的数据通路设计方面,我们借鉴了城市交通管理的思路。高通量计算在结构特征、资源管理、调度策略等方面都非常类似于城市交通管理,两者的共同特征都是在单位时间内完成尽可能多的处理请求,并保证QoS。如表2所示,我们参考交通设计方法开展了高通量处理器结构的设计。

Table 2

表2

表2高通量计算结构与城市交通结构类比

Table 2

| 共性特征 | 结构对比 | |||

|---|---|---|---|---|

| 高通量计算结构 | 规模庞大 实时调度需求 访问不规则 流量压力大 | 存储层次优化 | 全局实时调度 | 低宽度高密度网络 |

| 城市交通结构 | 候车空间导流 /快速通道 | 交通指挥控制中心 | 高密度路网 | |

新窗口打开|下载CSV

(1)在数据处理端:我们实现了基于硬件支持的任务调度机制,将任务按照优先级及剩余裕度时间进行动态调度,有效保障了任务的QoS。

(2)在数据传输端:针对大量细粒度访存的需求,实现了高密度路网,提高片上网络的利用率和吞吐量。

(3)在数据存储端:优化了片上缓存层次的配置,提高片上缓存的有效利用率,进而降低对面积和功耗的开销。

2 高通量众核处理器整体架构设计

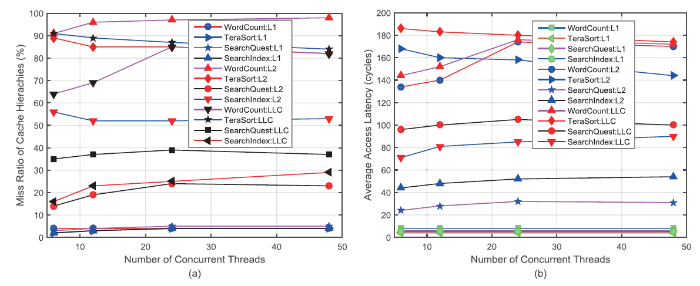

通过对高通量应用的特征分析,我们在文献[19]中提出了如图3结构的高通量众核处理器设计。图3

新窗口打开|下载原图ZIP|生成PPT

新窗口打开|下载原图ZIP|生成PPT图3高通量众核处理器架构示意图

Fig. 3High-throughput many-core processor architecture diagram

众核包含256个同构处理器核,采用16×16的两级环状拓扑结构,如图3所示,主环即为图中内部的环,子环通过路由器和主环连接。主环一共16个路由器与子环进行连接,并与Shared Cache、Memory、PCIe等设备连接。在256核的设计中,目前采用了4个DDR4作为高通量处理器的存储结构。子环通过路由器与主环连接,子环包括16个处理器核。每个处理核通过路由器与子环连接。基于上述结构,本文对数据处理端、传输端和存储端的关键设计进行分析探讨。

3 实时任务调度机制

3.1 实时性任务调度需求分析

在大规模并行多线程处理器体系结构中,保证线程的服务质量,即满足线程的实时性约束保障,是一个非常重要的问题。针对这一问题,我们首先分析了实时调度机制对性能的影响。我们构造了如表3所示配置项的测试环境进行测试。测试分三阶段进行:Table 3

表3

表3系统配置

Table 3

| 配置项 | 参数值 |

|---|---|

| 任务表项 | 4096项(对应一个子环) |

| 每个子环上的核数 | 16*2路SMT |

| 每个核上的调度任务表项 | 256项 |

| 每个核可调度的任务数N_TASK | 128个,所有任务等长 |

| 任务DEADLINE | 任务长度*F,通过调节F的大小(64-128)来调节任务的deadline紧迫程度 |

新窗口打开|下载CSV

第一阶段,热身阶段,均匀注入2*N_TASK个任务;这个阶段的时间是2*N_TASK*任务执行时间,也即能满足任务刚好在时间内执行完。

第二阶段,实际测试阶段,使用4种不同模式注入N_TASK个任务。这个阶段的时间是N_TASK*任务执行时间,也即如果均匀注入,可以在时间内刚好执行完毕。测试时分别在开始的1/4时间内,注入N_TASK的1/4、2/4、3/4、4/4。后面三种模式都会导致系统在这个区间出现集中注入的情况,从而容易引起任务失效。

第三阶段,退出阶段,均匀注入2*N_TASK个任务,时间和第一阶段相同。

测试时,将所有任务组织成优先级队列,按照不同的优先级进行轮询,如果发现任务未执行完,且优先级是最高优先级,即调度该任务执行固定cycle,如此循环,直到所有任务执行完毕为止。其中:

Deadline_1: 任务的deadline是任务执行时间的64倍,deadline最严格;

Deadline_2: 任务的deadline是任务执行时间的96倍,deadline次严格;

Deadline_3: 任务的deadline是任务执行时间的128倍,deadline要求最松。

Case1:前1/4时间注入1/4的任务量;

Case2:前1/4时间注入2/4的任务量;

Case3:前1/4时间注入3/4的任务量;

Case4:前1/4时间注入4/4的任务量;

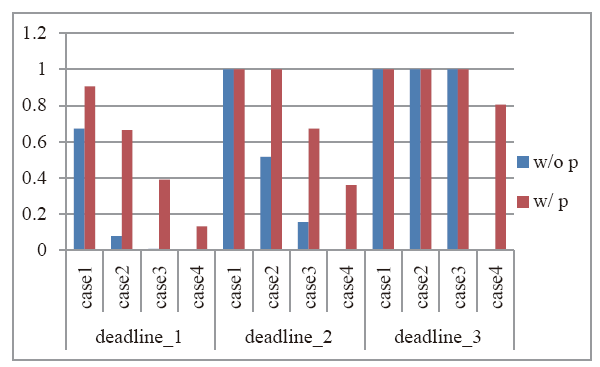

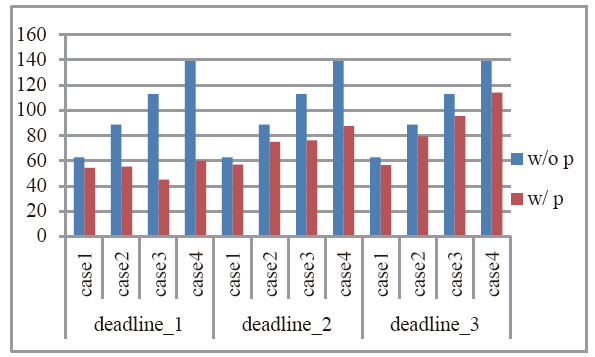

实验结果如图4所示,图中纵坐标数值是成功完成的任务占总任务的比例,红色为优先级调度的结果,蓝色为没有优先级调度的结果。Deadline越严格,成功完成的任务越少,但是,加入优先级调度后成功完成的任务数明显多于无优先级调度的情况。

图4

新窗口打开|下载原图ZIP|生成PPT

新窗口打开|下载原图ZIP|生成PPT图4实时任务完成率的对比

Fig.4Comparison of real-time task completion rates

图5所示的纵坐标数值是实际调度执行的平均完成时间相比于任务所需的理论执行时间的比值。可以看到,对于无优先级的调度,不同deadline下,任务的完成时间几乎相同,因为都是简单的轮询调度。当加入优先级调度后,任务完成时间明显变短,有利于满足deadline的要求,而且还可以看到,deadline越严格,任务的平均完成时间会越短。因为此时优先级调度会使得优先任务得到更多的连续调度机会。

图5

新窗口打开|下载原图ZIP|生成PPT

新窗口打开|下载原图ZIP|生成PPT图5实时任务完成时间的对比

Fig.5Comparison of real-time task completion time

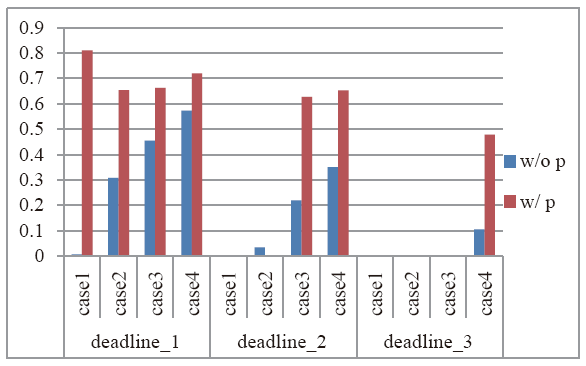

图6中纵坐标数值表示的是任务失效时的剩余执行时间占所需执行时间的比值,图中某些空的项是由于该场景下没有失效任务。对于失效任务,在失效时其剩余的执行时间越长越好,这说明浪费在这个失效任务上的计算资源更少。可以看到,加入优先级调度后,失效的任务的剩余执行时间都比较长,大部分情况下,已执行的比例都不足50%。而没有优先级调度时,任务失效时,失效任务已经都基本要执行结束了,可见无优先级的调度对计算资源的浪费比较严重。

图6

新窗口打开|下载原图ZIP|生成PPT

新窗口打开|下载原图ZIP|生成PPT图6失效任务在失效时的平均剩余执行时间对比

Fig.6Comparison of remaining time of failed tasks

3.2 调度机制设计及性能评估

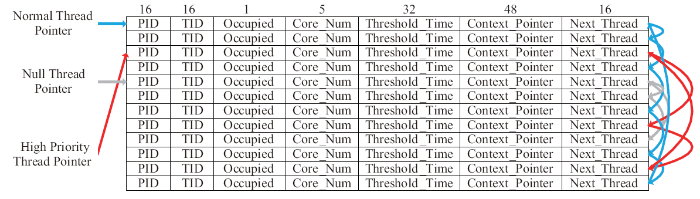

基于以上分析,在高通量处理器设计中,我们通过基于硬件任务调度机制对任务的实时性需求提供保障。图7所示为硬件实现的任务分发器,用于对处理器内并发执行的线程进行裕度时间管理,通过多个任务链表的方式,实现了不同的任务优先级管理。其中,PID代表任务所属进程号,TID为相应线程号,Occupied域标识任务是否正在运行,Core_Num用来记录任务运行的核号,Threshold_Time记录需要转入高优先级模式的时间点,Context_Pointer为指向该Thread的Context对应的内存地址,Next_Thread为指向本链表中下一个Thread的Index。分发器中在同一时刻存在三个链表:(1)空任务链表(Null Thread List):这个链表中存储的是还没有被分配任务的硬件线程,一开始所有的任务分发器上的线程都属于该列表;(2)普通任务链表(Normal Thread List):这个链表中存储的是正在运行的硬件线程,这些线程的门槛时间还没有过,所以处于普通优先级;(3)高优先级链表(High Priority List):这个链表中存储的是正在运行的硬件线程,这些线程的门槛时间已过,所以处于高优先级。图7

新窗口打开|下载原图ZIP|生成PPT

新窗口打开|下载原图ZIP|生成PPT图7任务分发器

Fig.7Tasks dispatcher

为了节省功耗和面积,整个任务分发器由RAM构成,用链表方式进行遍历。随着核数和线程数的增多,任务分发器将变得越来越大,此时可以采用分级管理机制,高优先级任务被率先分配至表中待执行,多个分发器并行执行。

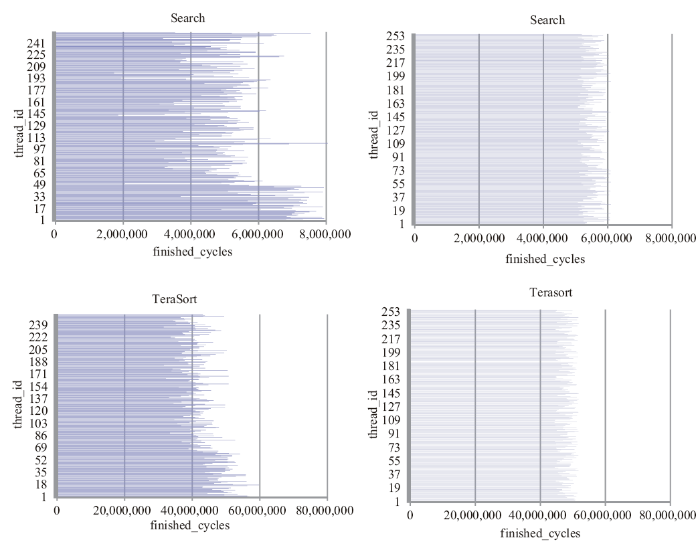

我们进一步测试了在前文所提及的高通量众核处理器结构下的实时任务调度机制的性能。如图8所示,在左图中,我们使用了Deadline Scheduler [22],它根据每个任务的剩余时间动态地调度任务,以提高所有任务的成功率。结果如图所示,在采用了实时调度机制控制下,尽管最早的退出线程的执行时间大于左图的执行时间,但线程执行的成功率得到明显提升,线程的完成时间也变得明显更加规整。

图8

新窗口打开|下载原图ZIP|生成PPT

新窗口打开|下载原图ZIP|生成PPT图8采用基于硬件的实时任务调度机制前后的任务完成情况对比

Fig.8Comparison of task completion before and after using hardware-based real-time task scheduling mechanism

4 高密度片上网络结构

4.1 高密度片上网络结构设计

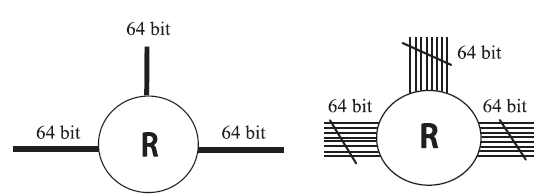

随着高通量处理场景对并发核数需求的不断增加,加之高通量应用中存在着大量的细粒度访存,造成了片上网络的效率依然不高。为了更深入地理解网络通路设计上存在的问题,我们以城市交通网络为例进行类比分析。在北京、东京、巴黎、纽约这些全球主要大都市中,北京汽车不比东京纽约多,而且面积也不比东京纽约小,但北京的交通状况和生活环境却感觉如此拥堵和拥挤。分析可知,东京、巴黎、纽约的路网密度比较大,既有比较宽的主干道路,也有众多高密度的网络道路。主干道单位时间内可以通过大量的车流,当主干道发生阻塞时,邻近众多的高密度辅路和支路网络也可以分担大量的车流来缓解交通阻塞。基于以上的分析,借鉴高密度道路设计的思路,我们提出了高密度片上网络的设计。为了最大限度控制硬件开销,我们在原有片上网络的基础上将较宽的通路拆分成多个细粒度的通道,每个通道独立控制,如图9所示。当不同粒度的访存请求从一个路由器发送到下一个路由器的时候,可以根据请求的大小选择合适的通道宽度,而其它未被使用的通道带宽可以并行传输其它请求。如此,可以提高带宽的有效利用率。

图9

新窗口打开|下载原图ZIP|生成PPT

新窗口打开|下载原图ZIP|生成PPT图9传统片上网络链路(左)与高密度片上网络链路(右)结构对比

Fig.9Structure comparison between traditional on-chip network links (left) and high-density NoC links (right)

图9展示了高密度路网中链路与传统链路之间的结构对比图。以下图为例,假设每个路由器有三个方向(左、右、本地),宽度为64bit宽。我们将传统的高宽度链路分割成低宽度的自治子链路,如图所示,64 bit宽的通路分割成8个8 bit宽的自治子链路,每个子链路可独立控制传输细粒度的数据包,也可以共同工作传输大数据包。

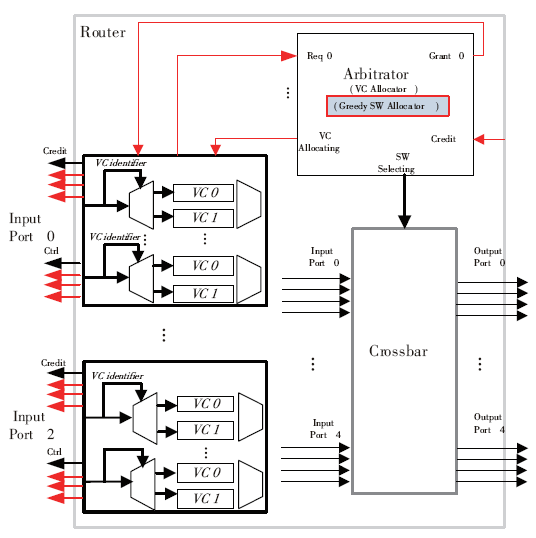

图10所示为高密度路网中路由器内部连线逻辑结构示意图。每个路由器有3个输入端口和3个输出端口。图中每个输入端口被分割成3个自主控制的子链路通道,且每个子通道支持两个虚通道。图中路由器结构分为三个主要的部分,左边为3个输入端口,与传统端口的不同是将链路的宽度分割成3个子链路,每个链路有自己的控制线(缓存区使能信号线等)、Credit信号线。相对于传统链路,添加的物理硬件即为控制信号线即控制逻辑等,链路的总宽度未发生变化,缓存大小也未发生变化。图中右上为仲裁器逻辑单元,与外界的连线包括与输入端口之间的虚通道分配控制信号、端口传输请求信号、端口传输使能、输出端口或下一路由传来的控制信号以及仲裁结果输出信号。所有的控制信号线由原先的一套变成高密度中的四套。

图10

新窗口打开|下载原图ZIP|生成PPT

新窗口打开|下载原图ZIP|生成PPT图10高密度片上网络路由器内部结构示意图

Fig.10Inner structure of router in high-density NoC

当传统网络结构变为高密度路网结构后,路由器内部传统的交叉开关分配算法并不能充分利用高密度路网带来的优势。为了适应高密度片上网络,我们结合链路连接结构提出了贪心传输机制来提高链路的有效利用率。“贪心”意味着传输链路在同一时刻尽可能传输更多的数据包。当几个待传输数据包大小不大于几个子链路通路的宽度时,这几个数据包便可以并行传输,以达到数据链路的充分利用。为了保证贪心传输机制的正常执行,在传统的(SA)Switch Allocation阶段,我们实现了GA(Greedy Algorithm)。在GA执行过程中,以输出端口为中心,在端口大小为上限的条件下,选择尽可能多的数据包。但是,为了保证公平性,算法需遵循一定的规则。

规则(1):以Round-Robin算法选择基准端口。所谓基准端口即以此端口的数据包大小为初始大小,通过贪婪算法选择其它端口的数据包,最终获取局部最优策略。使用RR算法轮询选择基准端口的原因是防止造成端口传输的不公平;

规则(2):基准端口数据包传输优先。对于某次传输,被选择的端口具有优先传输权利。所谓优先传输权利是指,当端口的虚通道或是虚通道内的缓冲中存在多个期望发往同一个输出端口时,优先组合基准端口的各个数据包,使其达到最优的传输效率。尽量选择同一端口的优点是降低输出端口所一次映射的输入端口,可以尽量使其它端口与其它输出端口映射,提高端口的利用率。若基准端口无法填满传输链路,则选择其它端口数据包进行合并传输;

规则(3):组合传输时不能存在重叠子通道。在合并传输的过程中,不能存在子通道重叠的数据包同时传输至同一个输出端口,例如端口1的子通道1和其它端口的子通道1不能同时传输至同一个输出端口。因为为了降低路由器内部交叉开关连线的复杂度,输出端口和输入端口的子通道是一一对应,非全相联映射关系。

4.2 高密度片上网络性能评估

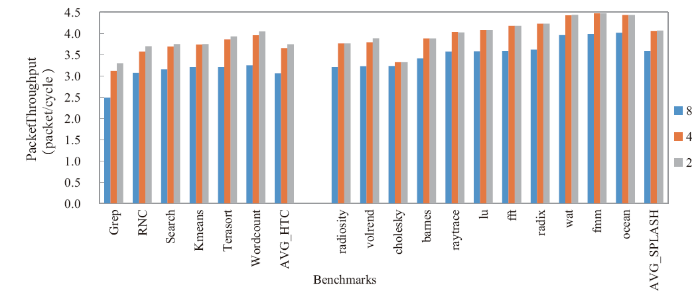

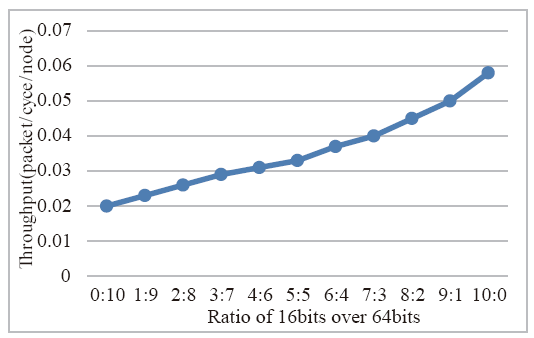

图11展示了高通量应用和SPLASH-2应用的数据吞吐量在饱和注入情况下随通路宽度的变化情况。实验中,我们分别测试了将64bits宽的链路切分成16bits、32bits以及原有宽度的配置下的饱和吞吐率情况。因为数据包的大小不一,理论上饱和吞吐量会随着链路的切分加深而上升。因为当切分的子链路越小时,可并行传输的数据包的概率会增多,从而增强片上网络的有效吞吐率。从实验结果可以看出,无论是高通量应用还是SPLASH-2应用,其吞吐率都随着通路宽度的降低而逐渐升高。对于高通量应用,子链路宽度从8 Bytes到4 Bytes时,平均吞吐率提高了19.3%,从8 Bytes到2 Bytes时,平均吞吐率提高了22.2%。其中,Grep应用分别提高了25.2%和32.4%。因为在Grep应用中,1 Byte的访存粒度占了近90%的比例,大量的细粒度访存消息使得高密度片上网络的优势得到了充分的发挥。对于SPLASH-2应用,子链路宽度从8 Bytes到4 Bytes时,平均吞吐率提高了13.3%,从8 Bytes到2 Bytes时,平均吞吐率提高了13.5%。因为在SPLASH-2中1 Bytes或2 Bytes细粒度访存比较少,所以从4 Bytes到2 Bytes的平均吞吐率的提高很小。由实验结果可知,高密度路网对于高通量应用和传统的SPLASH-2应用来说都有一定的性能提升,尤其对于高通量应用来说,效果显著。为了继续探索数据包大小在不同的比例下对片上网络的吞吐率(Throughput,网络所能够接受的最大注入率)的影响,我们试验了在不同数据包粒度下的数据吞吐率的变化趋势。实验选取了16bits和64bits两种数据包进行测试,片上路由链路宽度为64bits,两种数据包的出现比例为0:10, 1:9, 2:8, 3:7, 4:6, 5:5, 6:4, 7:3, 8:2, 9:1, 10:0,数据包出现的序列随机产生,实验结果如图12所示,可见低粒度的数据包占比较高时,网络的吞吐量有一定的性能提升。图11

新窗口打开|下载原图ZIP|生成PPT

新窗口打开|下载原图ZIP|生成PPT图11不同Channel宽度选择下的数据吞吐量对比

Fig.11Data throughput comparison under different channel width choices

图12

新窗口打开|下载原图ZIP|生成PPT

新窗口打开|下载原图ZIP|生成PPT图12不同的16bits和64bits数据包比例下吞吐率变化图

Fig.12Changes in throughput of different 16-bit and 64-bit data packet ratios

5 片上存储结构

5.1 片上Cache性能分析

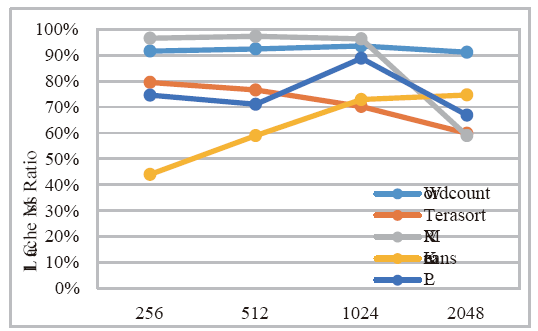

片上存储在处理器结构设计中扮演着重要角色,弥补了处理器核与主存储器的速度鸿沟。而对于数据密集型的高通量应用来说,片上存储对性能的影响更为巨大,因此需要合理设置片上存储来提高处理器的整体能效比。如前文中图2所示,传统Cache结构在高通量应用场景中出现了结构设计与应用需求明显不匹配的问题。一级Cache命中率极高,而二级Cache命中率很差。在高通量众核处理器片上存储设计中,为了保障通用性和可编程性,除SPM存储外,同时实现了片上Cache存储结构。为了探究在高通量应用中,对片上缓存的需求,我们首先对L1 Cache 和 L2 Cache进行试验分析和参数的确定,通过测试WordCount、TeraSort、KMP、K-Means、LP测试benchmark,对本文设计的面向高通量应用的的众核处理器 Cache Miss率进行了评估。实验配置私有L1 Cache 32K,4个共享256K L2 Cache。图13

新窗口打开|下载原图ZIP|生成PPT

新窗口打开|下载原图ZIP|生成PPT图13L1 Cache失效率

Fig.13L1 miss rate

图14

新窗口打开|下载原图ZIP|生成PPT

新窗口打开|下载原图ZIP|生成PPT图14L2 Cache失效率

Fig.14L2 miss rate

对于一级Cache来说,具有非常好的命中率,缺失率均稳定在1%以内。对于二级Cache来说,由于数据的局部性(数据空间局部性为流式局部性,数据按地址顺序使用一次即被抛弃)被一级Cache所消耗,因此导致二级Cache的命中率不高。

5.2 片上Cache设计探讨

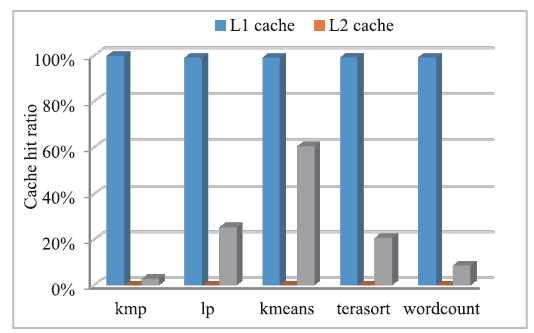

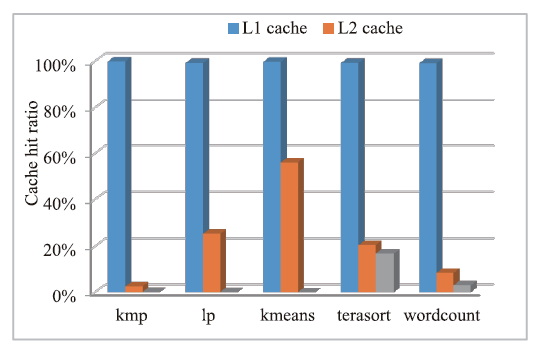

考虑通用性,本文在文献[19]所提众核结构上配置传统三级Cache结构并探讨其在高通量应用下的性能。图15和图16所示为高通量应用在传统3级Data Cache存储结构中各级Cache命中率。图15中的L2 Cache为核私有,而图16中的L2 Cache为共享Cache。Cache具体配置见表4。图15

新窗口打开|下载原图ZIP|生成PPT

新窗口打开|下载原图ZIP|生成PPT图15L1/L2私有,L3共享下的Cache性能统计

Fig.15Cache performance statistics for private L1 / L2 and shared L3

图16

新窗口打开|下载原图ZIP|生成PPT

新窗口打开|下载原图ZIP|生成PPT图16L1私有,L2/L3共享下的Cache性能统计

Fig.16Cache performance statistics for private L1 and shared L2 / L3

Table 4

表4

表4Cache层级配置参数

Table 4

| Cache层 | 私有/共享 | 容量大小 | 行大小 |

|---|---|---|---|

| L1 | 私有 | 32K | 64 Bytes |

| L2 | 私有/共享 | 256K | 64 Bytes |

| L3 | 共享 | 2048K | 64 Bytes |

新窗口打开|下载CSV

从结果中可以看出,几个典型高通量应用在访存行为上存在一个共同现象:L1 D-Cache的命中率非常高,L2和L3有一个的缺失率很高。其原因主要是由于Cache line大小保持了一致(64B),且大部分访存为流式数据,即数据地址连续且仅使用一次,导致其下一级Cache几乎全部是缺失。从面积和功耗的角度来说,L2和LLC的命中率并不高,但却占用了大量的片上面积,同时也带来了较高的功耗比。从实验结果来看,私有的L2 Cache没有必要,使用私有L1 Cache以及共享L2 Cache即可在性能和面积功耗上达到较好的权衡,无需L3 Cache。

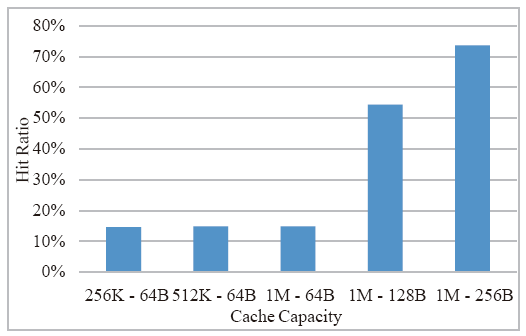

从以上实验数据中还可以看出,共享的二级Cache的命中率不高,对此我们进行进一步的探究,继续增加共享二级Cache的容量并对性能进行评估,以典型的KMP应用为例,测试结果如图17所示。

图17

新窗口打开|下载原图ZIP|生成PPT

新窗口打开|下载原图ZIP|生成PPT图17KMP应用下L2命中率随容量大小或Cache块大小变化趋势

Fig.17Trend of L2 hit rate in KMP applications with capacity or cache block size

由实验数据可知,在Cache块大小保持64 Bytes不变的情况下,即使二级Cache的容量不断增长,二级Cache的命中率依然比较低且变化可忽略不计。但当Cache块大小从64B增长到256B时,命中率从14.9%左右骤增到73.6%左右。主要原因是应用程序的顺序局部性较好,二级Cache所预取的值对一级Cache来说命中率非常高。因此,对于二级Cache的设计,推荐采用大Cache Block的配置(128B或256B)。

6 总结

随着具有高并发和强实时等特征的高通量应用成为网络服务数据中心的主要负载,传统高性能处理器设计已难以满足高通量应用的高效处理,必须针对高通量应用特征系统性地研究符合新应用特征的处理结构,高通量处理器的设计目标就是要打破传统高性能处理器一味追求速度快的设计方法,转而重点满足海量并发数据服务请求。本文通过对高通量应用特征的实验和分析,总结出高通量处理器需要面对的新型应用特征需求,基于两级环状网络的256核高通量众核处理器架构开展了关键技术的设计探讨。在数据处理端,针对高通量应用中高并发处理的实时性需求,采用基于硬件结构的两级任务调度和分配机制,提高大规模并行任务的调度有效性和实时性。在数据传输端,针对高通量应用离散的细粒度访存特征,采用高密度片上网络传输机制,提高片上网络对数据的传输能力。在数据存储端,针对高通量应用对片上存储的需求,优化了片上存储的配置参数,提高了高通量应用的数据存取能力。本文通过全面的实验和结果分析,探讨了面向高通量应用的众核处理器体系结构在数据处理端、传输端以及存储端的设计思路,期望对未来面向数据中心高通量应用的处理器体系结构设计具有一定的借鉴意义。利益冲突声明

所有作者声明不存在利益冲突关系。参考文献 原文顺序

文献年度倒序

文中引用次数倒序

被引期刊影响因子

[EB/OL]. .

URL [本文引用: 1]

[本文引用: 1]

[EB/OL]. .

URL [本文引用: 1]

[J].

[本文引用: 1]

[J]. October

[本文引用: 1]

[J].

[本文引用: 1]

[R].

[本文引用: 1]

[C].

[本文引用: 1]

[C].

[本文引用: 1]

[C].

[本文引用: 2]

[C].

[本文引用: 2]

[C].

[本文引用: 2]

[C].

[本文引用: 2]

[本文引用: 2]

[C].

[本文引用: 2]

[C].

[本文引用: 1]

[C].

[本文引用: 2]

[C].

[本文引用: 1]

[C].

[本文引用: 2]

[J].

[本文引用: 1]

[J].

[本文引用: 1]

[C].

[本文引用: 1]