全文HTML

--> --> -->目前国内外****对FinFET器件单粒子效应开展了相关实验研究并取得了一定的成果. 国外****对于FinFET单粒子效应的研究主要包括对电路单粒子翻转截面的研究[3-7]和对器件单粒子瞬态的研究[8-14]. Nsengiyumva等[3,4]研究了16 nm体硅FinFET触发器和28 nm平面器件触发器在不同LET、不同入射位置、不同供电电压等条件下的翻转截面, 得到FinFET器件单粒子翻转截面响应与平面器件的差异; 文献[5-7]报道了重离子入射角度和偏压对14/16 nm体硅FinFET D触发器翻转截面的影响及其机理; 文献[8]研究了FinFET参数变化对逻辑电路中单粒子瞬态的影响; 文献[9]研究了平面器件和FinFET器件单粒子闩锁敏感性差异. 文献[10-12]全面地研究了栅长为50和100 nm InGaAs沟道FinFET器件单粒子瞬态与器件Fin宽、衬底种类、偏置电压和入射激光波长的相关性, 并结合TCAD仿真研究得到InGaAs器件的电荷收集机制. 文献[13,14]通过激光和重离子实验研究比较了70 nm体硅和SOI FinFET器件的单粒子瞬态响应, 得到体硅器件相比SOI有更大的半高宽和幅值, 并给出体硅FinFET器件单粒子效应敏感位置. 国内****对于FinFET器件单粒子效应的研究较少, 以对器件单粒子瞬态仿真研究为主[15-19]. 文献[15-17]利用TCAD仿真研究得到FinFET器件fin结构参数、偏置电压与单粒子瞬态脉冲宽度的相关性和FinFET器件版图结构与器件间单粒子多瞬态效应(SEMT)的相关性. 文献[18]仿真研究入射粒子LET值、入射位置、器件偏置电压和器件参数对SOI FinFET器件单粒子瞬态的影响, 得到脉冲幅值和收集电荷量随这些变量的变化关系. 文献[19]仿真研究了体硅和SOI FinFET器件单粒子瞬态中电荷漂移和双极放大效应的贡献, 得出在体硅器件中单粒子瞬态脉冲由电荷漂移和双极放大效应共同引起, 而在SOI器件中以双极放大效应为主.

综合来看, 目前对于体硅FinFET器件单粒子效应电路层面的研究和InGaAs沟道FinFET器件单粒子瞬态的研究较多, 而对于应用更多的栅长30 nm以下的小尺寸Si沟道FinFET器件单粒子瞬态的研究几乎没有. 对于Si沟道FinFET器件栅长由100 nm缩小到30 nm或更小时, 是否会有新的因素影响单粒子瞬态产生的物理机制尚不明确.

本文结合激光单粒子实验和TCAD重离子仿真利用现有FinFET器件研究体硅FinFET器件栅长由100 nm缩小到30 nm, 器件重离子单粒子瞬态的波形变化以及造成该变化的物理机制, 研究结论将对更小尺寸FinFET器件单粒子瞬态提供理论参考. 结合激光实验和TCAD仿真是目前研究FinFET器件单粒子瞬态的重要方法. 首先利用激光微束从正面辐照器件获得30—100 nm栅长体硅FinFET器件单粒子瞬态波形和收集电荷情况, 分析得到栅长变短对器件单粒子瞬态脉冲的影响. 然后利用三维TCAD仿真研究器件在不同衬底厚度、栅长、入射位置和入射离子束宽度下的单粒子瞬态产生过程, 比较产生过程中器件内部电子浓度和电势分布变化, 得到栅长变短时FinFET器件重离子单粒子瞬态产生的物理机制.

2.1.器件结构

实验采用的器件为中国科学院微电子研究所提供的Si衬底N沟道FinFET器件, 其结构示意图如图1所示. 器件是在725 μm硅片上形成, 衬底之上为沟道截止区(channel stop)和氧化层隔离槽, 沟道截止区掺杂为2 × 1018铟掺杂, 沟道截止区上为源、漏和鳍(fin)区, 源、漏和鳍区实际形状为梯形, 高为35 nm, 上底宽为7 nm, 下底宽为13 nm. 源漏为2 × 1020的磷掺杂, 鳍区为2 × 1018的硼掺杂. 鳍上为0.6 nm氧化层, 氧化层上为2.4 nm HfO2和5 nm TiAl形成的叠栅. 实验采用双鳍和四鳍两种器件, 鳍间距都为3 μm, 采取4种不同栅长器件, 分别为30, 40, 60和100 nm. 图 1 双鳍FinFET器件结构模型

图 1 双鳍FinFET器件结构模型Figure1. The structure of two fin FinFET device.

2

2.2.实验条件

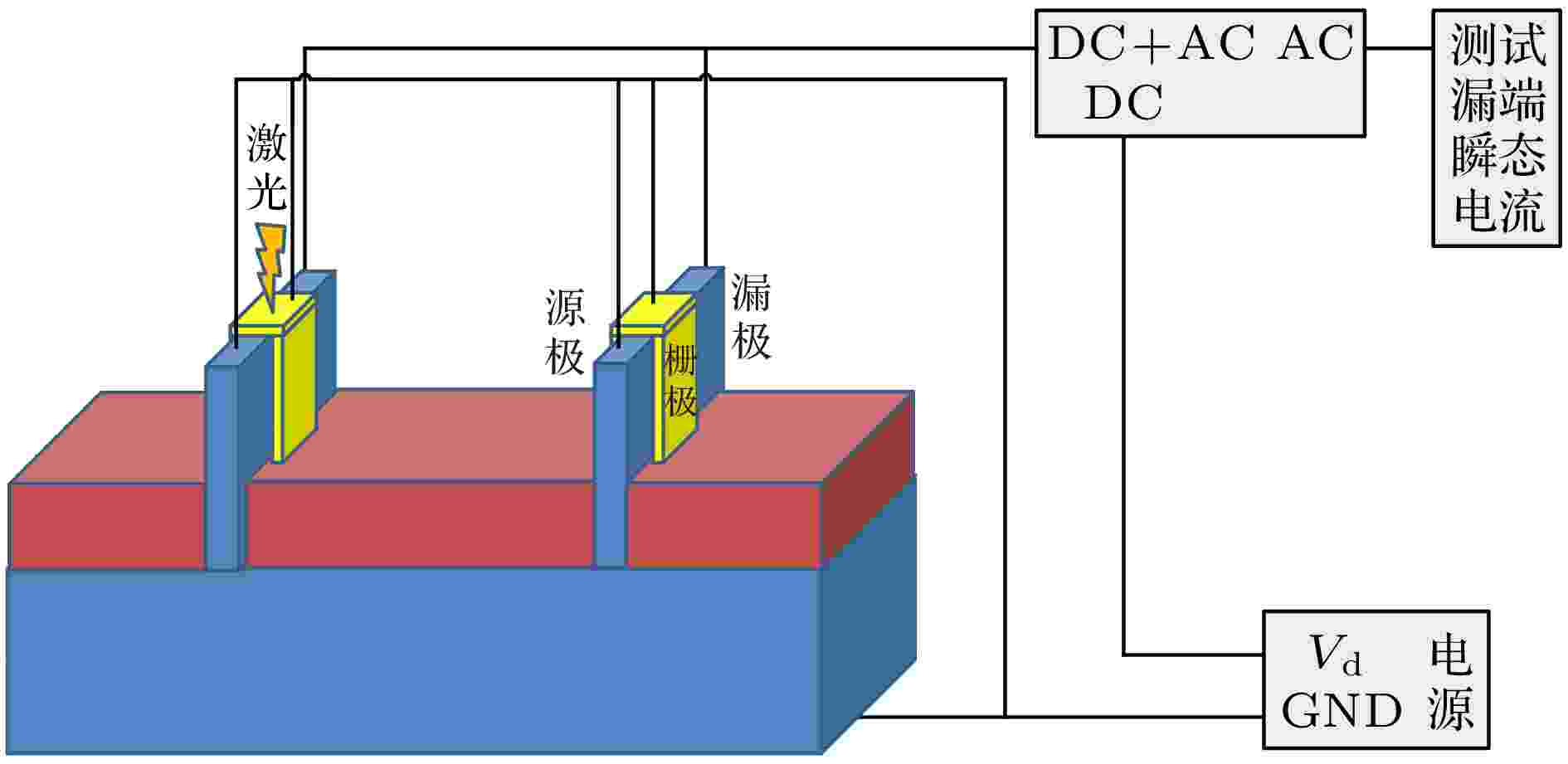

激光单粒子瞬态测试实验在中国科学院空间科学与应用研究中心完成, 使用的激光参数为: 激光脉宽为30 ps, 重复频率为1 kHz, 激光波长为1064 nm, 光子能量为1.168 eV, 光斑直径1 μm, 激光能量可从0 变化到10 nJ. 实验中采用激光能量为5 nJ, 根据相关报道中公式估算[20,21], 5 nJ激光在FinFET器件有源区的等效LET值大概为5 MeV·cm2/mg, 在近地辐射环境中该LET对应的粒子丰度较大[22], 因此利用5 nJ激光研究器件单粒子瞬态对评估器件在空间辐射环境中单粒子效应具有实际意义. 实验测试电路原理图如图2所示, 我们使用的是未封装的FinFET裸片, 偏压由电源通过探针输入. 激光从器件栅极顶部入射, 漏端产生的单粒子瞬态由高频探针引出, 经过电容器被示波器采集, 使用的示波器带宽为20 GHz, 采样率为80 GS/s. 由于FinFET器件在电路中工作状态有开态和关态两种, 开态偏压为漏端接高电平工作电压, 栅极接高电平阈值电压, 源衬底接地; 关态偏压为漏端接高电平工作电压, 栅、源和衬底接地. 开态时, 器件对单粒子瞬态不敏感, 目前研究器件单粒子瞬态时, 通常选择关态偏压. 因此, 实验过程中所加偏压为源、栅极和衬底接地, 漏端接器件工作电压Vd = 0.8 V. 图 2 实验测试电路图

图 2 实验测试电路图Figure2. The circuit schematic of experience.

图 3 4鳍不同栅长FinFET器件在5 nJ激光照射下的漏电流脉冲

图 3 4鳍不同栅长FinFET器件在5 nJ激光照射下的漏电流脉冲Figure3. Drain current transients for 4 fin FinFET of different gate length during the 5 nJ laser testing.

图 4 4鳍不同栅长器件在5 nJ激光入射下漏端收集电荷与时间关系

图 4 4鳍不同栅长器件在5 nJ激光入射下漏端收集电荷与时间关系Figure4. Drain charge collected for 4 fin FinFET of different gate length during the 5 nJ laser testing as a function of time.

图5显示鳍数量为2时, 100和30 nm栅长FinFET器件在5 nJ脉冲激光入射下漏电流瞬态脉冲, 由图5中数据可以看出, 栅长为100 nm双鳍FinFET器件比四鳍器件更快的形成平台区, 且平台区在2.5 ns时收集电荷量为0.25 pC, 远大于四鳍器件时的0.052 pC. 而栅长为30 nm双鳍器件漏电流在2.5 ns时依然保持在0.15 mA, 按照平台区电流的下降速度计算得到平台区电流将在10 ns左右减小到零, 这样栅长为30 nm FinFET器件平台区收集电荷将超过总收集电荷的65%, 平台区电流成为单粒子瞬态影响器件性能和工作状态的主要原因.

图 5 双鳍 100和30 nm栅长器件在5 nJ激光入射下漏电流脉冲

图 5 双鳍 100和30 nm栅长器件在5 nJ激光入射下漏电流脉冲Figure5. Drain current transients for 2 fin FinFET of different gate length during the 5 nJ laser testing.

综上, 在栅长为100 nm以下FinFET器件单粒子瞬态中平台区电流不可忽视, 且随着栅长变短, 平台区电流成为单粒子瞬态影响器件性能的主要原因, 因此, 对其产生机制的研究将变得非常重要. FinFET器件漏电流脉冲在平台区之前产生机制以漂移为主, 而对于平台区电流形成机制尚不明确. 接下来通过三维TCAD 重离子单粒子效应仿真研究器件单粒子瞬态漏电流脉冲平台区产生机理.

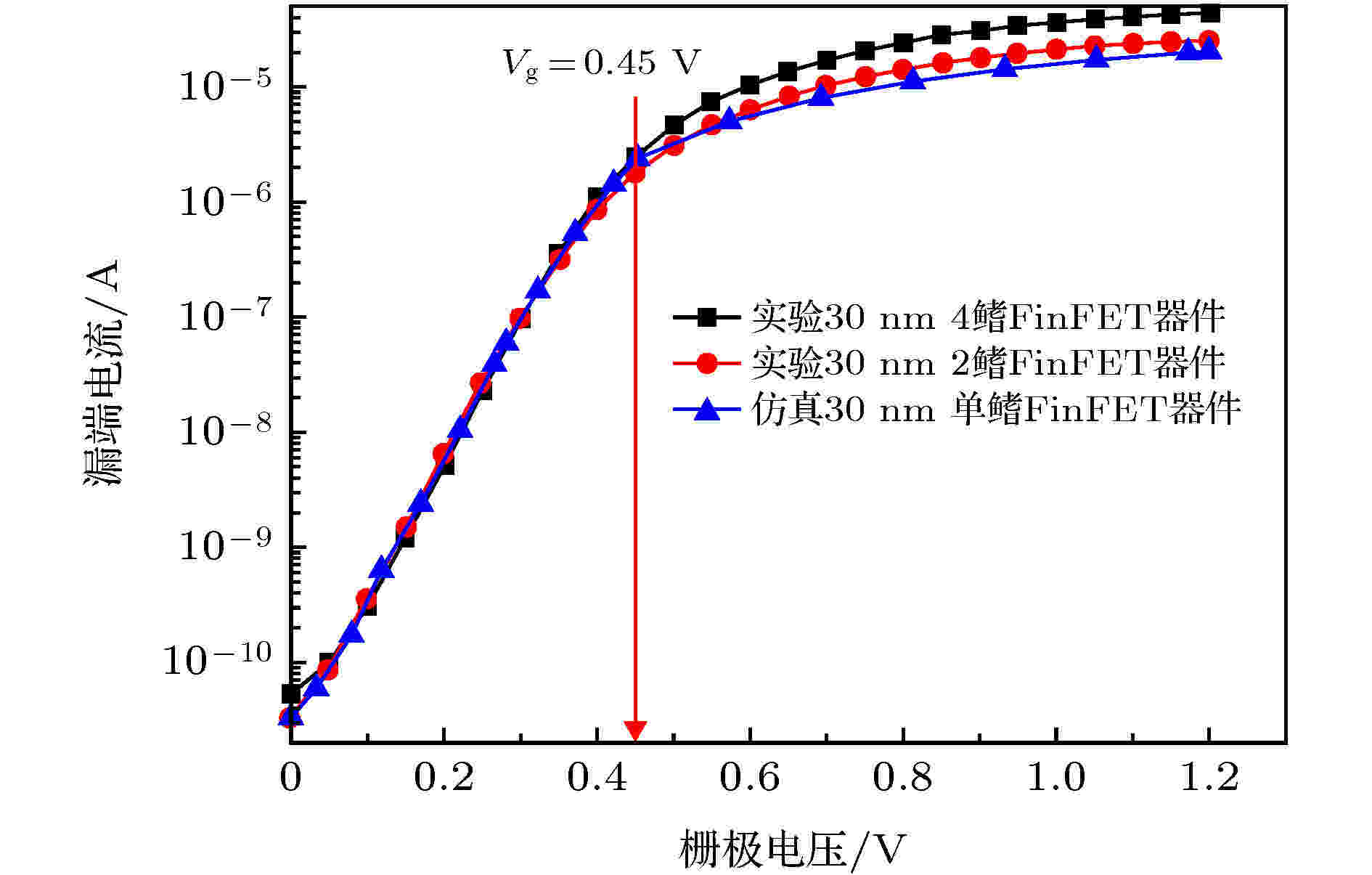

由于实验中双鳍和四鳍器件是通过单鳍器件并行排列组成, 因此多鳍结构虽然会对器件单粒子瞬态有影响, 但是不同鳍数量器件产生单粒子瞬态的物理机理一致, 从实验结果中也可以看出双鳍器件和四鳍器件漏电流瞬态波形基本一致. 因此仿真中采用单鳍FinFET器件, 以便更清楚地研究纳米FinFET器件栅长变短时单粒子瞬态平台区产生机理. 仿真器件模型通过与实验器件相同工艺建模得到, 除了鳍数量, 器件结构和掺杂参数都与实验器件相同, 并通过校准使得单鳍FinFET仿真器件与实验所采用的双鳍和四鳍FinFET器件具有相同的工作电压和阈值电压. 图6给出了在漏端电压为0.8 V时, 栅长为30 nm单鳍仿真器件和2鳍、4鳍实验器件转移特性曲线

图 6 单鳍FinFET仿真器件和2鳍、4鳍FinFET实验器件

图 6 单鳍FinFET仿真器件和2鳍、4鳍FinFET实验器件

Figure6.

偏压条件与实验相同, 漏端反偏0.8 V, 源、衬底和栅极接地. 重离子垂直从器件顶部入射, 在器件中产生电荷密度为

2

4.1.衬底扩散对漏电流脉冲的影响

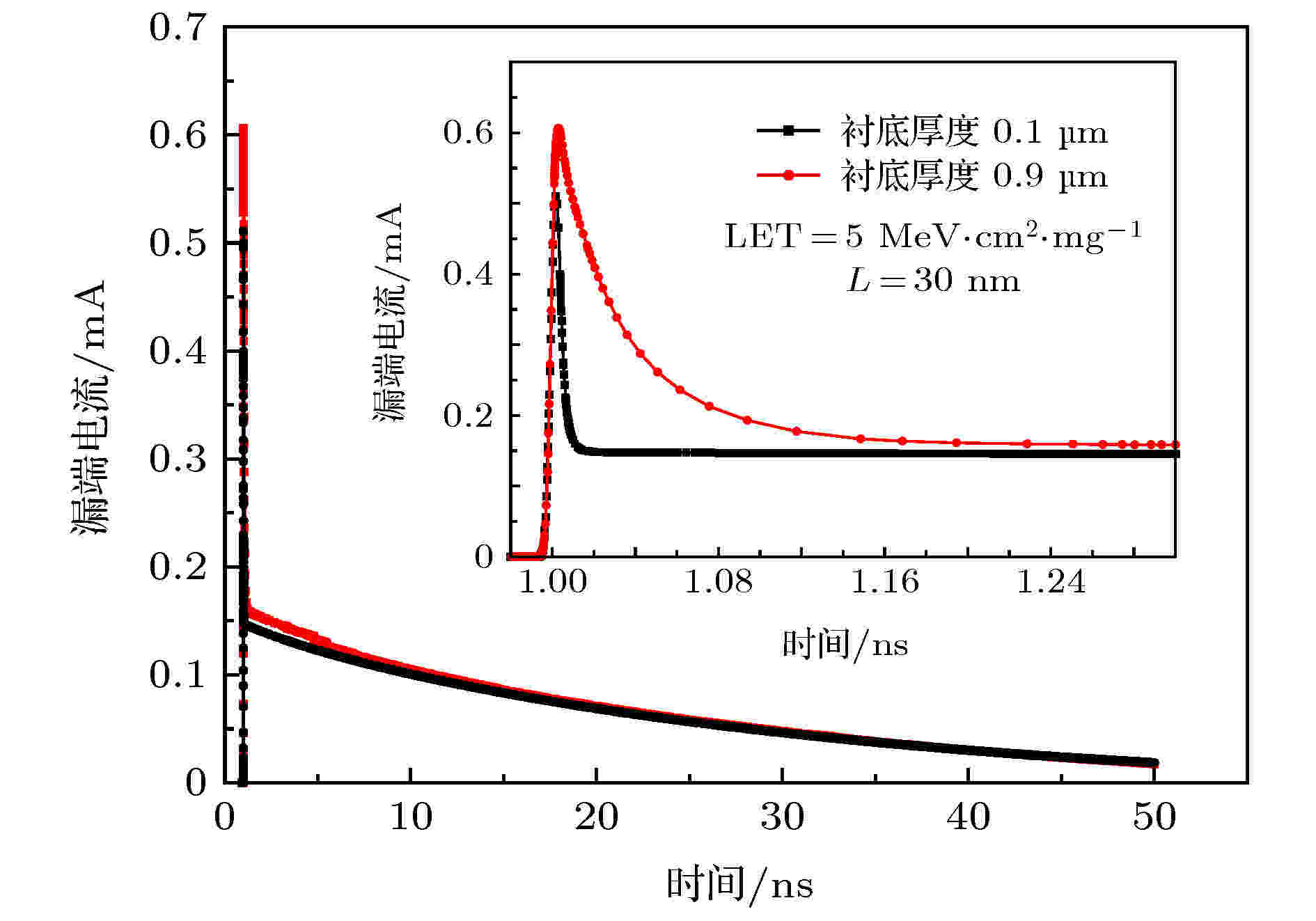

首先研究平台区电流是否与衬底厚度有关. 建立有源区结构完全相同, 衬底厚度分别为0.1和0.9 μm FinFET器件, 器件栅长为30 nm, 入射离子束特征半径取为50 nm, LET值为5 MeV·cm2·mg–1. 图7为两种器件在重离子入射下的漏电流脉冲, 可以看出衬底厚度增大引起的扩散电流主要作用在1.12 ns以前的漏电流下降阶段, 使得漏电流脉冲脉宽增大, 在1.12 ns以后两种衬底厚度器件漏电流基本相同, 电流维持在0.15 mA缓慢下降, 这说明衬底扩散会增大电流脉冲宽度, 但不影响拖尾平台区电流. 为了仿真更快速, 接下来仿真中我们采用器件衬底厚度为0.1 μm. 图 7 TCAD模拟下衬底厚度为0.1和0.9 μm, 栅长为30 nm FinFET器件漏电流脉冲

图 7 TCAD模拟下衬底厚度为0.1和0.9 μm, 栅长为30 nm FinFET器件漏电流脉冲Figure7. Drain current transients for FinFET of different substrate thickness from TCAD simulation.

2

4.2.源漏导通对漏电流脉冲的影响

比较不同栅长器件在相同重离子入射下单粒子瞬态响应和器件内部电子浓度和电势分布变化, 得到漏电流脉冲尾部平台区形成机理; 结合30 nm器件在不同离子束宽度入射下单粒子瞬态响应, 得出平台区电流与器件结构及入射条件关系; 比较不同入射位置, 漏电流脉冲平台区变化, 得到平台区电流与入射位置关系.3

4.2.1.不同栅长

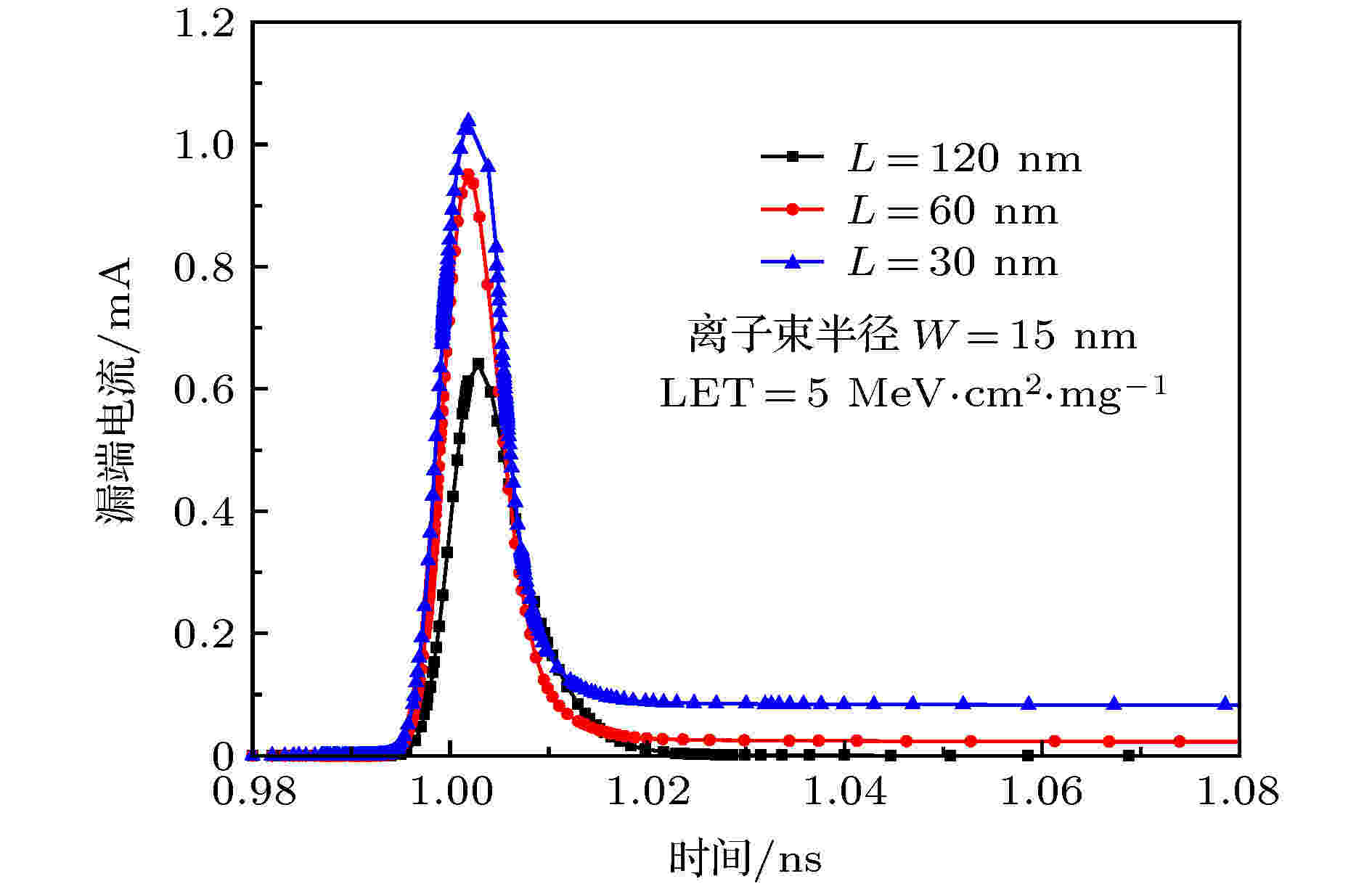

对栅长为30, 60和100 nm FinFET器件进行重离子注入. 重离子垂直于栅极入射, 离子束特征半径为15 nm, LET值为5 MeV·cm2·mg–1, 离子束中心入射时间为1 ns, 其他参数为默认值.图8为三种器件在重离子入射下漏电流脉冲, 可以看出栅长30和60 nm器件, 漏电流脉冲尾部存在平台区, 平台区电流分别为0.07和0.02 mA, 而栅长100 nm器件漏电流脉冲不存在尾部平台区, 在1.04 ns时其电流值为10–5 mA. 说明在重离子仿真中随着栅长变短, 漏电流脉冲尾部出现平台区, 且平台区电流值逐渐增大, 这与激光单粒子实验得到规律基本相同; 仿真得到的漏电流脉冲宽度小于实验结果, 主要是因为仿真器件衬底厚度取0.1 μm, 缺少了扩散电流的影响.

图 8 TCAD模拟下不同栅长FinFET器件漏电流脉冲

图 8 TCAD模拟下不同栅长FinFET器件漏电流脉冲Figure8. Drain current transients for FinFET of different gate length from TCAD simulation.

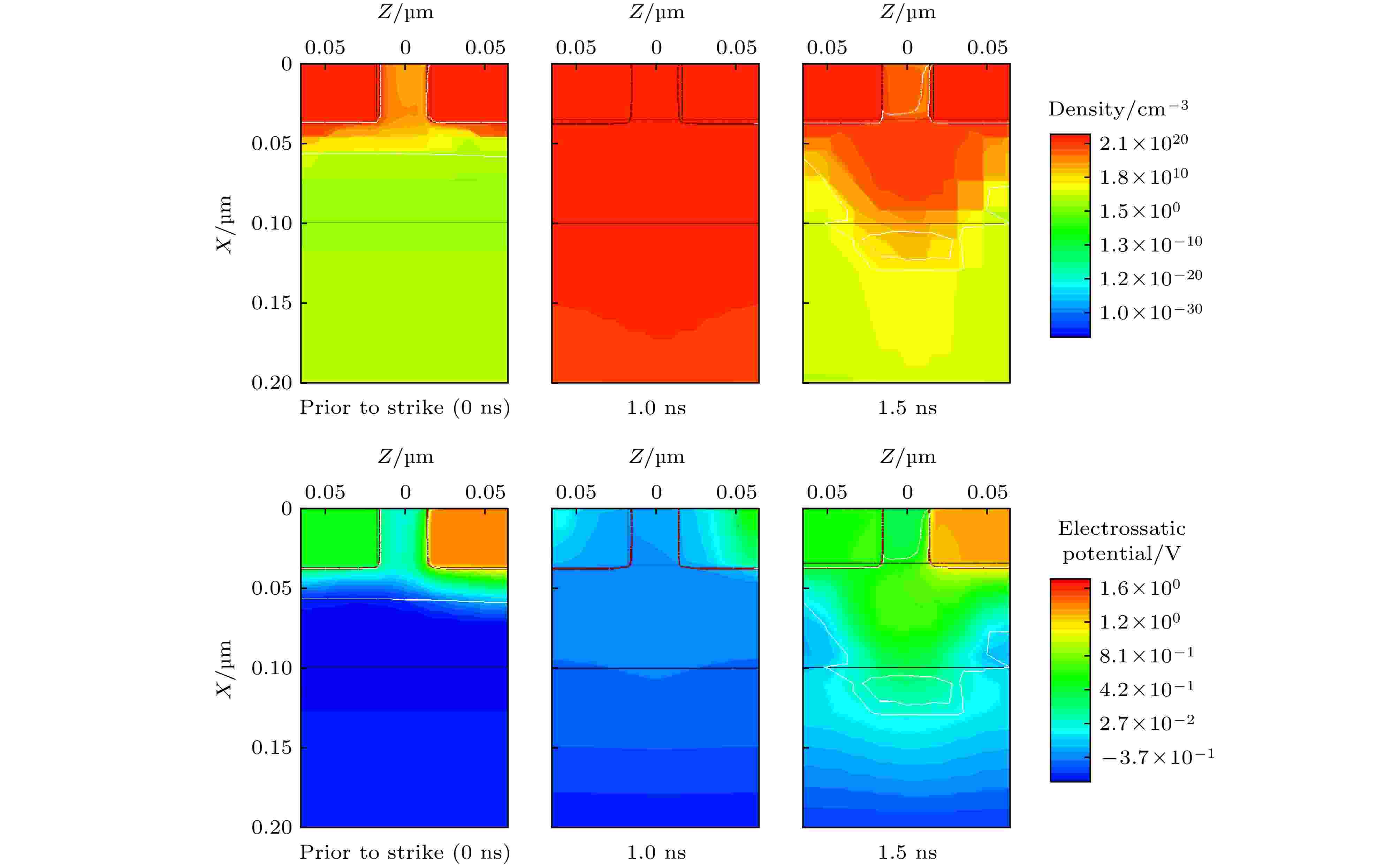

比较栅长30 nm FinFET器件在漏电流瞬态脉冲形成过程中电子浓度和电势变化. 特征半径为15 nm的离子束在器件中的电荷产生率为图9中实心原点连线所示, 红色和黑色圆点分别代表线性坐标和指数坐标. 其在半径38 nm内都可电离出1 × 1030以上的电子空穴对. 所以特征半径15 nm重离子束会在栅长30 nm器件鳍区、部分源区、部分漏区以及他们下方的体区产生高浓度电子空穴对. 图10为重离子入射前(0 ns)、入射中(1 ns)和入射后(1.5 ns) 30 nm器件中电子浓度和电势分布. 对照漏电流脉冲波形的时间特性和电子浓度变化, 重离子入射栅长30 nm器件时, 在器件中产生高浓度电子空穴对. 由于器件偏压和不同区域掺杂不同, 电子由漏-体结和源-体结收集, 而空穴由衬底漂移收集, 当重离子入射结束, 沟道区由于体积较小且与源漏直接接触, 该区产生的高浓度电子被源漏端快速收集; 衬底区产生高浓度电子由于偏压关系向上漂移, 使得电子浓度减小; 而沟道stop区产生的高浓度电子虽然也会被源漏收集, 但是因为不直接接触源漏, 收集速度较慢, 而且有来自衬底的飘移电子的补充, 衬底电子漂移到沟道stop区, 由于漏端偏压在沟道stop区产生的电场不是指向沟道, 而是指向漏端, 因此向沟道漂移的电子减少, 所以最终只在沟道stop留下高浓度电子, 如图10中FinFET器件在1.5 ns时的电子浓度分布. 该区域电子浓度远高于空穴浓度, 使得其性质与n型半导体相同, 将源漏导通. 源漏导通使得沟道stop区电势升高, 电势差造成的电场力抑制了高浓度电子向四周扩散, 所以源漏导通状态维持较长时间. 而由于漏端偏压高于源端, 则电子不断的由源端流向漏端, 形成漏电流脉冲的平台区.

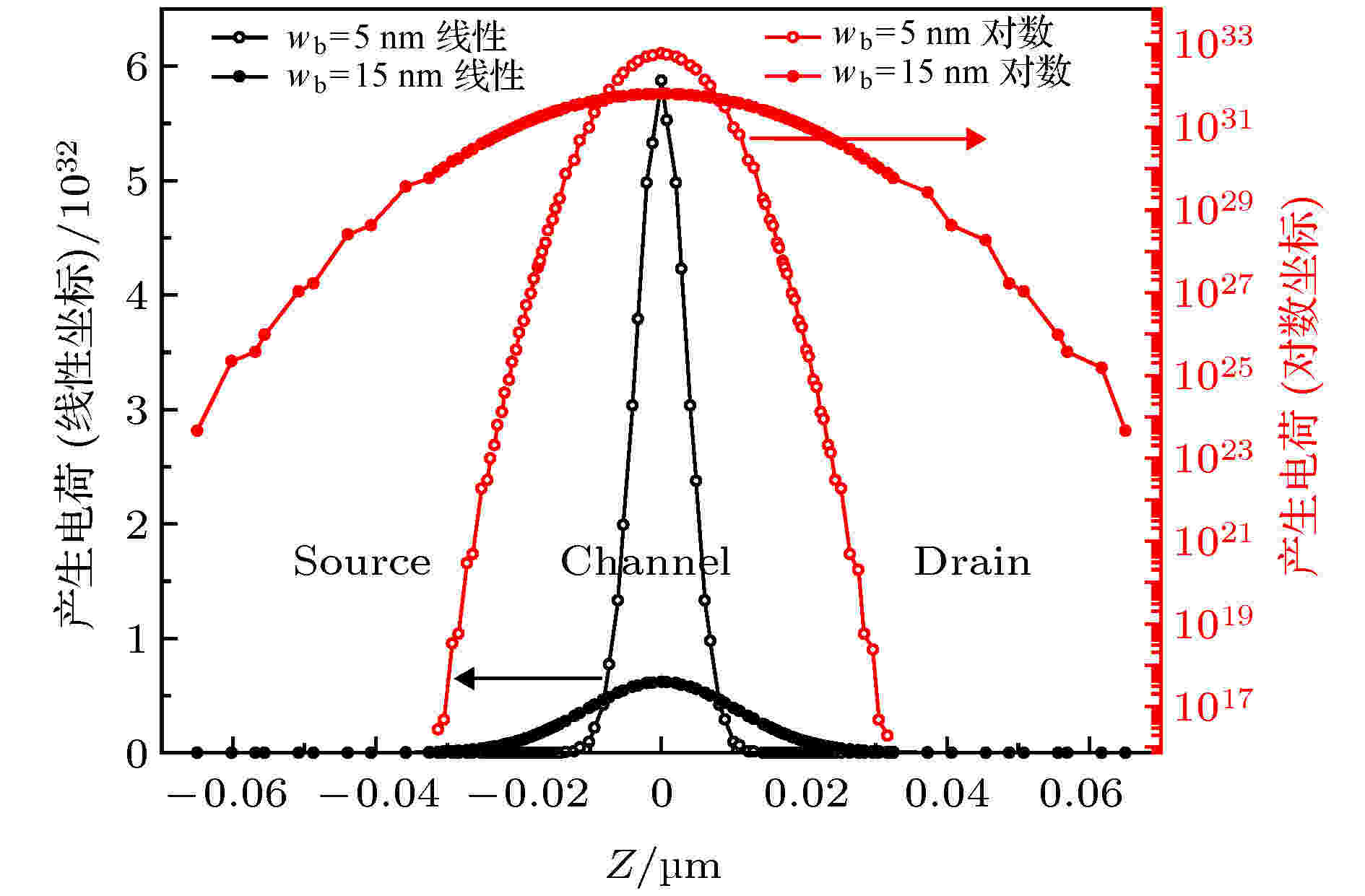

图 9 重离子产生的电荷径向分布

图 9 重离子产生的电荷径向分布Figure9. Charge generation radial distribution of heavy ion

图 10 重离子入射前、入射中和入射后30 nm FinFET器件内部电子浓度和电势分布

图 10 重离子入射前、入射中和入射后30 nm FinFET器件内部电子浓度和电势分布Figure10. Temporary evolution of electronic density and electrostatic potential for a 30 nm FinFET.

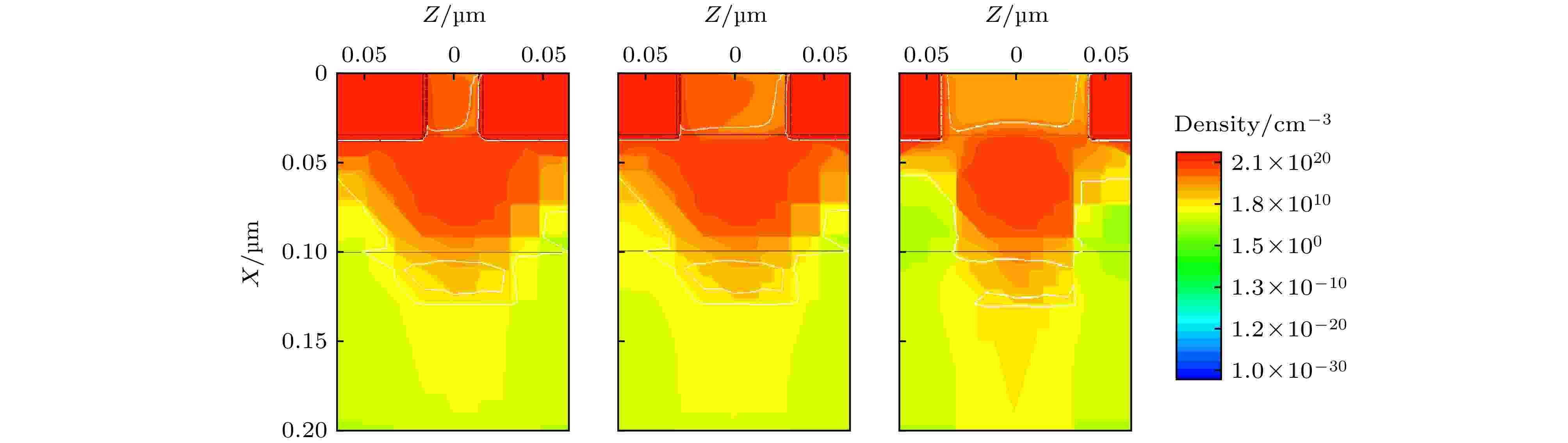

比较三种栅长器件1.5 ns时电子浓度分布, 如图11所示, 可以看出三种器件沟道stop区电子浓度都高于周围区域, 栅长30和60 nm器件源和漏被沟道stop内高浓度电子所导通, 在漏电流脉冲尾部形成平台区电流. 但是在栅长为100 nm时, 由于栅长较长, 源漏距离远, 高浓度电子区域不能将源漏导通, 所以100 nm器件漏电流脉冲不存在拖尾.

图 11 不同栅长FinFET器件在1.5 ns时的电子浓度

图 11 不同栅长FinFET器件在1.5 ns时的电子浓度Figure11. Electronic density for FinFET of different gate length at 1.5 ns.

3

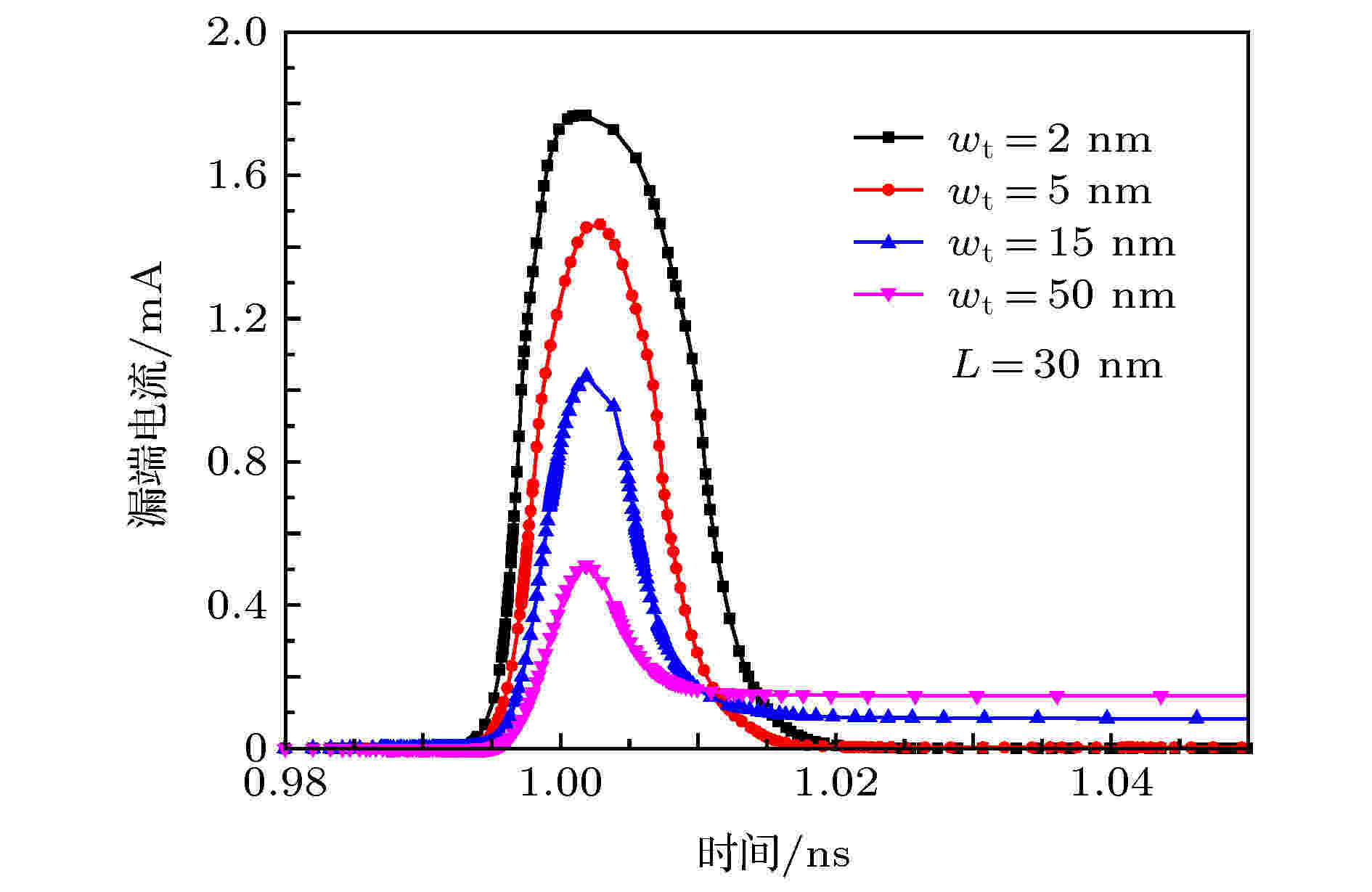

4.2.2.不同离子束半径

取离子束特征半径wt分别为50, 15, 5和2 nm来研究其对漏电流脉冲的影响. 在LET相同时, 4种不同离子束宽度在栅长30 nm FinFET中造成的漏电流脉冲瞬态为图12所示, 由图12可以看出, 相同LET时, 随着入射粒子束变宽, 漏电流脉冲幅值变小. 相比于离子束半径为2和5 nm, 当离子束特征半径为15和50 nm时, 漏电流脉冲出现平台区, 且50 nm时漏电流脉冲尾部平台区电流值大于15 nm. 图 12 30 nm器件在不同特征半径重离子入射下漏电流脉冲

图 12 30 nm器件在不同特征半径重离子入射下漏电流脉冲Figure12. Drain current transient for 30 nm FinFET when heavy ion incident device with different radius.

对于脉冲幅值变化解释: 图9所示为离子束宽度为5和15 nm时器件中电荷产生率径向分布, 相同LET, 入射离子束越窄, 在离子束中心处产生的电子空穴对浓度越高, 则漂移电流越大, 漏电流脉冲幅值越大.

而当重离子束特征半径在5 nm以上时器件源漏将会被重离子电离产生的电子导通, 其特征半径越大, 导通现象越严重. 源漏导通就会导致拖尾平台区电流, 所以在图12中, 特征半径在5 nm以上时, 漏电流脉冲尾部存在平台区, 且平台区电流值随着特征半径增大而增大. 特征半径为2和5 nm时, 电离产生的电子较窄, 不能将源漏导通, 所以其漏电流在1.04 ns时就恢复到重离子入射前状态. 结合不同栅长器件源漏导通现象, 得到在垂直栅极入射时, 当入射离子束特征宽度大于入射器件栅长的1/3时, 源漏就会出现导通. 因为重离子离子束在3倍的特征宽度范围内可以电离出导通器件源漏的高浓度电子.

3

4.2.3.重离子入射位置

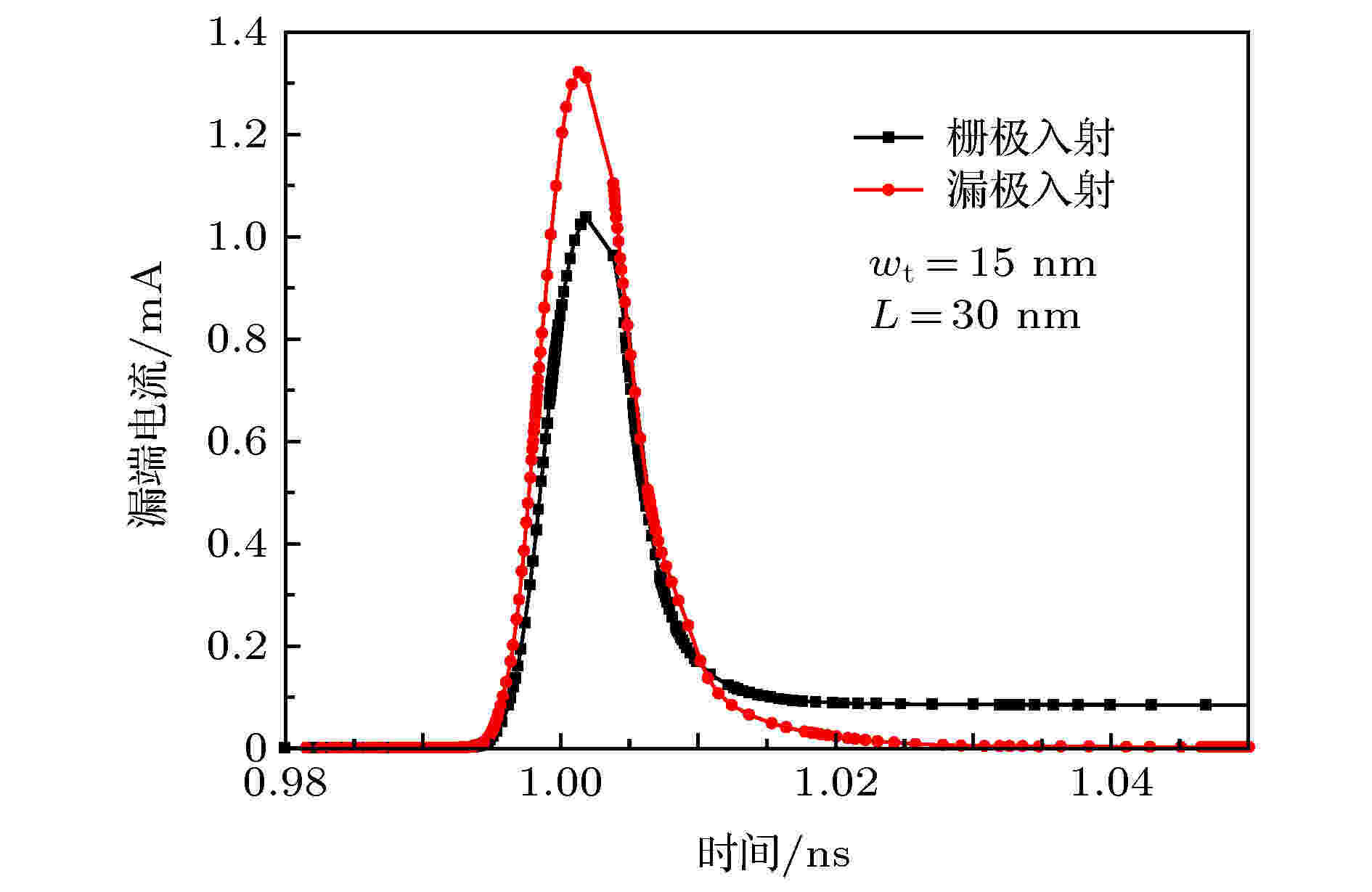

图13为重离子垂直入射栅长30 nm器件漏、栅极时漏电流脉冲波形. 当重离子在栅极入射时会产生较大的拖尾平台区电流, 而在漏极入射时, 漏电流在1.05 ns时基本恢复到入射前状态. 该结果和上述理论相符, 重离子入射栅极, 源漏导通导致漏电流脉冲平台区; 而重离子入射漏极时, 在漏极中心电离产生高浓度电子空穴对, 没有覆盖到源极, 不能将源漏导通, 所以漏电流会很快降低. 因此对于同一器件, 入射位置靠近栅极中心, 器件更容易发生源漏导通. 图 13 当重离子从栅极和漏极入射时, FinFET器件的漏电流脉冲

图 13 当重离子从栅极和漏极入射时, FinFET器件的漏电流脉冲Figure13. Drain current transient for a FinFET when heavy ion incident at drain and gate.