目前,胚胎电子细胞阵列中故障的检测和定位主要依靠冗余设计和内建自测试(Built-in Self Test, BIST)。其中冗余设计按照冗余程度,可分为针对胚胎电子细胞中特定模块的冗余设计和针对电子细胞整体的冗余设计。文献[1-2]对电子细胞的功能模块进行冗余设计,可检测功能模块发生的故障。文献[13]对电子细胞阵列中互连资源进行冗余设计,可检测互连资源中发生的故障;文献[14]提出一种先天性免疫系统,通过添加免疫层实现对电子细胞陈列的故障检测和定位。文献[15-16]从整体上对电子细胞阵列进行冗余设计,利用阵列中空闲电子细胞设计在线故障检测结构。

在采用BIST的故障检测和定位方法中,文献[17]提出一种人工免疫系统,采用负选择算法和Roving STARs[18]方法来检测和定位故障。文献[19-20]提出一种原核电子细胞结构,电子细胞间通过链状总线连接,采用BIST方法实现故障的检测和定位。文献[21]采用双模冗余设计和BIST方法对工作层细胞进行故障检测和定位。

总的来说,基于冗余设计的故障检测和定位方法受冗余程度的限制很大。如果冗余程度很小,则可检测和定位的故障就非常有限; 如果冗余程度很大,则用于检测的硬件消耗就很大。而基于BIST的故障检测和定位方法则受电子细胞阵列结构或电子细胞结构的限制,一种方法通常仅针对特定的阵列或细胞结构有效,通用性和适用范围有限。因此,针对胚胎电子细胞阵列,本文首先提出一种新的测试结构,对测试结构进行了详细设计。然后,基于新的测试结构,提出了一种通用的故障检测和定位方法,并分析了测试结构的硬件消耗。仿真和分析结果证明了方法的有效性,为解决胚胎电子细胞阵列的故障检测和定位问题提供了一个新的思路。

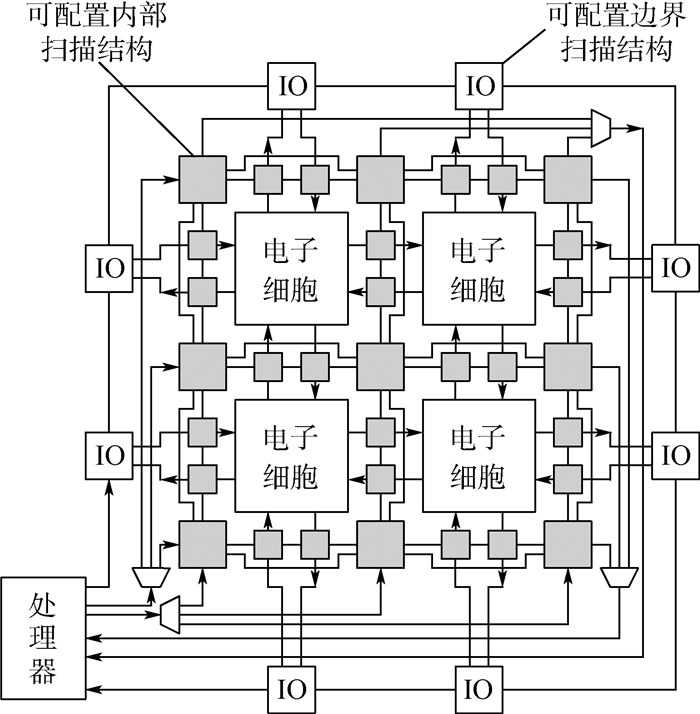

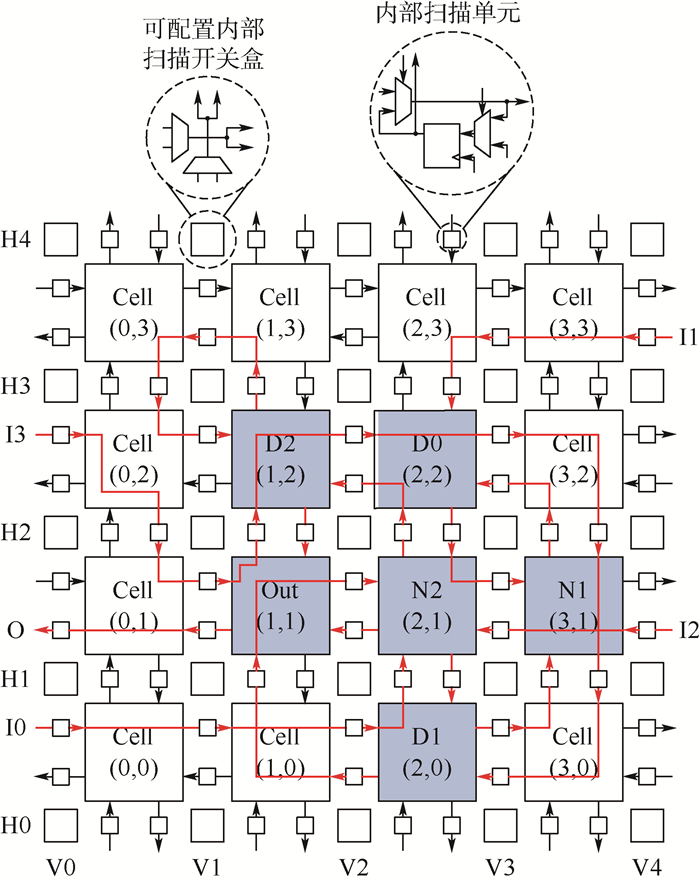

1 具有测试结构的胚胎电子细胞阵列 常见的胚胎电子细胞阵列如图 1所示。每个电子细胞内都包含一个专门设计的自检单元,电子细胞阵列的故障检测和定位主要依靠单个电子细胞的故障自检实现。这种方法对单个电子细胞的要求很高,为了达到一定的故障检测能力,自检单元结构通常比较复杂,导致细胞中用于故障检测的硬件消耗比较大。而且自检单元并没有统一的设计方法,故障检测能力也很有限,对于连线资源故障、开关盒故障和时序故障等,设计出有效的自检单元结构也比较困难。

|

| 图 1 胚胎电子细胞阵列 Fig. 1 Embryonics array |

| 图选项 |

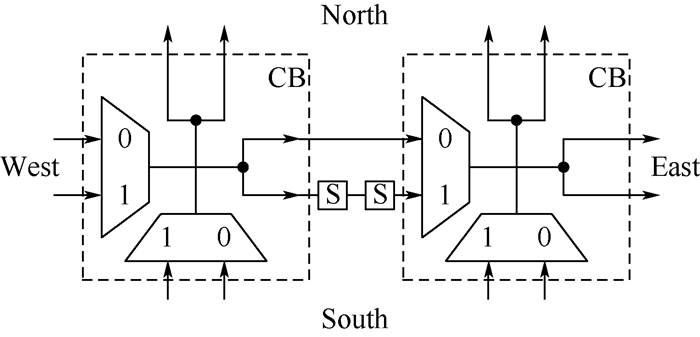

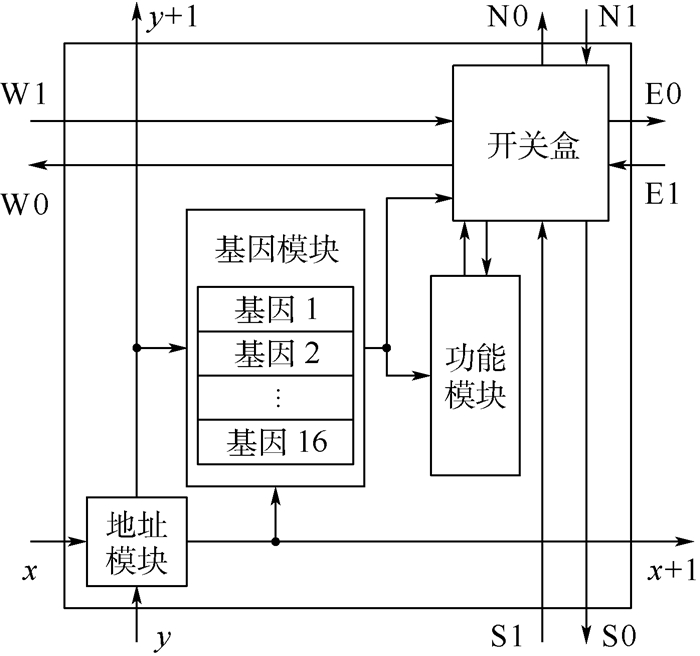

因此,本文将测试资源从电子细胞中分离出来,集中处理,提出一种新的测试结构,如图 2所示。图中IO表示具有边界扫描功能的双向输入输出端口,本文中称为可配置边界扫描单元,所有的可配置边界扫描单元串联构成可配置边界扫描结构。在可配置边界扫描结构与电子细胞之间,以及电子细胞周围,阵列中显示为阴影部分的结构称为可配置内部扫描结构。可配置边界扫描结构和可配置内部扫描结构一起构成了胚胎电子细胞阵列的测试结构。因此,具有测试结构的胚胎电子细胞阵列总体上可分为测试结构、处理器和电子细胞3部分。其中测试结构是实现胚胎电子细胞阵列故障检测与定位的硬件基础,是本文研究的重点。处理器主要实现对测试结构的测试控制和测试数据的分析。电子细胞的具体结构可以是任意的,阵列中电子细胞的数量以及每个电子细胞输入输出端口个数仅影响测试结构中测试单元的数量。为了方便分析,本文采用通用布线矩阵(General Routing Matrix, GRM)模型描述电子细胞结构,具体结构见图 3。

|

| 图 2 胚胎电子细胞阵列中的测试结构 Fig. 2 Testing architecture in embryonics array |

| 图选项 |

|

| 图 3 电子细胞结构 Fig. 3 Electronic cell architecture |

| 图选项 |

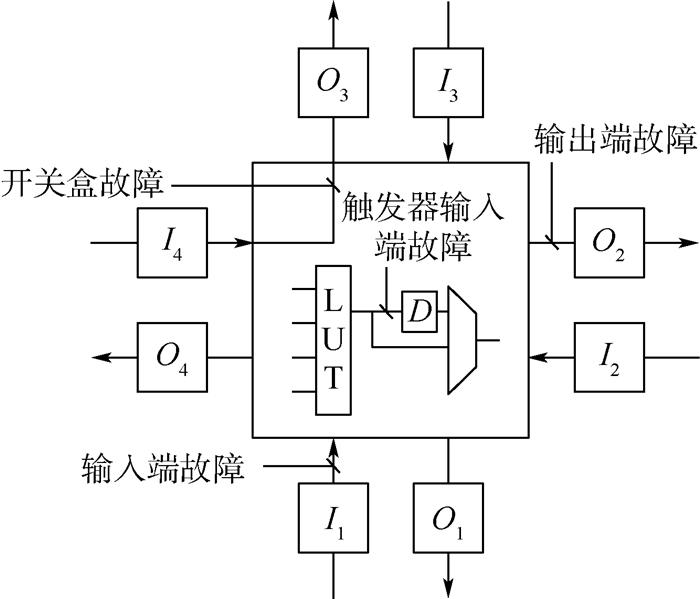

如图 3所示,可将电子细胞分为开关盒和功能部分。开关盒实现电子细胞间的信号传递,电子细胞的功能输入和输出都需要经过开关盒;功能部分主要实现电子细胞的逻辑功能,一般情况下由功能模块、基因存储模块、地址模块等组成。新的测试结构将电子细胞作为“黑盒”,通过对电子细胞开关盒的输入和输出信号,以及电子细胞内部时序单元的状态信号进行监测和分析来判断电子细胞的功能和故障。

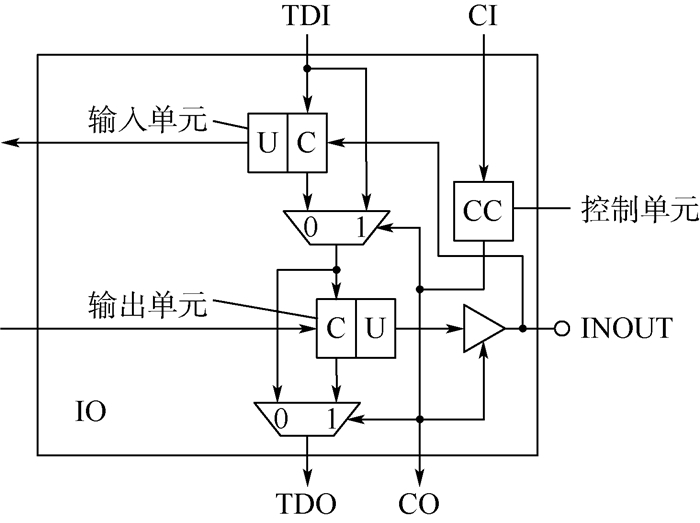

2 测试结构及具体构成 2.1 可配置边界扫描结构 可配置边界扫描结构由可配置边界扫描单元串联构成,是实现故障检测的硬件基础。本文在IEEE 1149.1—2013[22]的基础上,为了进一步减少扫描链长度,提高扫描速度,设计了一种新的可配置边界扫描单元结构,见图 4。

|

| 图 4 可配置边界扫描单元结构 Fig. 4 Configurable boundary scan cell architecture |

| 图选项 |

可配置边界扫描单元主要由输入单元、输出单元、控制单元、三态缓冲器和多路选择器等构成。输入单元和输出单元即为IEEE 1149.1—2013中定义的BC_1型扫描单元结构,图 4中仅给出了BC_1型扫描单元的简化模型[22],其中U代表BC_1型扫描单元中的更新寄存器,C代表BC_1型扫描单元中的捕获(移位)寄存器。与三态缓冲器相连接的INOUT端口代表电子细胞阵列的输入输出端口,为了减少端口数量,将所有的端口都设计为双向端口。CC代表控制单元,由单个触发器构成,主要完成对边界扫描单元中的多路选择器和三态缓冲器的控制。CI为来自上一级控制单元的移位输入,CO为送往下一级控制单元的移位输出,整个边界扫描链中所有的控制单元串联构成一个控制寄存器。控制寄存器可在电子细胞阵列进行功能分化时完成配置。TDI为扫描数据输入,TDO为扫描数据输出。在控制单元的控制下,每个边界扫描单元内,扫描数据仅经过1个触发器,因此扫描速度得到提升。

2.2 可配置内部扫描结构 可配置内部扫描结构是实现细胞级故障定位的硬件基础,具体结构见图 5。图中S代表内部扫描单元,CB代表可配置内部扫描开关盒。其中内部扫描单元分布在电子细胞开关盒之间相互连接的连线上。所有的内部扫描单元与可配置内部扫描开关盒构成可配置内部扫描网络。另外,为了对时序电路进行有效的测试,将电子细胞中所有的触发器设计为具有扫描功能的触发器,所有触发器串联起来,构成可配置内部扫描链,如图 5中虚线所示。因此,可配置内部扫描结构总体上可以分为可配置内部扫描网络和可配置内部扫描链两部分。

|

| 图 5 可配置内部扫描结构 Fig. 5 Configurable inner scan architecture |

| 图选项 |

如图 5所示,扫描数据在数据分配器的控制下,可以从水平和垂直2个方向输入可配置内部扫描网络,并在数据选择器的控制下,从水平和垂直2个方向输出扫描结果,实现对可配置内部扫描网络中任意行和列的扫描。因此,可配置内部扫描结构具有一定的自检能力。更重要的是,在可配置内部扫描链的配合下,任意电子细胞的输入、输出和触发器状态信息都可以通过可配置内部扫描结构输出,为故障的定位带来极大便利。

2.2.1 可配置内部扫描网络 可配置内部扫描网络中内部扫描单元的具体结构如图 6所示。

|

| 图 6 内部扫描单元结构 Fig. 6 Inner scan unit architecture |

| 图选项 |

内部扫描单元由2个多路选择器和1个触发器构成,具有故障自检能力。DI、DO分别为数据输入、输出端口;SDI、SDO分别为扫描数据输入、输出端口;US Clock为扫描(捕获)时钟;UMode为工作/检测模式选择信号;UShift为移位控制信号。内部扫描单元在UMode和UShift信号控制下,可以实现检测、移位、捕获等功能。当UMode为1时,内部扫描单元处于工作模式,此时,如果UShift为1,则内部扫描单元可实现数据捕获;如果UShift为0,则内部扫描单元可实现扫描数据的移位输入和输出。当UMode为0时,内部扫描单元处于检测模式,此时如果UShift为1,经过1个扫描时钟后,扫描数据由SDO端口送出,可以对发生在触发器输出端至输入端回路上的固定型故障进行自检;如果UShift为0,DO端输出触发器中的扫描数据,此时扫描数据可作为测试激励输入电子细胞。因此,基于内部扫描单元结构,可以实现非常灵活的测试。

图 7中可配置内部扫描开关盒由2个2选1多路选择器组成。本文中设定扫描数据的水平移位方向为由西(West)向东(East),垂直移位方向为由南(South)向北(North)。2个相邻的可配置内部扫描开关盒之间有2条连接通路,分别为经过内部扫描单元的扫描通路和直连的长线。在电子细胞阵列进行细胞(行/列)移除自修复的过程中,可将被移除细胞(行/列)周围的可配置内部扫描开关盒配置为通过直连的长线连接,保证了扫描功能不受自修复过程的影响。

|

| 图 7 可配置内部扫描开关盒 Fig. 7 Configurable inner scan switch box |

| 图选项 |

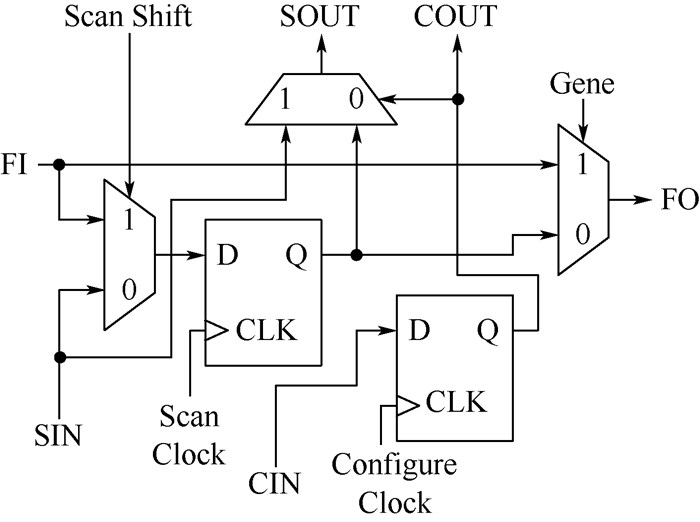

2.2.2 可配置内部扫描链 时序电路的测试和诊断是比较困难的,常用的可测性设计方法是将时序电路中的触发器串联起来构成扫描链,将时序电路的测试问题转化为组合电路的测试问题来解决。在电子细胞阵列中,实现时序逻辑功能的基本单元是电子细胞中的触发器,因此,将电子细胞中的触发器均设计为具有扫描功能的扫描触发器,具体结构如图 8所示。其中FI和FO分别为电子细胞中组合逻辑功能输出和电子细胞的功能输出。Gene为每个电子细胞中存储的基因,在Gene的控制下,每个电子细胞可以实现一定的组合或时序逻辑功能。SIN为扫描数据输入,SOUT为扫描数据输出。Scan Shift为移位控制信号。Scan Clock为工作(扫描)时钟。与配置时钟Configure Clock连接的是控制触发器,输入为CIN,输出为COUT。

|

| 图 8 电子细胞中的扫描触发器结构 Fig. 8 Scan flip-flop in electronic cell architecture |

| 图选项 |

在控制触发器的控制下,扫描触发器有2种状态,即扫描状态和快速通过状态。当控制触发器的输出COUT为0时,扫描触发器处于扫描状态,实现扫描数据移位功能;当COUT为1时,扫描触发器处于快速通过状态,扫描数据不经过触发器,直接从SOUT端输出。

3 故障检测方法 3.1 固定型故障模型 固定型故障是一种非常常用的故障模型,能够反映许多实际中出现的故障,因此,本文主要针对固定型故障进行研究。在对胚胎电子细胞阵列进行寄存器传输级(Register Transfer Level, RTL)的故障分析时,按照故障产生的位置,可分为电子细胞的输入端固定型故障和输出端固定型故障,如图 9所示,Cell 1~Cell 4为电子细胞。

|

| 图 9 故障模型 Fig. 9 Fault model |

| 图选项 |

图 9(a)为电子细胞Cell 1的输出端固定型故障(s-a-0或s-a-1),产生的故障直接影响所有与细胞输出相连接的细胞,在实际中相当于电子细胞损坏、电子细胞与开关盒间连线开路、开关盒故障等故障情况。图 9(b)为电子细胞Cell 2的输入端故障,电子细胞的输入端为固定的逻辑值0或1(s-a-0或s-a-1),在实际中相当于电子细胞的某输入端开路、电子细胞与电子细胞间的连线开路、开关盒故障等故障情况。

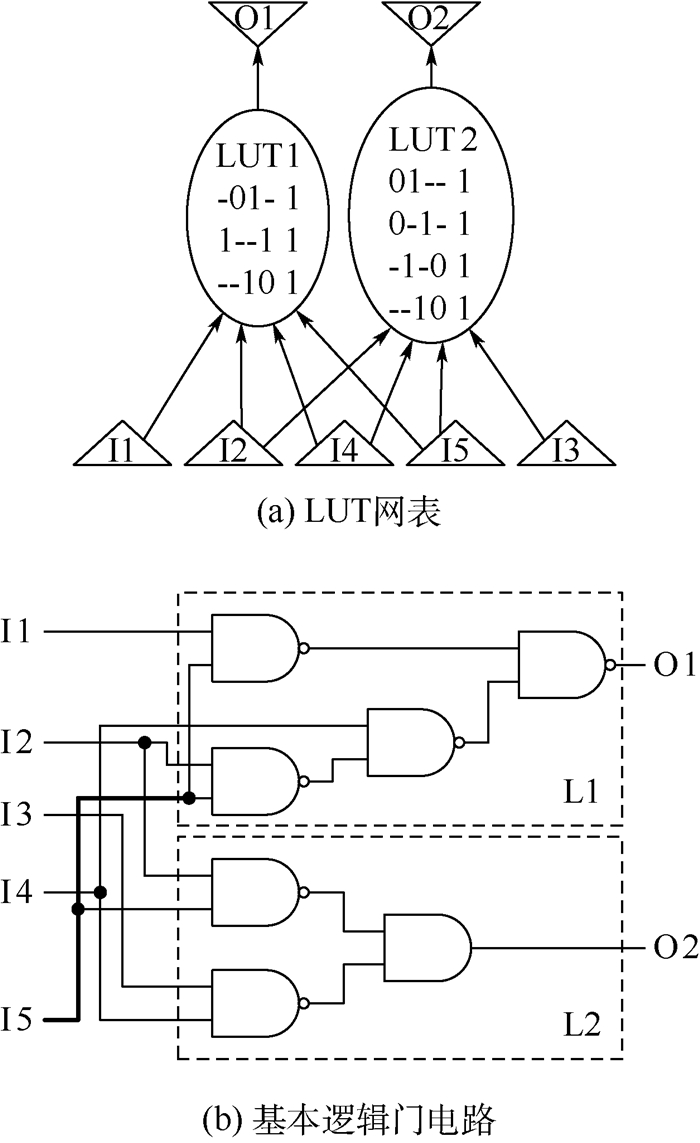

3.2 测试向量生成方法 RTL级故障检测方法中,核心的技术是测试向量生成。但是目前已有的测试向量生成方法,处理的对象主要是由基本逻辑门(如与门、或门、非门、与非门、或非门等)构成的电路,而电子细胞的功能单元一般采用可编程查找表(Look-up Table, LUT)实现,因此,针对LUT型功能单元如何有效的生成测试向量是一个值得研究的关键问题。为了有效解决这一问题,并充分利用目前已有的技术和方法,本文采用一种等价变换的方法,首先对LUT单元进行逻辑等价变换,转化为逻辑等价的基本逻辑门电路,然后再使用常规的自动测试向量生成(Automatic Test Pattern Generation, ATPG)工具产生测试向量。

以C17电路为例说明等价变换的具体方法,如图 10所示,I1~I5为电路的5个输入,O1、O2为电路的2个输出。图 10(a)为C17电路的LUT网表,图 10(b)为图 10(a)经过等价变换得到的基本逻辑门电路。在等价变换的过程中,图 10(a)中的LUT1、LUT2单元分别变换为图 10(b)中由基本逻辑门构成的L1、L2电路模块,L1、L2电路模块分别保留对应LUT单元的输出端、输入端名称。因此,LUT1和LUT2的输入端和输出端故障可等效为L1和L2模块中的输入端和输出端故障。在设置输入端故障时,当一个输入端在某模块中连接多个基本逻辑门时,应将所有相同的输入端合并。见图 10(b),I5在L1模块中连接2个与非门,将这2个与非门相同的输入端合并,在设置L1输入端故障时,这2个与非门同时受到故障的影响。

|

| 图 10 C17电路结构的等价变换 Fig. 10 Equivalent transformation of C17 circuit structure |

| 图选项 |

基于等价变换的测试向量生成的流程见图 11。RTL级电路描述文件可以是. v、. blif、. bench、. aig等多种格式;经过逻辑综合、映射生成以LUT为基本逻辑单元的. blif格式的LUT网表;将LUT网表进行分割,生成与LUT网表中LUT数量相同的. blif格式的子网表,每个子网表中仅包含一个LUT,分割过程中子网表保留LUT在原网表中的输入和输出端名称;分别对每个子网表进行等价变换,生成由与门和非门组成的. aig格式的子网表;网表综合过程对每个. aig格式的子网表进行逻辑综合、优化生成最简的. bench格式的子网表,然后将所有的子网表综合,重新生成完整的. bench格式的电路网表,此时电路的等价变换完成;按照LUT网表中LUT单元的输入端、输出端和连线位置,在等价变换生成的. bench网表中,确定相对应的基本逻辑门的输入端、输出端和连线,并分别设置固定型故障;按照ATPG工具可处理的格式记录设置故障,然后根据. bench电路网表文件和故障设置文件,生成测试向量文件。

|

| 图 11 测试向量生成流程 Fig. 11 Flowchart of test vector generation |

| 图选项 |

4 故障定位方法 细胞级故障定位方法基于可配置内部扫描结构,通过分析扫描数据,可将故障定位至具体的细胞。在故障定位流程中需要电子细胞的布局布线文件和基因文件,这2个文件在电子细胞阵列功能分化时生成。

其中布局布线文件记录着各个细胞的布局位置、输入输出端口位置以及从细胞输出端输出至所有相关细胞输入端的信号传输路径。基因文件记录着每个电子细胞中存储的基因信息,通过基因文件可以确定每个电子细胞的具体功能。故障定位的具体流程见图 12。

|

| 图 12 故障定位流程 Fig. 12 Flowchart of fault location |

| 图选项 |

故障定位流程整体上可分为模拟过程、扫描过程和定位过程3个部分。其中模拟过程是根据当前的测试向量和故障集,确定当前测试向量可检测的故障,即确定可能引发故障的故障集;扫描过程是根据布局布线文件和故障集,确定需要扫描的具体的行和列,即扫描范围,然后进行扫描测试,并移出测试数据;定位过程是根据测试数据、布局布线文件和基因文件,对扫描范围内的电子细胞逐一进行单细胞故障判断,并根据判断结果定位故障。在故障定位流程中,模拟过程可由专门的模拟工具实现,扫描和定位过程中关键的步骤是扫描范围确定和单细胞故障判断。

4.1 扫描范围确定 根据当前故障集,在布局布线文件中依次搜索确定各个故障传输的路径,传输路径起点细胞和终点细胞的全部端口都需要扫描,传输路径的中间细胞中,传输路径经过的端口需要扫描。如图 13所示,6个电子细胞Cell 1~Cell 6,假设经过故障检测确定当前可能存在2个故障,即Cell 4的输出端固定型故障和Cell 1~Cell 6输入端固定型故障。则需要扫描的端口如图 13中阴影部分所示,总的扫描范围需要包括所有的阴影部分,为X1~X3和Y1~Y4的3行4列共7条扫描链。

|

| 图 13 扫描范围 Fig. 13 Scan scope |

| 图选项 |

4.2 单细胞故障判断 电子细胞的功能包括由开关盒实现的信号传输功能和由LUT、触发器实现的逻辑功能。因此,在对电子细胞故障进行判断时,主要考虑电子细胞的输入端故障、输出端故障、开关盒故障和触发器输入端故障,见图 14。

|

| 图 14 电子细胞的故障 Fig. 14 Faults in electronic cell |

| 图选项 |

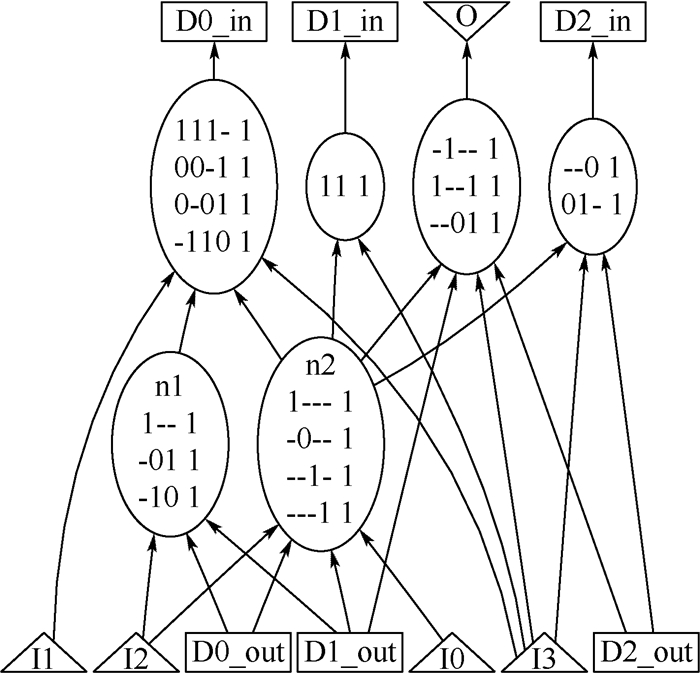

单细胞故障判断基于电子细胞的功能模拟,即根据电子细胞的功能、输入和寄存器状态模拟得到电子细胞正常输出和下一时刻寄存器状态。以开关盒宽度为2(每个方向有1个输入和1个输出)的电子细胞为例,记扫描得到的电子细胞4个输入端数据构成输入向量I =(I1, I2, I3, I4);4个输出端数据构成响应向量O =(O1, O2, O3, O4),由测试向量得到当前时刻细胞的触发器数据为D,由扫描输出数据得到触发器的真实响应数据记为Dr。记电子细胞的功能模拟函数为F,则经过功能模拟,电子细胞输出端的正常响应向量为O′=(O′1, O′2, O′3, O′4),记触发器的下一时刻的正常响应为D′,记电子细胞的基因信息为G,则电子细胞的功能模拟过程可由式(1)描述:

| (1) |

因此,当O = O′且D′=Dr时,说明电子细胞无故障;当O ≠ O′时,说明电子细胞存在输入端故障、输出端故障或开关盒故障;当D′≠Dr时,说明电子细胞存在触发器输入端故障。

5 仿真实验 仿真实验分为算法仿真和电路仿真2部分。其中算法仿真在Ubuntu 15.04环境下,基于ABC逻辑综合工具实现RTL级电路网表的等价变换;基于VTR[23]实现电子细胞阵列的布局布线和单细胞故障判断;基于Atalanta和fsim[24]实现测试向量的生成和模拟。电路仿真在Windows XP环境下,使用Xilinx ISE Design Suite 12.2集成开发环境,对测试结构的功能和测试过程进行仿真。

5.1 s27电路在电子细胞阵列中的实现

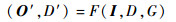

5.1.1 s27电路网表及布局布线结果 以s27电路为例,说明故障检测定位方法的具体流程。在VTR给出的标准文件库中,映射到4-LUT中的s27电路文件s27.blif含有5个输入端(包含1个时钟端)、1个输出端、3个触发器和6个LUT单元。因为s27电路为时序电路,需要转化为扫描形式,记s27电路的输入分别为I0、I1、I2和I3;输出为O;触发器为D0、D1和D2;D0_in、D1_in和D2_in为触发器的输入,D0_out、D1_out和D2_out为触发器的输出,s27电路的具体结构见图 15。

|

| 图 15 s27电路结构 Fig. 15 s27 circuit architecture |

| 图选项 |

采用4行4列的电子细胞阵列实现s27电路,电子细胞的开关盒宽度为2。阵列的布局布线结果如图 16所示。

|

| 图 16 s27电路的布局布线结果 Fig. 16 Placement and routing result of s27 circuit |

| 图选项 |

电子细胞N1、N2分别实现电路节点n1、n2的功能。触发器D0、D1、D2和分别与之相连接的电路节点经过打包,对应阵列中的电子细胞D0、D1、D2。电子细胞Out对应电路节点O。H0~H4为水平方向的5个扫描链,V0~V4为垂直方向的5个扫描链。

5.1.2 电子细胞结构及基因编码 如图 17所示,电子细胞中,地址模块由x和y方向的2个3位全加器构成。基因模块由SRAM存储器构成。功能模块由4输入LUT和扫描触发器构成。开关盒由4个4选1多路选择器构成。S1、E1、N1、W1分别为4个方向的输入端口,S0、E0、N0、W0为4个方向的输出端口。

|

| 图 17 s27电路中的电子细胞 Fig. 17 Electronic cell in s27 circuit |

| 图选项 |

每个电子细胞包含整个电子细胞阵列的16条基因,每一条基因由37位的0/1编码数据构成,基因编码对应的细胞功能如表 1所示。

表 1 基因编码 Table 1 Gene code

| 基因功能 | 开关盒控制 | LUT输入选择 | 输出控制 | LUT功能 |

| 编码位置 | 36~25 | 24~17 | 16 | 15~0 |

表选项

基因编码的15~0位存储着细胞中LUT的功能;16位控制细胞中LUT与触发器的输出;24~17位控制LUT的4个输入端的输入信号选择;36~25位控制开关盒中4个多路选择器。

电子细胞阵列中全部16个电子细胞的基因构成一个基因库,基因库中每条基因采用16进制编码表示,具体的编码见表 2。

表 2 基因库 Table 2 Gene bank

| 细胞坐标 | 细胞基因 |

| (0, 0) | 1FBE000000 |

| (1, 0) | 1EBE000000 |

| (2, 0) | 18EE138888 |

| (3, 0) | 14FE000000 |

| (0, 1) | 0F9E000000 |

| (1, 1) | 18DEC6EFCC |

| (2, 1) | 1B1DC2FFFB |

| (3, 1) | 0F761ABEBE |

| (0, 2) | 1F9A000000 |

| (1, 2) | 1F5C394F4F |

| (2, 2) | 07BC9D95C0 |

| (3, 2) | 07FA000000 |

| (0, 3) | 1FF2000000 |

| (1, 3) | 07FE000000 |

| (2, 3) | 1FF2000000 |

| (3, 3) | 0FFE000000 |

表选项

5.2 故障检测与定位

5.2.1 故障集和测试向量集 将每一个LUT称为一个电路节点,假设电路节点的输出端为“Op”,则“Op /1”和“Op /0”分别表示输出端Op的固定0型故障和固定1型故障;因为每个电路节点仅有一个输出端,因此可以用输出端指代电路节点。假设电路节点Op的一个输入端为Ip,则“Ip->Op /0”和“Ip->Op /1”分别表示输入端Ip的固定0型故障和固定1型故障。因此,在s27电路的输入输出端口和电路节点的输入输出端口处分别设置固定0型和固定1型故障,共54个故障,具体为:I0/0,I1/0,I2/0,I3/0,O/0,N1/0,N2/0,I0/1,I1/1,I2/1,I3/1,O/1,N1/1,N2/1,I1->D0_in/0,I1->D0_in/1,N1->D0_in/0,N1->D0_in/1,N2->D0_in/0,N2->D0_in/1,I3->D0_in/0,I3->D0_in/1,N2->D1_in/0,N2->D1_in/1,I3->D1_in/0,I3->D1_in/1,N2->O/0,N2->O/1,D1_out->O/0,D1_out->O/1,I3->O/0,I3->O/1,D2_out->O/0,D2_out->O/1,N2->D2_in/0,N2->D2_in/1,I3->D2_in/0,I3->D2_in/1,D2_out->D2_in/0,D2_out->D2_in/1,I2->N1/0,I2->N1/1,D0_out->N1/0,D0_out->N1/1,D1_out->N1/0,D1_out->N1 1,I2->N2/0,I2->N2/1,D0_out->N2/0,D0_out->N2/1,D1_out->N2/0,D1_out->N2/1,I0->N2/0,I0->N2/1。

采用4.2节给出的方法,对s27电路进行等价变换,然后根据电路的故障集,生成最小测试向量集,并使用fsim故障仿真器确定每个测试向量能够检测的具体故障并存储,结果如表 3所示。得到的测试向量集的故障覆盖率为100%。

表 3 最小测试向量集 Table 3 Minimal test vector set

| 序号 | 测试向量 | 正常响应 | 可检测 故障数 | |

| (I0, I1, I2, I3, D0, D1, D2) | (D0, D1, D2, O) | |||

| 1 | (1, 0, 0, 1, 1, 0, 0) | (0, 1, 0, 1) | 16 | |

| 2 | (1, 1, 1, 0, 1, 1, 1) | (0, 0, 1, 1) | 8 | |

| 3 | (0, 0, 0, 0, 0, 0, 0) | (0, 0, 0, 1) | 9 | |

| 4 | (1, 0, 0, 1, 0, 1, 1) | (0, 1, 0, 1) | 3 | |

| 5 | (1, 0, 1, 1, 0, 0, 1) | (0, 1, 0, 1) | 4 | |

| 6 | (1, 0, 0, 1, 0, 0, 1) | (0, 0, 1, 0) | 12 | |

| 7 | (0, 0, 0, 0, 1, 0, 1) | (1, 0, 1, 0) | 2 |

表选项

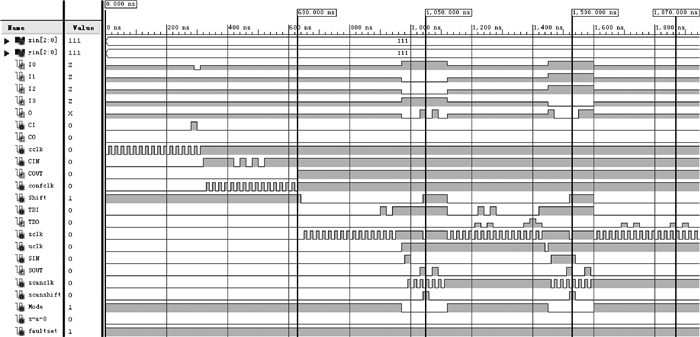

5.2.2 设定故障及故障的检测、定位过程 假设细胞Cell(1, 0)的开关盒发生E1端到N0端的固定0型故障。此故障反映在RTL级的故障为D1_out->O/0。对测试结构的故障检测和扫描测试过程进行仿真,结果如图 18、图 19所示。

|

| 图 18 故障检测 Fig. 18 Fault detection |

| 图选项 |

|

| 图 19 扫描测试 Fig. 19 Scan test |

| 图选项 |

图 18中xin[2 : 0]和yin[2 : 0]为地址输入,I0、I1、I2、I3、O是在电子细胞阵列中插入的与图 16中输入输出相对应的观测信号;CI为可配置边界扫描结构的配置输入信号,CO为可配置边界扫描结构的配置输出信号,cclk为配置时钟。Mode和Shift为可配置边界扫描单元中BC_1型扫描单元的控制信号。当Mode为1时,BC_1型扫描单元相当于直连线,当Mode为0时,BC_1型扫描单元输出更新寄存器中的数据;当Shift为1时,BC_1型扫描单元实现数据捕获功能,当Shift为0时,BC_1型扫描单元实现扫描数据移位功能。TDI为边界扫描单元的扫描数据输入,TDO为扫描数据输出,sclk为扫描时钟,uclk为更新时钟。CIN为电子细胞中扫描触发器的配置输入信号,COUT为扫描触发器的配置输出信号,confclk为扫描触发器的配置时钟。SIN为扫描触发器的扫描数据输入,SOUT为扫描数据输出,scanclk为扫描时钟,scanshift为扫描触发器的移位控制信号,当scanshift为0时,扫描触发器实现扫描功能,否则,扫描触发器实现捕获(正常工作)功能。s-a-0为插入的固定0型故障。faultset为故障设置信号,当faultset为1时表示插入故障。

系统时钟设为20 ns。0~310 ns完成边界扫描单元配置,当配置数据为0时,边界扫描单元为输入端口,否则为输出端口。将未使用的边界扫描单元全部默认设置为输入端口。根据图 16的布局布线结果,配置数据按照输入顺序依次为“0000000000000010”。320~630 ns完成可配置内部扫描链的配置,当扫描触发器中的配置数据为0时,扫描触发器处于扫描状态,否则,扫描触发器处于快速通过状态。因此,扫描触发器的配置数据按照输入顺序依次为“1111101010111111”。按照表 3的测试向量集,640~950 ns施加第1个测试向量“1001100”,I0~I3为“1001”,D0~D2为“100”,因此首先由TDI端口输入“0000000000 000101”,950~970 ns完成边界扫描测试数据更新,980~1 030 ns由SI N端口移入数据“100”,1 030~1 050 ns完成测试数据捕获,1 050~1 110 ns由SOUT端口移出数据“010”。1 120~1 530 ns施加第2个测试向量“1110111”。1 390 ns由TDO端口读回上一个测试向量在输出端口O的响应数据,为“1”,因此第1个测试向量的实际响应为“0101”,由表 3可知为正常响应。按照这种方法依次施加测试向量,并读回响应数据,1 530~1 590 ns由SOUT端读回数据“001”,1 870 ns时由TDO端读回数据“0”,则第二个向量的实际响应数据为“0010”,与正常响应数据“0011”不同,此时检测到故障。

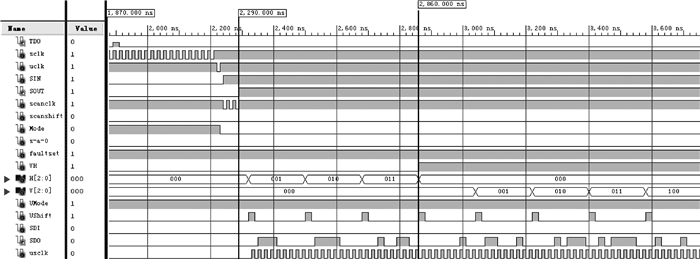

由故障模拟可知,此时测试向量“1110111”可检测“D1_out->O/0”、“I1->D0_in/0”、“I1/0”、“D2_out->D2_in /0”、“I3->D2_in /1”、“I3->D1_in/1”、“I3->D0_in/1”和“I3 /1”等8个故障。根据这些故障在阵列中的信号传输路径,确定扫描范围为H1~H3和V0~V4。依次进行扫描,扫描结果见图 19。仿真中假设测试数据为串行输出,VH为水平和垂直方向输出控制信号,当VH为0时,选择移出水平方向信号,当VH为1时,选择移出垂直方向信号。H[2 : 0]和V[2 : 0]分别为水平和垂直方向的多路选择器控制信号。UMode和UShift为扫描单元控制信号,当UMode为1,UShift为1时,扫描单元实现数据捕获功能,当UMode为1,UShift为0时,扫描单元实现数据移位功能。SDI为测试数据输入,SDO为测试数据输出,usclk为扫描时钟。1 900~2 290 ns重新加载测试向量“1110111”。2 320~2 330 ns捕获测试数据。2 330~3 750 ns由SDO端口依次移出扫描链H1~H3和V0~V4中的测试数据,按照移出顺序记录测试数据,得到测试数据如表 4所示。

表 4 测试数据 Table 4 Test data

| 扫描范围 | 数据 |

| H1 | 01110000 |

| H2 | 01111000 |

| H3 | 00100110 |

| V0 | 00000010 |

| V1 | 01100010 |

| V2 | 00010111 |

| V3 | 01011110 |

| V4 | 01000100 |

表选项

由测试数据、当前测试向量和已知的真实响应数据,根据电子细胞的具体功能进行单故障判断。单细胞故障判断可由C语言编程实现,主要过程的伪代码如下:

for(id=0;id < cellnum; id++)

{

??gene=Gene[id];

??cellsim(indata, outdata, d, dr, gene)

??{

????dn=Dsim(indata, gene);

????for(i=0;i < 4;i++)

????{o[i]=Osim(indata, d, i, gene); }

????if((dn= =dr) & & (o= =outdata))

??????cellfault=0;

????else

??????cellfault=1;

??}

}

其中: id为电子细胞的编号;cellnum为电子细胞的个数;gene为电子细胞的基因编码;cellsim为细胞功能模拟函数,根据在测试数据中获得的输入端数据indata,输出端数据outdata,当前的触发器状态d,触发器真实响应dr和电子细胞的基因实现故障判断功能;Dsim为触发器响应模拟函数,当电子细胞执行时序功能时,Dsim根据当前的输入端数据indata和细胞基因编码gene,返回下一时刻触发器正常情况下的状态dn;Osim为输出响应模拟函数,因为电子细胞的开关盒宽度为2,所以电子细胞共有4个输出端,针对每个输出端采用Osim进行模拟,得到正常情况下的输出端响应数据o。比较触发器和输出端的模拟响应与真实响应,如果相同,则电子细胞无故障,否则电子细胞出现故障。在故障判断的过程中,空格表示未扫描的数据,进行故障判断时,未扫描的数据均认为是正常数据。经过故障判断得到的电子细胞的故障情况如表 5所示,坐标为(1, 0)的细胞被判断为故障,成功完成故障定位。

表 5 故障判断结果 Table 5 Fault diagnosis results

| 坐标 | 实际 输入 | 实际 输出 | 正常 响应 | d | dn | dr | 判断 结果 |

| (0, 0) | (1, 0, 0, ) | (0, 0, 1, ) | (0, 0, 1, 0) | 正常 | |||

| (1, 0) | (1, 0, 1, ) | (0, 0, 1, ) | (0, 1, 1, 0) | 故障 | |||

| (2, 0) | (1, 1, 0, ) | (1, 0, 1, ) | (1, 0, 1, 0) | 1 | 0 | 0 | 正常 |

| (3, 0) | (1, 0, 0, ) | (0, 1, 0, ) | (0, 1, 0, 0) | 正常 | |||

| (0, 1) | (0, 0, 0, 0) | (0, 0, 0, 0) | (0, 0, 0, 0) | 正常 | |||

| (1, 1) | (0, 1, 1, 0) | (0, 0, 0, 0) | (0, 0, 0, 0) | 正常 | |||

| (2, 1) | (0, 1, 1, 1) | (1, 1, 1, 1) | (1, 1, 1, 1) | 正常 | |||

| (3, 1) | (1, 0, 1, 1) | (1, 1, 0, 0) | (1, 1, 0, 0) | 正常 | |||

| (0, 2) | (0, 1, 0, 0) | (0, 0, 1, 0) | (0, 0, 1, 0) | 正常 | |||

| (1, 2) | (1, 0, 1, 0) | (0, 1, 0, 1) | (0, 1, 0, 1) | 1 | 1 | 1 | 正常 |

| (2, 2) | (0, 1, 1, 1) | (1, 0, 0, 1) | (1, 0, 0, 1) | 1 | 0 | 0 | 正常 |

| (3, 2) | (0, 0, 0, 1) | (1, 0, 0, 1) | (1, 0, 0, 1) | 正常 | |||

| (0, 3) | (0, ,1, 0) | (0, ,0, 1) | (0, 0, 0, 1) | 正常 | |||

| (1, 3) | (0, ,0, 1) | (1, ,0, 0) | (1, 0, 0, 0) | 正常 | |||

| (2, 3) | (0, ,1, 0) | (0, ,0, 1) | (0, 0, 0, 1) | 正常 | |||

| (3, 3) | (0, ,1, 0) | (1, ,0, 0) | (1, 0, 0, 0) | 正常 |

表选项

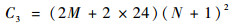

5.3 测试结构硬件消耗分析 如果电子细胞阵列由N行N列电子细胞构成,则称电子细胞阵列规模为N。如果电子细胞中开关盒在每个方向都有W个输入和W个输出,则称开关盒的宽度为2W。

以构成电路的MOS管数量来估算测试结构和胚胎电子细胞阵列所消耗的硬件资源。构成电路基本逻辑单元的MOS管数量如表 6所示。

表 6 基本逻辑单元的硬件消耗 Table 6 Hardware cost of basic logic units

| 基本逻辑单元 | 晶体管数量 |

| D触发器[25] | 24 |

| SRAM单元[25] | 6 |

| 2选1多路选择器[26] | 8 |

| 三态缓冲器[27] | 7 |

| 全加器[28] | 28 |

表选项

图 17所示的经典电子细胞结构主要由地址模块、开关盒、功能模块和基因模块组成。在计算硬件消耗时,任意输入的多路选择器均由2选1多路选择器级联实现,为了更加清楚直观,记2选1多路选择器的硬件消耗为M。

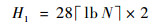

地址模块可由并行加法器实现。当数据输入位数为?lb N?时,由?lb N?个全加器级联构成并行加法器。由表 6可见,一个全加器由28个晶体管构成,因此记地址模块的硬件消耗为H1,因为地址模块中包含x和y2个方向,因此

| (2) |

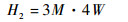

电子细胞的开关盒由4个方向的多路选择器构成,当电子细胞的开关盒宽度为2W时,假设开关盒为Wilton连接,则开关盒由4W个4选1多路选择器构成,每个4选1多路选择器由3个2选1多路选择器构成,开关盒的硬件消耗为

| (3) |

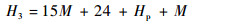

在计算功能模块的硬件消耗时,构成LUT的SRAM单元计算在基因存储模块的硬件消耗内。因此功能模块中包括1个16选1多路选择器(由15个2选1多路选择器级联构成)、1个触发器、4个实现LUT输入选择的多路选择器和1个实现触发器输出和LUT输出选择的2选1多路选择器。假设LUT可以接收来自4个方向的所有的4W个输入信号,则4个实现LUT输入选择的多路选择器的硬件消耗记为

| (4) |

因此功能模块的整体硬件消耗记为

| (5) |

每条基因编码存储着8W位开关盒的控制信息,4?lb(4W)?位LUT的输入控制信息,1位LUT和触发器输出控制信息,16位LUT的功能信息,记基因的编码长度为L。

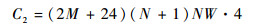

基因模块由SRAM存储器构成,1个SRAM单元存储1位基因编码,基因模块存储的基因个数为N2,则基因模块的硬件消耗为

| (6) |

因此,记整个电子细胞的硬件消耗为

| (7) |

整个阵列的硬件消耗记为

| (8) |

每一个可配置边界扫描单元中包含6个2选1多路选择器、5个触发器和1个三态缓冲门。可配置边界扫描结构包含4N个可配置边界扫描单元,记可配置边界扫描结构的硬件消耗为

| (9) |

每一个内部扫描单元包含2个2选1多路选择器和1个触发器,因此所有的扫描单元的硬件消耗记为

| (10) |

每一个可配置内部扫描开关盒包含2个2选1多路选择器和2个实现控制功能的触发器。测试结构中共含有(N+1)2个可配置扫描开关,所有的可配置扫描开关的硬件消耗记为

| (11) |

阵列中有N2个扫描触发器。每个扫描触发器由3个2选1多路选择器和2个触发器构成,与正常的电子细胞相比,扫描触发器中增加了2个2选1多路选择器和1个触发器。将增加部分的硬件消耗记为

| (12) |

所有测试结构的硬件消耗记为

| (13) |

由表 6和式(2)~式(13),可以计算电子细胞阵列和测试结构的硬件消耗,其中M的值为8。当电子细胞阵列的规模N在5~40范围内,开关盒宽度2W在2~32范围内变化时,电子细胞阵列和测试结构的硬件消耗如图 20所示。

|

| 图 20 硬件消耗比较 Fig. 20 Hardware cost comparison |

| 图选项 |

如图 20所示,当电子细胞阵列规模为5,开关盒宽度为2时,构成电子细胞阵列的晶体管数量约为105,构成测试结构的晶体管数量约为104;当电子细胞阵列规模为40,开关盒宽度为32时,构成电子细胞阵列的晶体管数量约为109,构成测试结构的晶体管数量在106~107之间。说明随着电子细胞阵列规模和开关盒宽度的增大,电子细胞阵列和测试结构的硬件消耗都增加了,而且电子细胞阵列的硬件消耗增长速度远远高于测试结构。

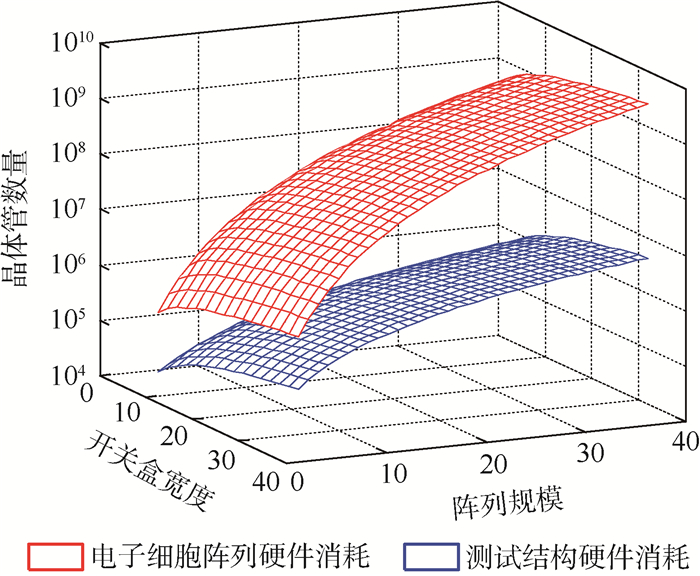

如图 21所示,当阵列规模为5,开关盒宽度为2时,测试结构的硬件消耗所占的比例为0.078 3,开关盒宽度为32时,测试结构的硬件消耗所占的比例为0.102 7;当阵列规模为40,开关盒宽度为2时,测试结构的硬件消耗所占的比例为0.000 9,开关盒宽度为32时,测试结构的硬件消耗所占的比例为0.001 7。因此,阵列规模越大,开关盒宽度越小,测试结构的硬件消耗所占的比例越小,而且阵列规模越大,开关盒宽度对测试结构硬件消耗所占的比例影响越小。

|

| 图 21 测试结构硬件消耗所占比例 Fig. 21 Proportion of testing architecture hardware cost |

| 图选项 |

总的来说,电子细胞阵列和测试结构的硬件消耗随着阵列规模和开关盒宽度的增大而增加;但是,随着阵列规模的增大,测试结构的硬件消耗所占的比例明显降低,这说明测试结构适用于大规模的电子细胞阵列。

本文的研究工作特点主要体现在以下3个方面:

1) 在测试结构设计方面,提出将测试资源从电子细胞中分离出来,构成一个整体的测试结构,统一处理,实现故障的整体检测和局部定位,电子细胞不再承担故障检测的任务。提出的测试结构具有统一的、明确的设计方法。

2) 在故障检测和定位方法方面,提出了RTL级故障检测和细胞级故障定位相结合、硬件测试结构和软件算法相结合的,更为系统的故障检测和定位方法,更充分的利用了测试结构与计算资源的优势。

3) 在硬件消耗方面,通过计算晶体管数量,对测试结构的硬件消耗进行了简单的估计,给出了定量的评估数据。

6 结论 1) 提出的测试结构可有效的实现配置、扫描等功能,为故障检测和故障定位提供了硬件基础;而且提出的测试结构和故障检测、定位方法与具体的电子细胞结构关系不大,受电子细胞和阵列结构限制较小,通用性较强。

2) 提出的故障检测和定位方法,可在RTL级对整个电子细胞阵列的故障进行检测,并将故障定位至具体的电子细胞,而且可以有效地检测时序电路中出现的故障,故障检测和定位能力较强。

3) 随着电子细胞阵列规模的增大,测试结构的硬件消耗在整个阵列中所占的比例明显下降,说明测试结构适用于大规模的电子细胞阵列,硬件消耗较低。

另外,本文提出的方法对于演化硬件(evolvable hardware)领域的研究也有一定的意义。从故障自修复的角度来看,演化硬件实现自修复主要依靠重构,但是,由于缺少演化专用的可重构硬件,在演化重构的过程中往往仅对故障进行检测,很难对故障进行定位,导致演化速度慢。因此,如果在专用的可重构硬件结构设计中加入测试结构,就可以实现故障的准确定位,加快演化的速度。

在未来的工作中,还需要对更复杂的故障情况进行深入研究,特别是瞬态故障和单粒子效应等,这些故障已成为电子系统在强辐射环境下面临的主要威胁,因此,针对瞬态故障和单粒子效应的特点,设计更完善的在线故障检测结构,对于进一步提高电子系统的可靠性具有重要意义。

参考文献

| [1] | MANGE D, SANCHEZ E, STAUFFER A, et al. Embryonics:A new methodology for designing field-programmable gate arrays with self-repair and self-replicating[J].IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 1998, 6(3): 387–399.DOI:10.1109/92.711310 |

| [2] | ORTEGA-SANCHEZ C, MANGE D, SMITH S, et al. Embryonics:A bio-inspired celluar architecture with fault-tolerant properties[J].Genetic Programming and Evolvable Machines, 2000, 1(3): 187–215.DOI:10.1023/A:1010080629099 |

| [3] | 张砦, 王友仁. 基于可靠性优化的芯片自愈型硬件细胞阵列布局方法[J].航空学报, 2014, 35(12): 3392–3402. ZHANG Z, WANG Y R. Method to reliability improving of chip self-healing hardware by array layout reformation[J].Acta Aeronautica et Astronautica Sinica, 2014, 35(12): 3392–3402.(in Chinese) |

| [4] | 张砦, 王友仁. 应用设计过程的胚胎硬件细胞单元粒度优化方法[J].航空学报, 2016, 37(11): 3502–3511. ZHANG Z, WANG Y R. Cell granularity optimization method of embryonics hardware in application design process[J].Acta Aeronautica et Astronautica Sinica, 2016, 37(11): 3502–3511.(in Chinese) |

| [5] | 朱赛, 蔡金燕, 孟亚峰, 等. 具有故障细胞的胚胎电子阵列上目标电路评估[J].兵工学报, 2016, 37(11): 2120–2127. ZHU S, CAI J Y, MENG Y F, et al. Evaluation of target circuit realized on embryonics array with faulty cells[J].Acta Armamentarii, 2016, 37(11): 2120–2127.DOI:10.3969/j.issn.1000-1093.2016.11.021(in Chinese) |

| [6] | 王涛, 蔡金燕, 孟亚峰, 等. 胚胎电子细胞阵列中空闲细胞的配置[J].航空学报, 2017, 38(4): 320266. WANG T, CAI J Y, MENG Y F, et al. Configuration of idle cells in embryonics electronic cell array[J].Acta Aeronautica et Astronautica Sinica, 2017, 38(4): 320266.(in Chinese) |

| [7] | 李岳, 王南天, 钱彦岭. 原核细胞仿生自修复电路设计[J].国防科技大学学报, 2012, 34(3): 154–157. LI Y, WANG N T, QIAN Y L. Self-healing circuit design inspired by prokaryotic cell[J].Journal of National University of Defense Technology, 2012, 34(3): 154–157.(in Chinese) |

| [8] | 徐佳庆, 窦勇, 吕启, 等. 电子组织:一种具有自适应能力的可重构仿生硬件结构[J].计算机研究与发展, 2012, 49(9): 2005–2017. XU J Q, DOU Y, LV Q, et al. eTissue:An adaptive reconfigurable bio-inspired hardware architecture[J].Journal of Computer Research and Development, 2012, 49(9): 2005–2017.(in Chinese) |

| [9] | 王敏, 王友仁, 张砦, 等. 三维结构可重构阵列在线自诊断与容错方法[J].仪器仪表学报, 2013, 34(3): 650–656. WANG M, WANG Y R, ZHANG Z, et al. Online self-fault diagnosis and fault tolerant method for three-dimensional reconfigurable array[J].Chinese Journal of Scientific Instrument, 2013, 34(3): 650–656.(in Chinese) |

| [10] | 蔡金燕, 朱赛, 孟亚峰. 一种新型的仿生电子细胞基因存储结构[J].电子学报, 2016, 44(8): 1915–1923. CAI J Y, ZHU S, MENG Y F. A novel gene memory structure for bio-inspired electronic cell[J].Acta Electronica Sinica, 2016, 44(8): 1915–1923.(in Chinese) |

| [11] | 李丹阳, 蔡金燕, 孟亚峰, 等. 基因循环存储模块的SEU自检[J].半导体技术, 2016, 41(4): 312–318. LI D Y, CAI J Y, MENG Y F, et al. SEU self-checking of gene cyclic memory module[J].Semiconductor Technology, 2016, 41(4): 312–318.(in Chinese) |

| [12] | 朱赛, 蔡金燕, 孟亚峰. 一种LUT型胚胎电子阵列的功能分化方法[J].电子学报, 2015, 43(12): 2440–2448. ZHU S, CAI J Y, MENG Y F. A functional differentiation method for LUT-based embryonics array[J].Acta Electronica Sinica, 2015, 43(12): 2440–2448.DOI:10.3969/j.issn.0372-2112.2015.12.014(in Chinese) |

| [13] | 郝国锋, 王友仁, 张砦, 等. 可重构硬件芯片级故障定位与自主修复方法[J].电子学报, 2012, 40(2): 384–388. HAO G F, WANG Y R, ZHANG Z, et al. In-chip fault localization and self-repairing method for reconfigurable hardware[J].Acta Electronica Sinica, 2012, 40(2): 384–388.(in Chinese) |

| [14] | ZHANG X, DRAGFFY G, PIPE A G, et al. Artificial innate immune system:An instant defence layer of embryonics[J].Lecture Notes in Computer Science, 2004, 3239(1): 302–315. |

| [15] | BOLCHINI C, SALICE F, SCIUTO D.Designing self-checking FPGAs through error detection codes[C]//Proceedings 17th IEEE International Symposium on Defect and Fault Tolerance in VLSI Systems.Piscataway, NJ:IEEE Press, 2002:60-68. |

| [16] | 李丹阳, 蔡金燕, 孟亚峰, 等. 基于双模冗余的胚胎电子阵列在线故障检测[J].北京航空航天大学学报, 2017, 43(6): 1112–1122. LI D Y, CAI J Y, MENG Y F, et al. An online fault detection method based on dual modular redundancy for embryonics array[J].Journal of Beijing University of Aeronautics and Astronautics, 2017, 43(6): 1112–1122.(in Chinese) |

| [17] | CANHAM R O, TYRRELL A M. A hardware artificial immune system and embryonic array for fault tolerant systems[J].Genetic Programming and Evolvable Machines, 2003, 4(4): 359–382.DOI:10.1023/A:1026143128448 |

| [18] | ABRAMOVICI M, EMMERT J M, STROUD C E.Roving STARs:An integrated approach to on-line testing, diagnosis, and fault tolerance for fpgas in adaptive computing systems[C]//Proceedings the 3rd NASA/DoD workshop on Evolvable Hardware.Piscataway, NJ:IEEE Press, 2001:73-92. |

| [19] | SAMIE M, DRAGFFY G, TYRRELL A M. Novel bio-inspired approach for fault-tolerant VLSI systems[J].IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2013, 21(10): 1878–1891.DOI:10.1109/TVLSI.2012.2220793 |

| [20] | BREMNER P, LIU Y, SAMIE M, et al. SABRE:A bio-inspired fault-tolerant electronic architecture[J].Bioinspiration & Biomimetics, 2013, 8(1): 1–16. |

| [21] | KIM S, CHU H, YANG I, et al. A hierarchical self-repairing architecture for fast fault recovery of digital systems inspired from paralogous gene regulatory circuits[J].IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2012, 20(12): 2315–2328.DOI:10.1109/TVLSI.2011.2176544 |

| [22] | Test Technology Standards Committee.IEEE standard for test access port and boundary-scan architecture:IEEE 1149.1-2013[S].Piscataway, NJ:IEEE Press, 2013:155. |

| [23] | LUU J, GOEDERS J, WAINBERG M, et al.VTR7.0:Next generation architecture and cad system for FPGAS[J].ACM Transactions on Reconfigurable Technology and Systems, 2014, 7(2):6:1-6:30. |

| [24] | LEE H K, HA D S.An efficient, forward fault simulation algorithm based on the parallel pattern single fault propagation[C]//Proceedings international Test Conference.Piscataway, NJ:IEEE Press, 1991, 25(11):946-955. |

| [25] | 朱赛, 蔡金燕, 孟亚峰, 等. 胚胎电子细胞中基因备份数目优选方法[J].北京航空航天大学学报, 2016, 42(2): 328–336. ZHU S, CAI J Y, MENG Y F, et al. Gene backup number selection method for embryonics cell[J].Journal of Beijing University of Aeronautics and Astronautics, 2016, 42(2): 328–336.(in Chinese) |

| [26] | 杨之廉, 许军. 集成电路导论[M].北京: 清华大学出版社, 2012: 103. YANG Z L, XU J. Integrate circuit introduction[M].Beijing: Tsinghua University Press, 2012: 103.(in Chinese) |

| [27] | 彭科, 杨海钢. 一种用于数字集成系统的新型CMOS三态缓冲器的设计[J].电子器件, 2007, 30(6): 2080–2087. PENG K, YANG H G. Design of a novel CMOS three-state buffer for digital integrated systems[J].Chinese Journal of Electron Devices, 2007, 30(6): 2080–2087.(in Chinese) |

| [28] | 叶以正, 来逢昌. 集成电路设计[M].北京: 清华大学出版社, 2011: 219. YE Y Z, LAI F C. Integrate circuit design[M].Beijing: Tsinghua University Press, 2011: 219.(in Chinese) |