全文HTML

--> --> -->提升锂离子电池能量密度的根本途径之一是开发高容量的电极材料. 其中, 硅材料由于具有极高的理论比容量(3579 mAh/g), 已经成为最具有前景的负极材料之一, 并被广泛研究[2-6]. 但是, 硅电极在脱/嵌锂的过程中会发生大的体积变形(约300%), 进而在材料内部引起较大的应力, 最终会导致电极颗粒的断裂、固态电解质界面膜(solid electrolyte interface)不稳定生长、活性材料与导电剂或集流体界面接触损失[7-9]. 这些不利的力学衰减行为致使硅电极容量损失和较差的循环性能. 近年来, 众多****利用原位或非原位的实验方法对硅电极(包括纳米尺寸和微米尺寸)充放电过程中的变形、断裂行为进行了深入的研究[9-18]. 另外, 为了解释硅电极的变形和断裂行为以及指导硅电极的结构设计, 国内外****建立和发展了一系列力-化耦合模型[19-24]和数值模拟方法[16,19,25-28]. 综合现有研究结果[10,11], 以(111)单晶硅为例阐述在嵌锂过程中硅电极的变形、断裂过程, 如图1所示. 由于锂嵌入过程依赖于晶体取向, 硅电极沿着

图 1 在锂化过程中(111)单晶硅电极的衰减机制

图 1 在锂化过程中(111)单晶硅电极的衰减机制Figure1. Degradation mechanism of (111) single-crystalline silicon electrodes during lithiation.

另外, 电池的弱点之一是高倍率充放电下电池容量的快速衰减[29], 也正因为此, 倍率性能是评价电池性能的重要指标. 由于硅电极的应力水平、分布与锂离子的扩散及其引起的内部浓度梯度息息相关, 因此研究不同电流密度(或倍率)下硅电极的应力水平和断裂行为是非常重要的[30,31]. Soni等[31]利用原位多光束光学应力传感系统调查了倍率从C/20到5C变化过程中无定形硅薄膜电极内部应力分布, 发现硅薄膜中锂离子较慢的扩散引起了应力梯度, 且高的倍率会引起大的局部应力和薄膜裂纹的产生. 除此之外, 常力蠕变测试[32]和纳米压痕蠕变测试[33]等实验已经证明了锂化硅的率相关性. 基于锂化硅塑性的率相关性, Jia和Liu[34]建立了能够捕捉两相锂化的纳米硅电极黏塑性力学模型, 并发现锂化诱导应力依赖于相界面移动速度和硅电极特征尺寸. 对于微米尺寸硅电极来说, 研究倍率对硅电极断裂行为的影响有助于进一步理解硅电极的断裂行为, 并选择合适的充放电倍率.

本文针对微米尺寸的(111)单晶硅柱电极, 利用光学显微镜观测嵌锂过程中硅电极表面形貌演化. 通过光学显微镜的观测确定裂纹形成时刻, 并计算对应时刻的硅电极嵌锂深度. 为了进一步认识硅电极起裂行为, 研究了不同电流密度下硅电极的断裂全过程. 发现尽管电流密度不同, 但起裂时硅电极相对嵌锂深度差异不大. 所建立的有限元模型可以对实验现象进行很好的解释, 并结合理论模型分析了起裂时锂化硅层的应力状态. 这些结果有助于理解硅电极的电化学嵌入过程与变形、断裂的关系, 并为微米硅电极的合理设计提供指导. 这里需要说明的是, 我们前期所做的工作主要关注点是在锂化过程中硅电极形貌的演化, 以及硅电极破坏的整个过程(如膨胀变形、裂纹起裂及扩展、锂化硅剥离等), 并根据断裂机制提出几何设计方法以缓解各向异性变形引起的力学衰减问题[10]. 本文主要关注点是建立锂化过程中硅柱起裂与嵌锂深度的关系, 并研究不同电流密度对形貌演化和起裂时嵌锂深度的影响.

2.1.电极制备

微米尺寸N型(111)单晶硅柱阵列的详细制备方法参见我们之前所做的工作[10]. 在本文中, 具有特定尺寸、间距和高度的硅柱阵列通过标准的光刻工艺并结合深反应离子刻蚀技术获得. 为了提高硅电极的电接触性能, 在硅电极的刻蚀背面通过磁控溅射的方法沉积15 nm的钛(Ti)层和100 nm的金(Au)层. 剪裁宽度约为2 mm的铜箔作为引线, 用环氧树脂胶粘在金镀层表面. 这里需要注意的是, 除了硅刻蚀面以及铜箔引线外的其他区域都需涂上环氧树脂胶, 以控制硅与电解液接触区域并防止金镀层在脱/嵌锂过程中的脱落.2

2.2.电化学测试

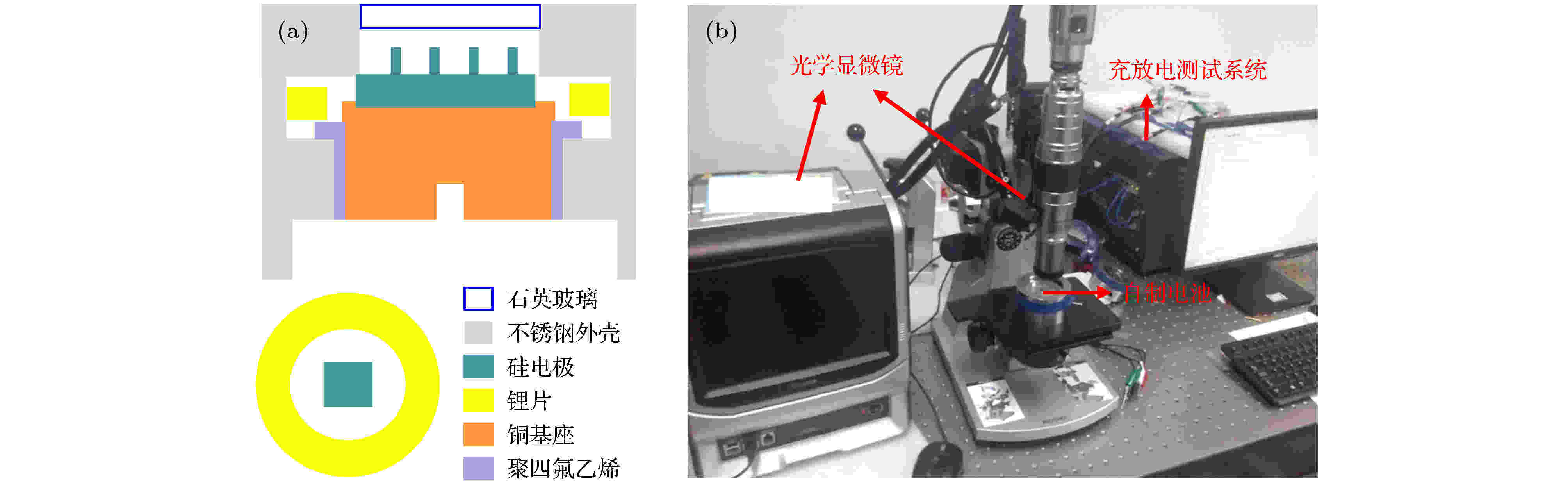

图2(a)为用来组装半电池的自制电池装置. 该装置由不锈钢外壳(与锂片直接接触)、铜柱(硅负极放置处)、聚四氟乙烯柱(绝缘作用)和石英玻璃窗口(光学观测)组成, 可与光学显微镜结合实时观测硅柱电极表面形貌变化(图2(b)). 电池组装在水、氧含量小于 1 ppm (1 ppm = 1 mg/L)的手套箱中进行. 电解液由溶质为1 mol/L的LiPF6, 溶剂为EC (ethylene carbonate)和DMC (dimethyl carbonate) (体积比为1∶1)的溶液配制而成. 所有的恒电流测试实验都在Arbin充放电测试系统上进行. 为了研究电流密度对硅电极初始断裂的影响, 恒流放电电流密度(对应硅嵌锂过程)分别设置为72.9, 193.3和465.3 μA/cm2. 图 2 (a) 自制电池装置示意图; (b) 光学观测平台

图 2 (a) 自制电池装置示意图; (b) 光学观测平台Figure2. (a) Schematic diagram of a home-made battery cell; (b) experimental platform for the optical observation.

2

2.3.形貌表征

硅柱阵列初始形貌通过场发射扫描电子显微镜(field-emission scanning electron microscope, FE-SEM)表征. 利用表征得到的硅柱高度和直径计算硅柱的表面积, 从而计算面电流密度. 这里, 在计算面电流密度时忽略了刻蚀硅柱的制造缺陷和表面波动. 另外, 通过聚焦离子束设备(focused ion beam machine, FIB)表征参与反应的硅基体的嵌锂深度.3.1.不同电流密度下硅电极形貌演化

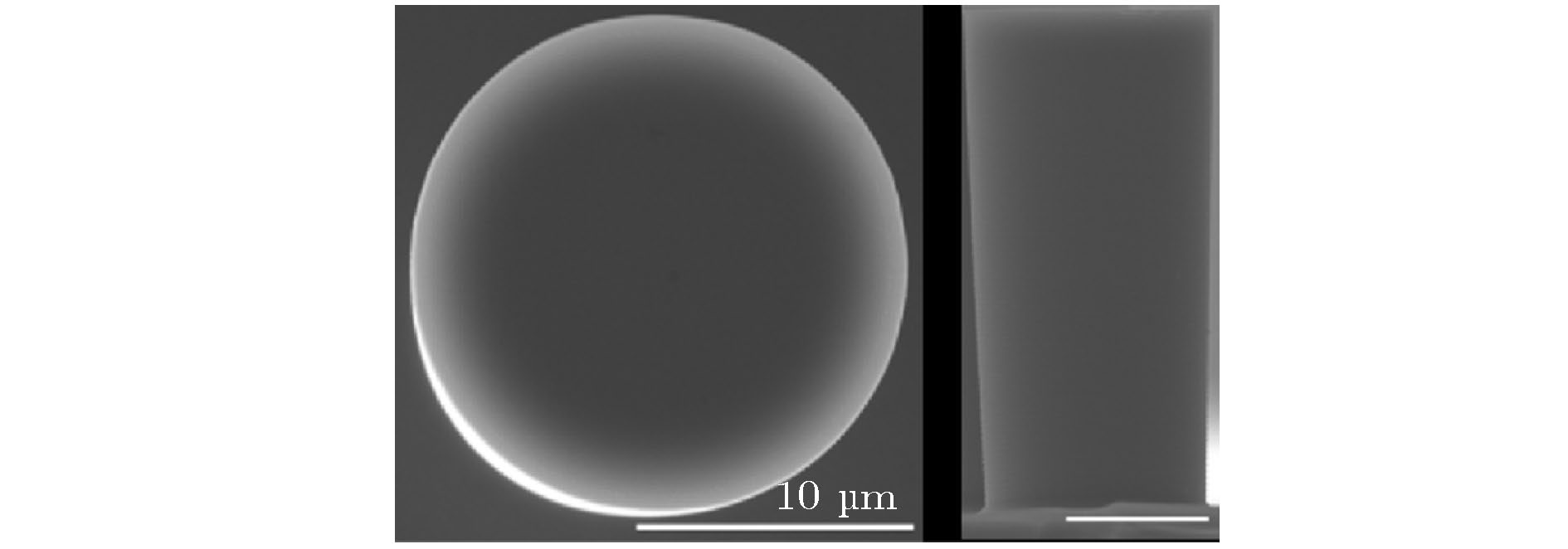

虽然硅电极在脱/嵌锂过程中的整个断裂过程已经被详细研究过, 但是在不同电流密度下硅电极断裂行为的一些关键细节还有待进一步研究[10]. 本文所讨论的硅电极典型尺寸和形貌如图3所示. 选择直径约20 μm硅柱的原因有以下两点: 1)较大尺寸的微米硅电极力-化耦合行为突出, 可以放大硅电极的力学衰减行为; 2)较大尺寸的微米电极有利于通过光学手段较清晰地观测硅柱的形貌演化. 图 3 硅柱典型形貌FE-SEM图, 标尺为10 μm

图 3 硅柱典型形貌FE-SEM图, 标尺为10 μmFigure3. Typical FE-SEM images of a micron-sized silicon pillar. Here, the scale bars are 10 μm.

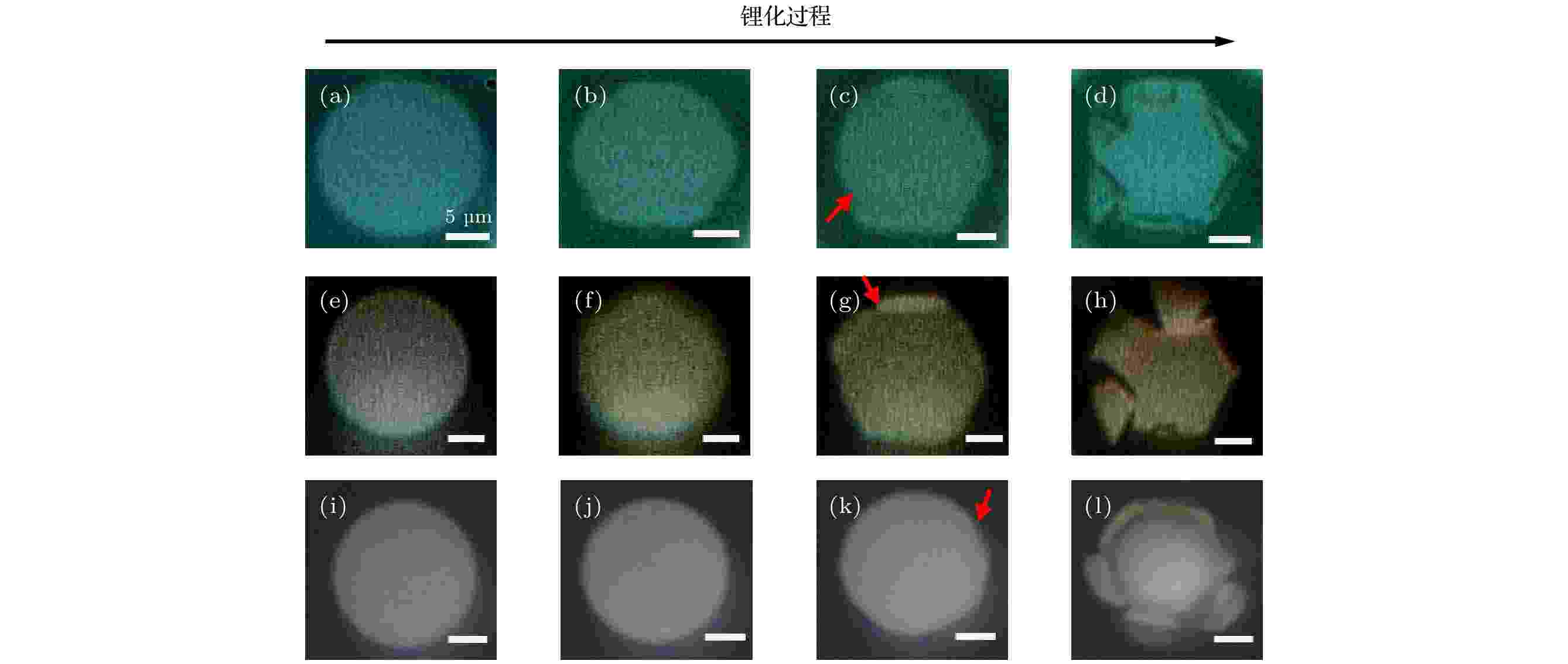

为了调查电流密度对硅电极断裂行为的影响, 以恒电流放电(嵌锂过程)的方式设定了三种电流密度(72.9, 193.3和465.3 μA/cm2). 在三种电流密度下硅电极的形貌演化如图4所示. 可以发现在不同的电流密度下硅电极的变形、起裂位置和锂化硅剥离形貌会有较大差异, 但均可分为以下三个过程: 1)膨胀变形阶段(如图4(b)、图4(f)和图4(j)); 2)裂纹形成阶段(如图4(c)、图4(g)和图4(k)); 3)裂纹扩展和锂化硅剥离阶段(如图4(d)、图4(h)和图4(l)). 对于膨胀变形阶段, 电流密度越大, 从膨胀变形阶段到裂纹形成阶段时间越短, 光学显微镜所得的膨胀变形形貌越不明显, 如电流密度为465.3 μA/cm2时此阶段变形不明显(如图4(j)所示). 对于裂纹形成阶段, 虽然起裂位置不同, 但都位于相邻{110}相交处附近, 与我们之前报道的结果一致[10]. 对于裂纹扩展和锂化硅剥离阶段, 电流密度越大, 由于硅柱位置等差异所引起的非均匀分布的锂离子浓度的影响越小, 电极断裂和剥离更接近于理想情况, 即呈现出六重对称性(如图1所示), 但裂纹扩展和剥离情况也越快且越严重.

图 4 在以(a)?(d) 72.9 μA/cm2[10]、(e)?(h) 193.3 μA/cm2和(i)?(l) 465.3 μA/cm2的电流密度嵌锂过程中硅电极截面的形貌演化, 标尺为5 μm

图 4 在以(a)?(d) 72.9 μA/cm2[10]、(e)?(h) 193.3 μA/cm2和(i)?(l) 465.3 μA/cm2的电流密度嵌锂过程中硅电极截面的形貌演化, 标尺为5 μmFigure4. Morphological changes during lithiation for silicon electrodes at (a)?(d) 72.9 μA/cm2[10], (e)?(h) 193.3 μA/cm2 and (i)?(l) 465.3 μA/cm2. Here, the scale bars are 5 μm.

2

3.2.裂纹形成阶段嵌锂深度

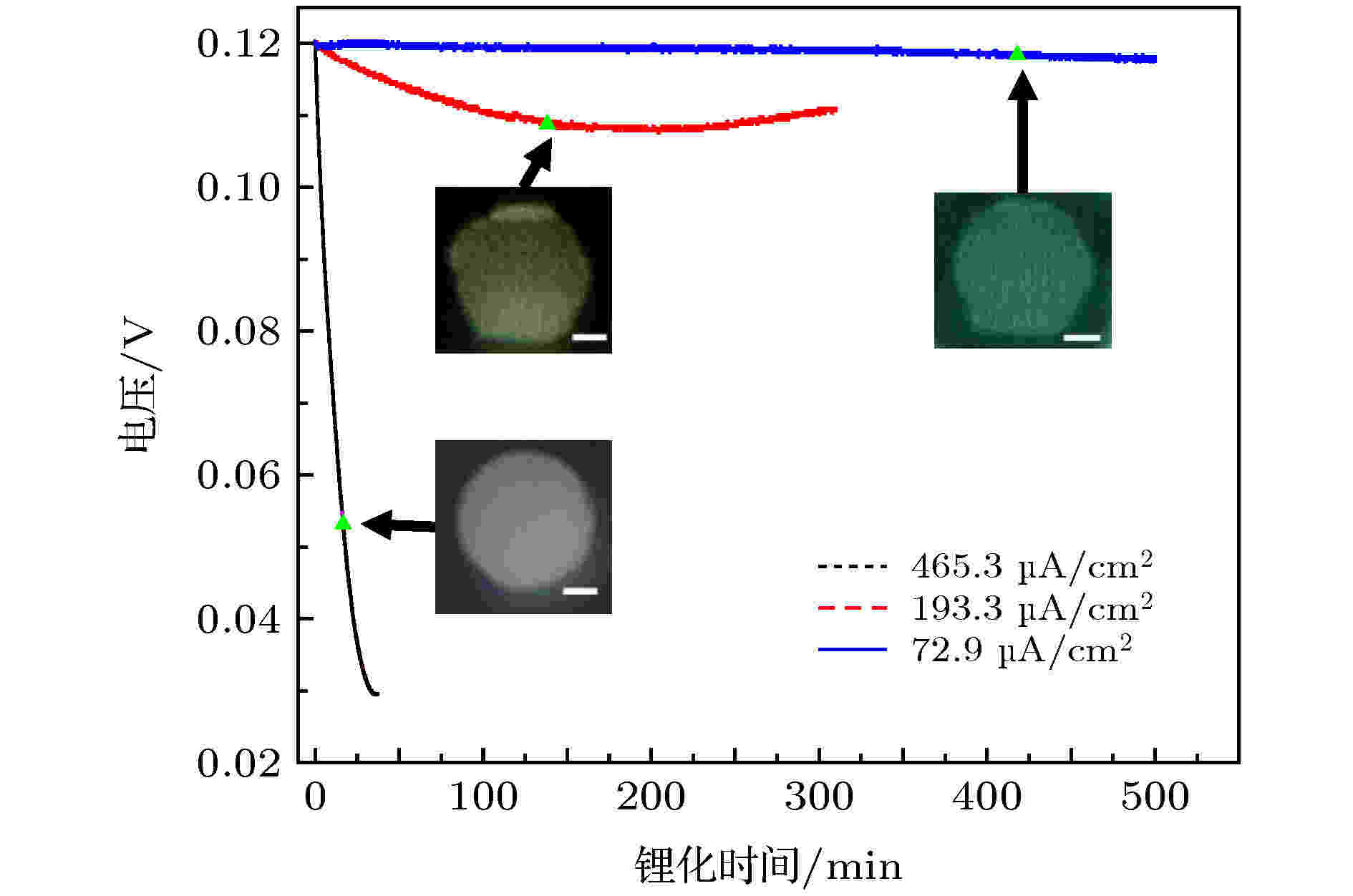

微米尺寸硅电极脱/嵌锂过程中由于过大的体积变形会在电极内部产生较大的应力, 最终导致裂纹形成、扩展和电极颗粒粉化. 本文重点关注不同电流密度对硅电极裂纹形成阶段的影响. 裂纹形成时对应的锂化时间和电压关系如图5所示. 需要说明的是, 在电压大于0.12 V时硅电极并没有发生嵌锂变形[10], 意味着绝大部分硅电极的嵌锂过程发生在0.12 V以下. 因此, 为了消除副反应等影响, 将锂化时间定义为T = Tt – TU = 0.12 V. 这里Tt是当前所关心时刻对应的总放电时间(嵌锂时间), TU = 0.12 V是电压U = 0.12 V时对应的放电时间. 从图5可看出, 电流密度越大, 起裂时间越早, 并且从起裂阶段(如图4(c)、图4(g)和图4(k))到破坏阶段(如图4(d)、图4(h)和图4(l))的间隔时间越短. 图 5 不同电流密度下硅电极裂纹形成时对应的锂化时间和电压, 标尺为5 μm

图 5 不同电流密度下硅电极裂纹形成时对应的锂化时间和电压, 标尺为5 μmFigure5. Profile of voltage and lithiation time for crack initiation of silicon electrodes at different current density. Here, the scale bars are 5 μm.

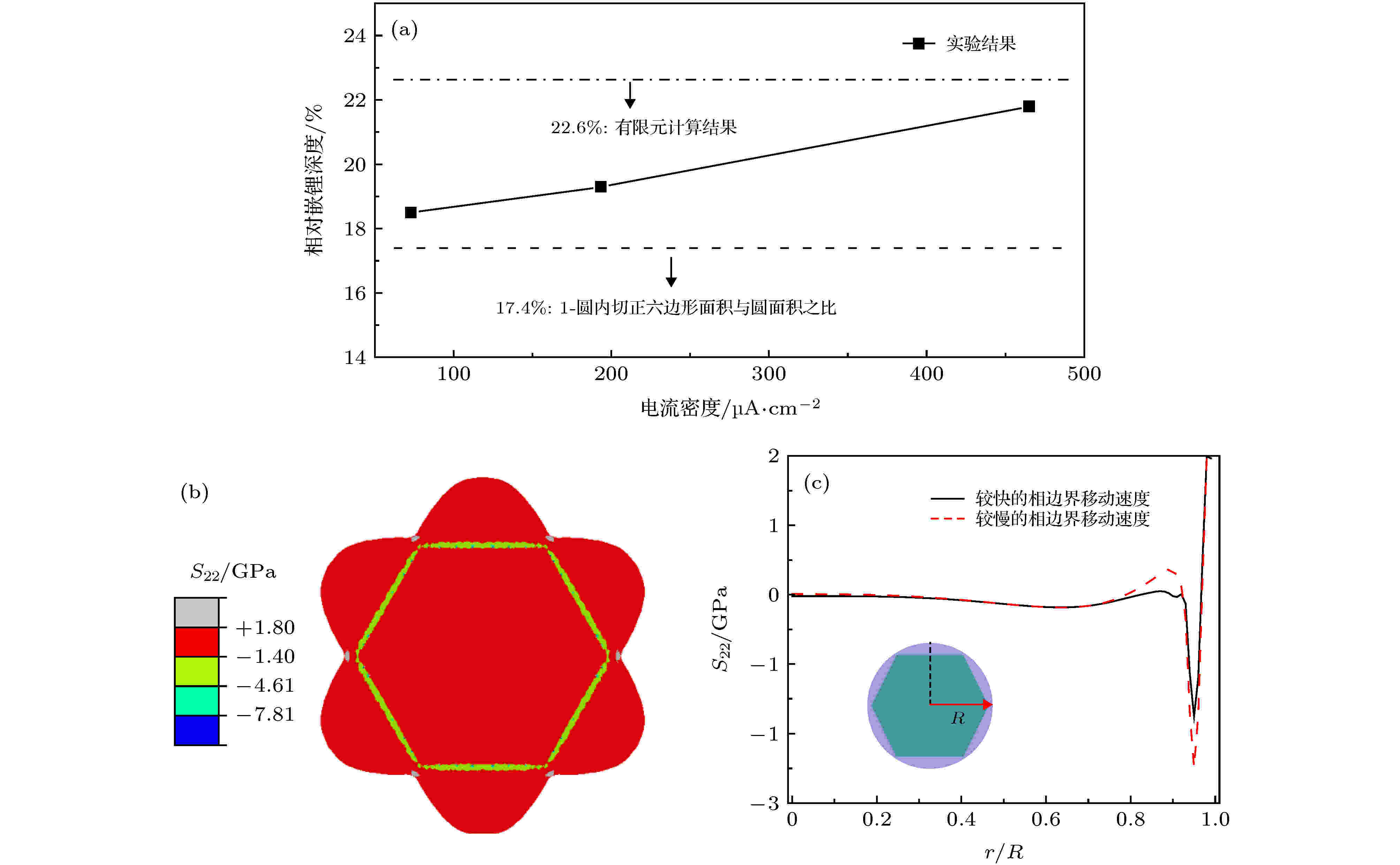

本文所设计的硅柱电极尺寸在20 μm左右, 在恒电流放电下硅柱几乎都会发生断裂现象, 且断裂位置位于两个{110}晶面相交处附近, 这主要是由于单晶硅电极各向异性体积变形, 导致在两个{110}晶面相交处产生局部的应力集中或者应变集中, 最终造成硅电极裂纹形成, 如图6(b)所示. 在前文中提到, 电流密度越大, 裂纹形成对应的锂化时间越短. 但目前对于嵌锂深度与裂纹形成的关系及不同电流密度对硅电极裂纹形成阶段的影响还有待进一步分析. 因此, 这里统计分析了不同电流密度下硅电极裂纹形成时的相对嵌锂深度, 如图6所示. 本文中将相对嵌锂深度定义为(Capacityt –CapacityU = 0.12 V)与Capacitytheory的比值. 这里Capacityt指裂纹形成时充放电测试系统记录的容量, CapacityU = 0.12 V是电压为0.12 V时对应的容量, Capacitytheory是硅柱的理论容量. 因为我们关心的是硅柱的嵌锂程度, 所以在计算相对嵌锂深度时需要排除硅基底的嵌锂影响(如图7所示). 从图6(a)可以看出, 在三种不同电流密度放电(嵌锂)过程中, 即使起裂时锂化时间和锂化硅剥离时间差异明显, 硅电极起裂时相对嵌锂深度差异也不大(相对锂化深度在18%—22%之间), 这个现象需要并值得进一步分析和讨论. 现有研究已经表明(111)单晶硅锂化过程与晶向相关, 理想情况下形貌呈现出六重对称性, 未锂化晶体硅柱是六棱柱形状(如图1所示). 根据这一特点和圆内切正六边形与圆面积比值关系可计算出理想情况下未锂化硅的正六边形截面刚与硅柱圆截面内切时嵌锂深度为17.4%. 因此, 实验所得的相对嵌锂深度结果表明硅电极开裂发生在此情形(与圆截面内切)之后. 为了进一步解释实验现象, 利用ABAQUS建立了二维平面应变有限元模型, 如图6(b)所示. 在单晶硅电极锂化过程的有限元模拟中, 根据两相扩散假设, 通过预定义温度场方法模拟相边界移动速度. 在模型中, 晶体硅和锂化硅分别假设为各向同性的线弹性材料(弹性模量为185 GPa、泊松比为0.28)和弹塑性材料(弹性模量为35 GPa, 泊松比为0.22, 屈服强度为1.5 GPa). 由图6(b)可知, 对于理想嵌锂过程, 两相界面刚过圆截面内切处后不久, 在两个{110}晶面相交处发生了局部应力集中现象, 假设这时达到了裂纹形成的条件. 由模拟结果计算得到起裂时嵌锂深度约22.6%, 并且对于不同的相边界移动速度, 应力集中程度(或裂纹形成)几乎一致, 如图6(c)所示. 换句话说, 基于该有限元模型假设, 发现在不同的嵌锂速度下硅电极起裂时嵌锂深度相同. 这些模拟结果很好地解释了不同电流密度下相对嵌锂深度差异很小的实验结果. 这里需要说明的是, 有限元模型中忽略了锂化硅塑性变形的率相关性[32,33], 即忽略了应变率对锂化硅塑性变形的影响, 只考虑了相界面位置的影响. 对于实验结果所得的相对嵌锂深度小于模拟结果的原因, 可能来源于副反应和硅基底引起的锂损失、实验中非理想嵌锂过程的发生以及模型中忽略率相关塑性的影响所导致的应力偏小[34].

图 6 (a) 不同电流密度下硅电极起裂时相对嵌锂深度; (b) 有限元模拟所得的应力云图; (c) 不同相边界移动速度下不同r/R (红色箭头标示)处径向应力分布

图 6 (a) 不同电流密度下硅电极起裂时相对嵌锂深度; (b) 有限元模拟所得的应力云图; (c) 不同相边界移动速度下不同r/R (红色箭头标示)处径向应力分布Figure6. (a) Relative lithiation depth for crack initiation of silicon electrodes at different current density; (b) hoop stress contour of Si micropillars obtained by finite element method; (c) hoop stress along the radial direction at different moving velocity of phase interfaces.

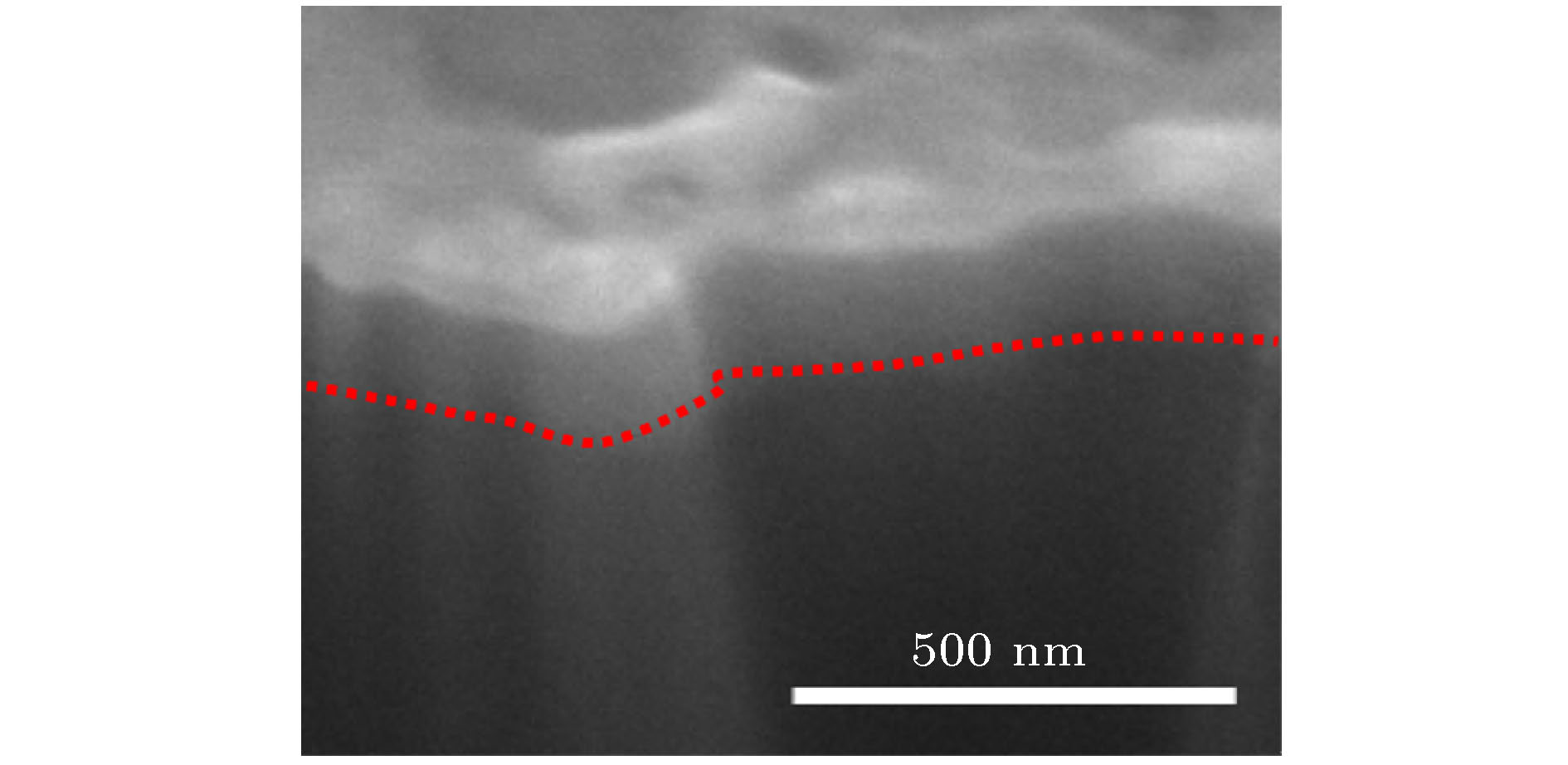

图 7 硅基底锂化后形貌, 标尺为500 nm

图 7 硅基底锂化后形貌, 标尺为500 nmFigure7. Morphology of the silicon substrate after lithiation. Here, the scale bar is 500 nm.

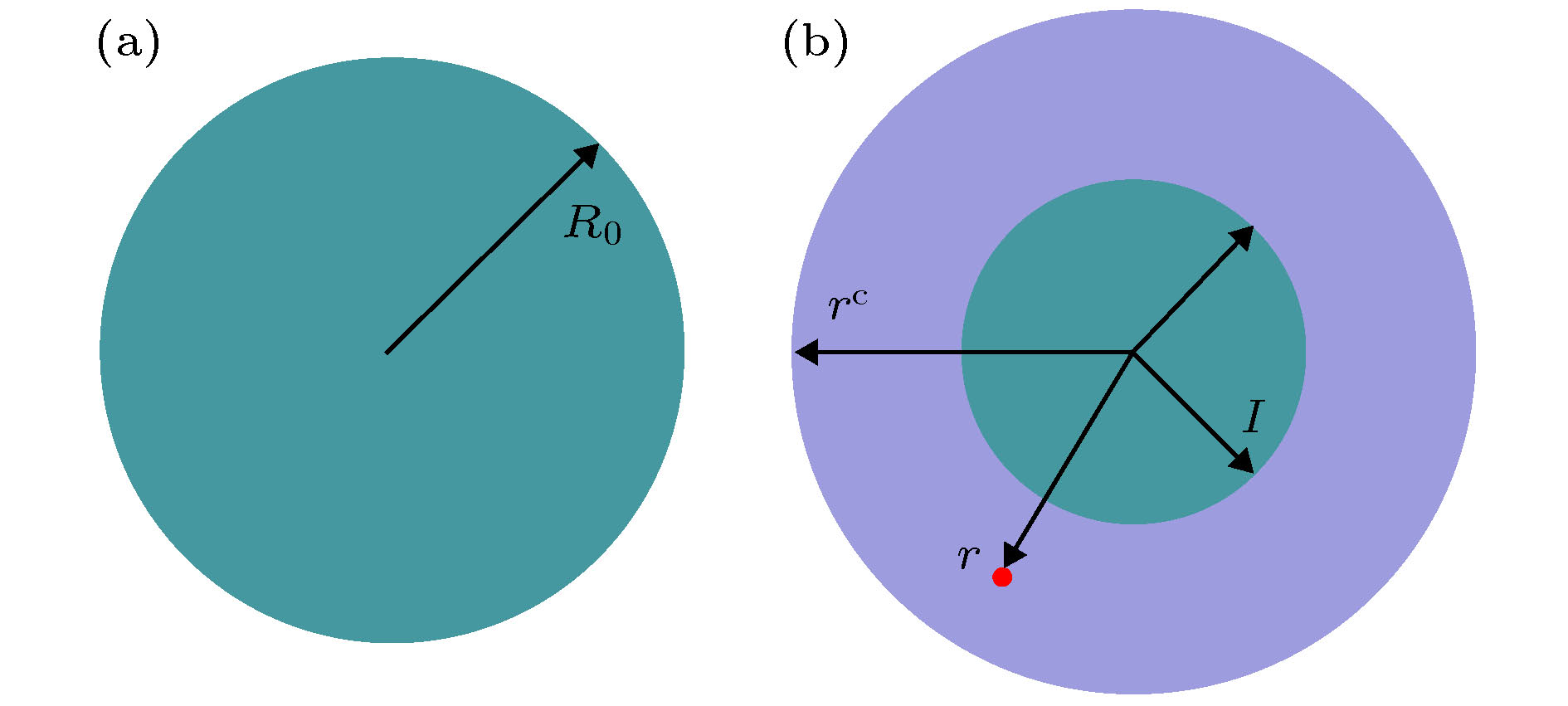

虽然晶体硅电极锂化过程中各向异性变形给理论分析带来了挑战, 但是依然可以通过一些合理的假设建立力学理论模型, 以描述晶体硅电极变形和断裂行为的主要特征[19,20]. 这里, 在理论模型中假设所有晶向的反应前端移动速度相同, 硅柱电极横截面在锂化过程中可分为3个区域(如图8所示): 全锂化区域(I < r ≤ rc)、反应前端(r = I )和未锂化晶体硅区域(0 ≤ r < I ). 基于锂化硅是各向同性的理想刚塑性材料的假设, 参考Jia和Li[19]建立的考虑反应前端移动和体积膨胀变形共存状态下硅柱电极锂化诱导应力的力学模型. 根据此模型, 全锂化区域(I < r ≤ rc)的应力分布可以表示为

图 8 (a) 锂化前硅柱圆截面示意图; (b) 锂化过程中硅柱圆界面示意图

图 8 (a) 锂化前硅柱圆截面示意图; (b) 锂化过程中硅柱圆界面示意图Figure8. Cross-section of a silicon micropillar: (a) Before lithiation; (b) during lithiation.

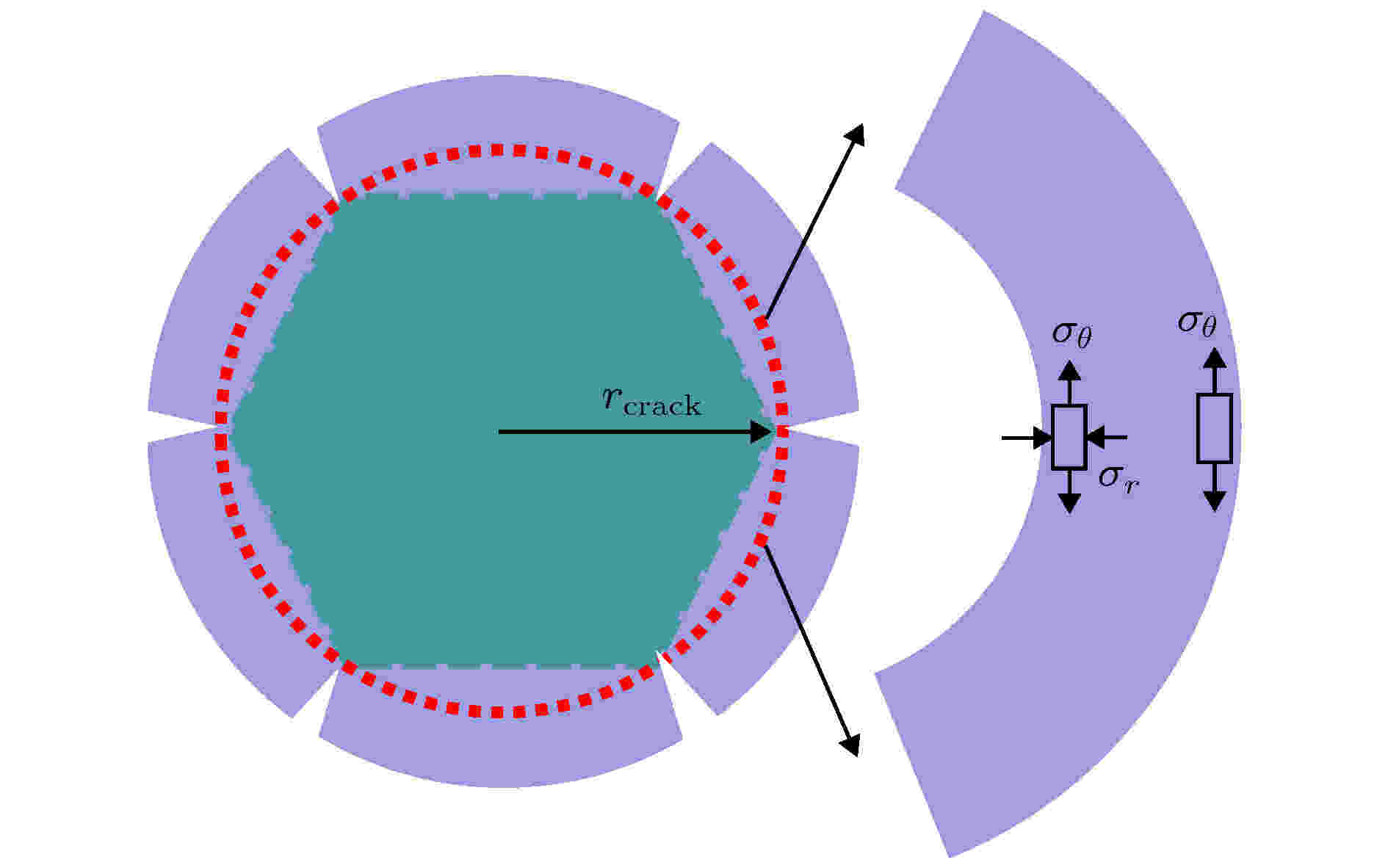

结合上述的实验结果、数值结果和理论分析, 详细分析了微米硅电极的断裂行为, 尤其是裂纹形成阶段. 因为锂化硅内部的应力状态决定了裂纹形成、扩展等过程, 因此有必要进一步分析起裂时全锂化区域的受力状态, 以更好地理解硅电极起裂行为. 上述实验和数值模拟结果已经表明不同电流密度下裂纹形成时的嵌锂深度差异很小(嵌锂深度在18%—22%之间). 理想情况下, 由有限元模型所得的硅柱嵌锂深度对应的rcrack/R约为0.84 (这里rcrack表示裂纹形成时未锂化晶体硅外切圆半径, 如图9所示). 同时从(1)式可以看出, 全锂化区域中靠近相边界I处的环向应力为压应力时, 该位置r小于1/e (< 0.84). 因此, 裂纹形成时靠近相边界附近处的锂化区域内部环向应力也为拉应力状态(如图9所示), 并随着嵌锂的进行将引起裂纹进一步扩展. 这些结果为理解硅电极的断裂机制和大变形合金电极的设计提供了实验和理论指导.

图 9 裂纹形成时硅电极在全锂化区域的受力示意图

图 9 裂纹形成时硅电极在全锂化区域的受力示意图Figure9. Schematic diagram of stress state at the moment of crack initiation.

感谢北京理工大学陈浩森教授的建设性讨论和帮助.