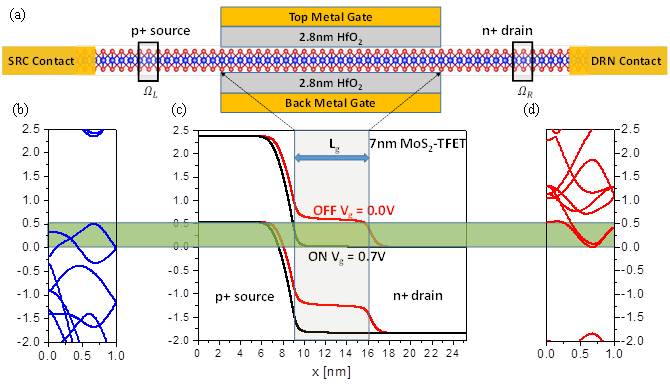

高性能和低功耗是当今微电子器件及其集成电路的两大制高点,在过去半个多世纪晶体管一直按照摩尔定律在不断等比例缩小,晶体管尺寸和芯片集成度当前已经达到了物理极限,提高器件性能和降低器件功耗成为了一对难以调和的矛盾。具有陡直亚阈特性的隧穿场效应晶体管,可以有效解决晶体管的功耗难题,被广泛认为是亚十纳米技术节点的重要备选,国际微电子学术界和Intel等大公司对它开展了大量研究。但是经过近十年的研究发现隧穿场效应晶体管不能同时得到较高的开态电流和较小的亚阈值摆幅,这表明它难以同时用于高性能和低功耗集成电路。为了突破这一物理限制,该课题组从物理原理上寻求突破,在隧穿场效应晶体管的隧穿结处通过引入深能级缺陷来辅助器件开启状态下的带间隧穿,又称作齐纳隧穿,同时在关闭状态下又能将缺陷能级调制出隧穿窗口从而不影响亚阈电流。以二维过渡金属硫化物为例,他们使用密度泛函量子输运方法模拟了亚十纳米隧穿场效应晶体管的器件性能(如图1所示),通过在隧穿结处引入过渡金属空位,他们发现在保持关态电流不变的前提下实现了开态电流数量级的提升(如图2所示),这是一种深能级缺陷调制的共振齐纳隧穿机制。这种共振齐纳隧穿场效应晶体管的概念为研制高性能低功耗的纳米晶体管器件提供了一种新的思路。论文题目为“HowGoodisMono-LayerTransition-MetalDichalcogenideTunnelField-EffectTransistorsinsub-10nm?–AnabinitioSimulationStudy”,IEDM报告链接:http://ieee-iedm.org/session-12-modeling-and-simulation-modeling-of-2d-and-organic-semiconductor-devices/。全文将出现在2015年度的IEDMTech.Dig.p12.4.

该工作得到了国家自然科学基金委的资助。

中国科学院半导体研究所半导体超晶格国家重点实验室的这个课题组和美国劳伦斯伯克利国家实验室的汪林望教授合作,长期从事纳米半导体器件物理及其量子模拟研究,开发了一套拥有自主知识产权的原子尺度全量子器件模拟软件,在该领域发表学术论文二十篇,其中表面科学进展ProgressinSurfaceScience1篇,应用物理快报Appl.Phys.Lett.5篇,微电子器件著名期刊IEEETrans.Elect.Dev.1篇,应用物理期刊J.Appl.Phys.4篇,固态电子学SolidStateElectronics1篇。另外在2012年IEEENUSOD国际会议上作邀请报告,2015年微电子器件领域顶级会议IEDM论文和会议专题报告。

图1:二维过渡金属硫化物隧穿场效应晶体管

图2:Mo空位缺陷调制的MoS2-RZTFET性能提升及其共振隧穿机理