王晨旭1,闫涛1,宫月红2,罗敏1,曾琅3,张德明3,徐天亮1

(1.哈尔滨工业大学(威海) 信息科学与工程学院,山东 威海 264209;2.山东交通学院 航运学院,山东 威海 264200; 3.北京航空航天大学 集成电路科学与工程学院,北京 100191)

摘要:

为了在提高轻量级密码算法(Lightweight cipher algorithm,LWCA)电路安全性的同时降低功耗,提出了一种磁隧道结 (Magnetic tunnel junction,MTJ)/CMOS混合结构查找表(Look up table,LUT)电路,该结构通过与感测放大器逻辑(Sense amplifier based logic, SABL)元件配合可以实现完整的PRESENT-80加密算法电路。设计将MTJ器件引入防护电路设计中,进而提出了一种基于混合MTJ/CMOS结构的双轨查找表(Look-up table,LUT)电路结构。首先,基于40 nm CMOS工艺库和MTJ器件仿真模型,使用新提出的双轨查找表结构设计了加密算法电路工作过程中所需要的关键S-box电路并通过了仿真验证。然后,利用该电路和敏感放大器逻辑元件电路结构组合设计了PRESENT-80密码算法的完整电路。最后对所设计的电路模型进行了相关性功耗分析攻击(CPA)攻击,同时为了方便进行对比研究,还对使用传统CMOS单轨和SABL双轨结构实现的PRESENT-80加密算法电路模型进行了相同条件下的仿真和功耗分析研究。对比仿真结果表明,基于新结构实现的电路具有良好的抗功耗攻击性能,能够抵御10 000条功耗迹下的CPA攻击,同时新结构的电路在工作时的平均功耗要明显低于经典的SABL电路。

关键词: MTJ SABL PRESENT 低功耗 抗CPA攻击

DOI:10.11918/202103131

分类号:TN43

文献标识码:A

基金项目:中国科学院A类战略先导专项项目(XDA19010302);国家自然科学基金(12075142,U2106202);山东省重大科技创新工程(2020CXGC5,1ZLGX05)

Circuit design of cryptographic algorithm using hybrid MTJ/CMOS and SABL structure

WANG Chenxu1,YAN Tao1,GONG Yuehong2,LUO Min1,ZENG Lang3,ZHANG Deming3,XU Tianliang1

(1.School of Information Science and Engineering, Harbin Institute of Technology (Weihai), Weihai 264209, Shandong, China; 2.School of Navigation and Shipping, Shandong Jiaotong University, Weihai 264200, Shandong, China; 3.School of Integrated Circuit Science and Engineering, Beihang University, Beijing 100191, China)

Abstract:

To improve the circuit security of lightweight cipher algorithm (LWCA) and reduce power consumption, we proposed a look-up table (LUT) circuit with magnetic tunnel junction (MTJ)/CMOS hybrid structure, which can realize the complete PRESENT-80 encryption algorithm circuit by combining with sense amplifier based logic (SABL) cells. MTJ cells were introduced into the protection circuits for the design of the LUT circuit with hybrid MTJ/CMOS structure. Firstly, on the basis of 40 nm CMOS process and MTJ simulation model, the proposed LUT architecture was applied to design the S-box circuits which are essential in the operation process of cryptographic algorithm circuits, and results were verified through simulation. Secondly, a complete PRESENT-80 algorithm circuit was designed with the combination of the proposed circuit and SABL cells. Finally, all the circuits were tested by correlation power attack (CPA). Identical simulation and power consumption analysis were conducted on conventional CMOS single-rail and SABL dual-rail circuit structures. Results show that the proposed circuit possessed excellent power consumption attack resistance ability, which was capable of protecting against the CPA attack from 10 000 samples. Besides, the average power consumption of the proposed circuit was apparently reduced compared with that of the traditional SABL circuit.

Key words: magnetic tunnel junction (MTJ) sense amplifier based logic (SABL) PRESENT low power consumption resistance to correlation power attack (CPA)

王晨旭, 闫涛, 宫月红, 罗敏, 曾琅, 张德明, 徐天亮. 采用混合MTJ/CMOS和SABL结构的密码算法电路设计[J]. 哈尔滨工业大学学报, 2022, 54(6): 72-78. DOI: 10.11918/202103131.

WANG Chenxu, YAN Tao, GONG Yuehong, LUO Min, ZENG Lang, ZHANG Deming, XU Tianliang. Circuit design of cryptographic algorithm using hybrid MTJ/CMOS and SABL structure[J]. Journal of Harbin Institute of Technology, 2022, 54(6): 72-78. DOI: 10.11918/202103131.

基金项目 中国科学院A类战略先导专项项目(XDA19010302);国家自然科学基金(12075142, U2106202);山东省重大科技创新工程(2020CXGC010705, 2021ZLGX05) 作者简介 王晨旭(1977-),男,教授 通信作者 宫月红, gongyuehonghit@126.com 文章历史 收稿日期: 2021-03-31

Abstract Full text Figures/Tables PDF

采用混合MTJ/CMOS和SABL结构的密码算法电路设计

王晨旭1, 闫涛1, 宫月红2

, 罗敏1, 曾琅3, 张德明3, 徐天亮1

, 罗敏1, 曾琅3, 张德明3, 徐天亮1 1. 哈尔滨工业大学(威海) 信息科学与工程学院,山东 威海 264209;

2. 山东交通学院 航运学院,山东 威海 264200;

3. 北京航空航天大学 集成电路科学与工程学院,北京 100191

收稿日期: 2021-03-31

基金项目: 中国科学院A类战略先导专项项目(XDA19010302);国家自然科学基金(12075142, U2106202);山东省重大科技创新工程(2020CXGC010705, 2021ZLGX05)

作者简介: 王晨旭(1977-),男,教授

通信作者: 宫月红, gongyuehonghit@126.com

摘要: 为了在提高轻量级密码算法(Lightweight cipher algorithm, LWCA)电路安全性的同时降低功耗,提出了一种磁隧道结(Magnetic tunnel junction,MTJ)/CMOS混合结构查找表(Look up table,LUT)电路,该结构通过与感测放大器逻辑(Sense amplifier based logic, SABL)元件配合可以实现完整的PRESENT-80加密算法电路。设计将MTJ器件引入防护电路设计中,进而提出了一种基于混合MTJ/CMOS结构的双轨查找表(Look-up table,LUT)电路结构。首先,基于40 nm CMOS工艺库和MTJ器件仿真模型,使用新提出的双轨查找表结构设计了加密算法电路工作过程中所需要的关键S-box电路并通过了仿真验证。然后,利用该电路和敏感放大器逻辑元件电路结构组合设计了PRESENT-80密码算法的完整电路。最后对所设计的电路模型进行了相关性功耗分析攻击(CPA)攻击,同时为了方便进行对比研究,还对使用传统CMOS单轨和SABL双轨结构实现的PRESENT-80加密算法电路模型进行了相同条件下的仿真和功耗分析研究。对比仿真结果表明,基于新结构实现的电路具有良好的抗功耗攻击性能,能够抵御10 000条功耗迹下的CPA攻击,同时新结构的电路在工作时的平均功耗要明显低于经典的SABL电路。

关键词: MTJ SABL PRESENT 低功耗 抗CPA攻击

Circuit design of cryptographic algorithm using hybrid MTJ/CMOS and SABL structure

WANG Chenxu1, YAN Tao1, GONG Yuehong2

, LUO Min1, ZENG Lang3, ZHANG Deming3, XU Tianliang1

, LUO Min1, ZENG Lang3, ZHANG Deming3, XU Tianliang1 1. School of Information Science and Engineering, Harbin Institute of Technology (Weihai), Weihai 264209, Shandong, China;

2. School of Navigation and Shipping, Shandong Jiaotong University, Weihai 264200, Shandong, China;

3. School of Integrated Circuit Science and Engineering, Beihang University, Beijing 100191, China

Abstract: To improve the circuit security of lightweight cipher algorithm (LWCA) and reduce power consumption, we proposed a look-up table (LUT) circuit with magnetic tunnel junction (MTJ)/CMOS hybrid structure, which can realize the complete PRESENT-80 encryption algorithm circuit by combining with sense amplifier based logic (SABL) cells. MTJ cells were introduced into the protection circuits for the design of the LUT circuit with hybrid MTJ/CMOS structure. Firstly, on the basis of 40 nm CMOS process and MTJ simulation model, the proposed LUT architecture was applied to design the S-box circuits which are essential in the operation process of cryptographic algorithm circuits, and results were verified through simulation. Secondly, a complete PRESENT-80 algorithm circuit was designed with the combination of the proposed circuit and SABL cells. Finally, all the circuits were tested by correlation power attack (CPA). Identical simulation and power consumption analysis were conducted on conventional CMOS single-rail and SABL dual-rail circuit structures. Results show that the proposed circuit possessed excellent power consumption attack resistance ability, which was capable of protecting against the CPA attack from 10 000 samples. Besides, the average power consumption of the proposed circuit was apparently reduced compared with that of the traditional SABL circuit.

Keywords: magnetic tunnel junction (MTJ) sense amplifier based logic (SABL) PRESENT low power consumption resistance to correlation power attack (CPA)

随着物联网(Internet of things, IoT)和传感器网络技术的快速发展,物联网嵌入式设备的集成度越来越高,对整体功耗的限制也越发严格。由于物联网通信中大量信息不断且频繁地传输,通信安全问题愈发受到人们的重视[1]。目前市场上的嵌入式设备主要使用轻量级密码算法(Lightweight cipher algorithm, LWCA)电路对传输信息进行加密。而随着半导体工艺的快速发展和功耗攻击技术的进步,传统的防护方法如加入掩码或提升算法复杂度[2-3]、使用防护基本单元[4-5]等方法均会带来面积和功耗上的巨大损耗,已经不能满足愈发严格的功耗和安全要求,市场上迫切需要一种兼具低功耗和高安全性的电路解决方案。针对当前现状和存在的问题,本文提出了一种MTJ/CMOS混合结构查找表电路,该结构通过与感测放大器逻辑(Sense amplifier based logic, SABL)元件配合可以实现完整的PRESENT-80加密算法电路。本文使用Cadence软件对设计电路进行仿真并提取电路的功耗信息进行了功耗分析攻击以研究其抗攻击性能。在研究过程中还使用相同的工艺库搭建了传统的CMOS单轨和SABL双轨结构的PRESENT-80电路来实现对比分析,通过一些评估参数的计算来对实验结果进行进一步的量化分析,探究该电路是否具备低功耗特性。

1 基本结构和加密算法 1.1 磁隧道结MTJ由于其良好的电学特性而在研究界引起了广泛的关注,它是由两个铁磁(FM,例如CoFeB)层组成的纳米结构,铁磁层之间由氧化物阻挡层(例如,MgO)隔开,如图 1(a)所示[6]。铁磁层分为参考层和自由层,参考层的磁化方向是固定的,而自由层的磁化方向可以在平行(P)和反平行(AP)方向之间切换,其过程如图 1(b)所示。通过研究发现,当MTJ的铁磁层处于反平行状态时的电阻值(RAP)要明显大于处于平行状态的电阻值(RP),衡量这种电阻特性的参数称为隧道磁阻(RTM)。RTM的具体定义为(RAP-RP)/RP[7]。

Fig. 1

图 1 MTJ结构与切换机制示意 Fig. 1 Schematic of MTJ structure and switching mechanism

图 1 MTJ结构与切换机制示意 Fig. 1 Schematic of MTJ structure and switching mechanism 本文中进行电路设计和仿真使用是基于开源网站Spinmodel library上提供的STT PMA MTJ仿真模型[8],其各项特性参数见表 1。

表 1

kB/J 单位电荷

e/C 约化普朗克常数

?/(J·S) MgO势垒高度

φ/eV 交换刚度

Aex/(J·cm-1) 饱和磁化强度

Ms/(A·m-1) 各向异性场强

Hk/(A·cm-1) 面积电阻指数

RA/(kΩ·m2)

1.38×10-23 1.60×10-19 1.055×10-34 0.4 4×10-13 8.0×105 3.6×105 5×10-12

温度

T/K 自旋极化效

率系数g MTJ侧向直径

a/cm MTJ自由层厚度

d/cm 氧化层厚度

tox/cm 吉尔伯特阻

尼因子α 零偏置TMR

比率/%

300 0.57 2.8×10-6 0.85×10-7 0.85×10-7 0.036 100

表 1 MTJ模型的各项参数 Tab. 1 MTJ model parameters

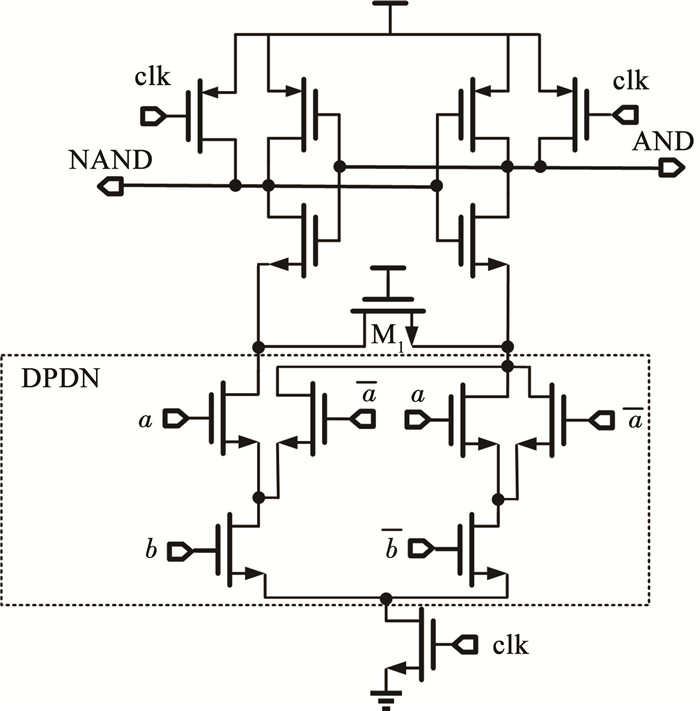

1.2 SABL逻辑SABL是一种经典的抗DPA逻辑结构,该结构由交叉耦合的反相器和差分下拉网络(Differential pull down network, DPDN)组成[9-10]。SABL通用门电路和AND-NAND门电路如图 2所示。整个电路由时钟信号clk驱动,当时钟电平为“0”时,两个输出信号端子都被预充为高电平;当时钟电平为“1”时,两个信号端子之一会根据输入的不同情况被置为低电平。恒定导通的晶体管M1通过用作亚阈值电流的路径来防止浮置节点,并保证所有内部节点都有放电通路[11-12]。

Fig. 2

图 2 SABL与非门示意图 Fig. 2 NAND gate diagram of SABL

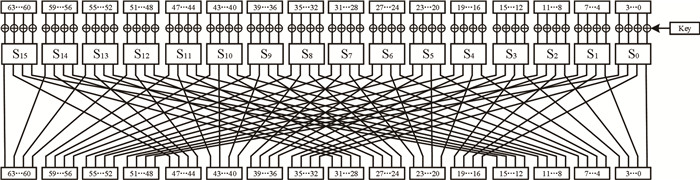

图 2 SABL与非门示意图 Fig. 2 NAND gate diagram of SABL 1.3 PRESENT算法PRESENT是一种轻量级分组加密算法,明文输入为64 bit,密钥长度为80 bit或者128 bit,密文输出为64 bit。其加密过程包括31个常规循环和仅由密钥混合步骤组成的最终循环[13],该算法的加密过程如图 3所示。

Fig. 3

图 3 PRESENT加密过程 Fig. 3 PRESENT encryption process

图 3 PRESENT加密过程 Fig. 3 PRESENT encryption process 图中每轮循环过程需要经历S盒变换、P置换、轮密钥加变换3种数据处理过程,且在最后一轮迭代完成后还需要再与轮密钥进行一次异或运算才能得到最终的密文。PRESENT被广泛应用于低功耗电池供电的嵌入式设备中以进行加解密操作。

2 电路设计和仿真 2.1 多米诺机制对SABL逻辑所述的交叉耦合反相器结构进行改进,得到的电路结构如图 4所示,改进后电路的两输出端各加入了一个反向器。在时钟为“0”时输出信号将被置为“0”,这意味着在逻辑组件级联的计算阶段,下一级组件的DPDN中的NMOS晶体管不会被GND意外地导通。同时,逻辑功能和差分输出不会受到影响,这种信号传输机制称为多米诺机制[14]。

Fig. 4

图 4 改进后的交叉耦合反相器结构 Fig. 4 Improved cross-coupled inverter structure

图 4 改进后的交叉耦合反相器结构 Fig. 4 Improved cross-coupled inverter structure 2.2 混合MTJ/CMOS结构S-box电路S-box电路是对被加密数据进行非线性变换的基本单元。每个S-box电路有4位输入和4位输出,其对应关系见表 2。

表 2

S(x) C 5 6 B 9 0 A D 3 E F 8 4 7 1 2

表 2 PRESENT-80 S-box输入输出关系 Tab. 2 Input and output relationship of PRESENT-80 S-box

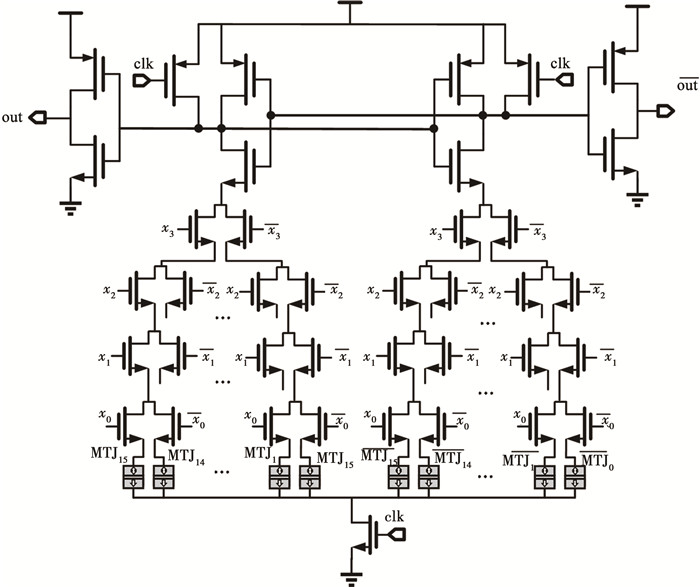

本文提出了一种基于MTJ/CMOS的LUT(look up table)电路结构,在该结构的设计中使用了多米诺机制,从而避免在与其他组件进行级联时信号逻辑发生错误。基于该结构设计的互补四输入的LUT电路如图 5所示,该电路在工作开始之前,需要预先通过写入电路在MTJ中写入指定的数据。在电路工作时,会通过输入选择信号来定位到LUT中相应MTJ中存储的数据,并通过图 4所示的多米诺机制的交叉耦合反相器将数据读取出来。与传统的SRAM等存储电路相比,将MTJ作为存储单元主要有两大优势。首先,使用传统方式实现S-box电路得到的电路会比较复杂,静态功耗大。而MTJ在工作时的静态电流几乎为零,因此使用MTJ进行设计能够大大降低了电路的功耗。其次,MTJ是性能良好的非易失器件,在掉电的情况下其存储的信息也能长时间的保存,这样的特性恰恰与S-box电路相契合,因为非线性变换的输入与输出关系是固定的,数据写入后就不需要再被改写或者频繁刷新。如果使用SRAM一类的传统存储单元设计电路,则每次给电路通电时都必须刷新数据从而带来额外的功耗。

Fig. 5

图 5 基于MTJ/CMOS的查找表电路 Fig. 5 Look-up table circuit based on MTJ/CMOS

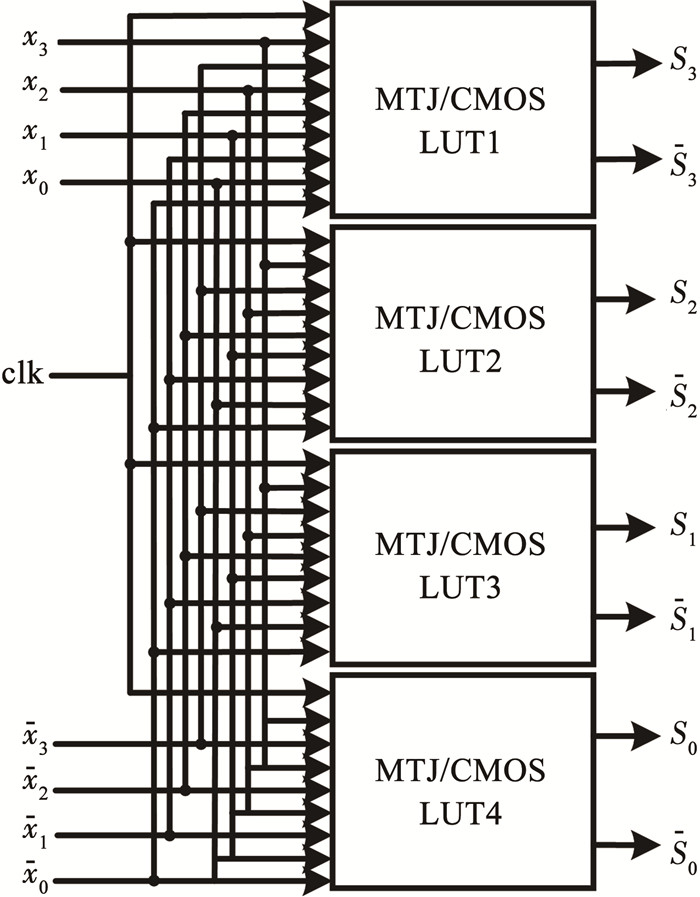

图 5 基于MTJ/CMOS的查找表电路 Fig. 5 Look-up table circuit based on MTJ/CMOS Kumar等[15]提出了一种使用基于混合MTJ/CMOS内存中逻辑LUT的电路实现PRESENT-80 S-box电路的方法,PRESENT-80 S-box电路由4个的LUT电路组成,如图 6所示,表 3中显示了每个LUT中以MTJ编写的内容,该方法适用于低功耗硬件设计[15-17]。然而,文献[15]中只实现了一轮加密过程,没有对密钥更新和电路级联问题给出明确的解决方案。针对这一问题,本文提出的电路结构可以与满足多米诺机制的标准SABL逻辑单元实现级联,很好的解决了这一问题,进而可以实现完整的加密电路设计。对于加密算法而言,满足此级联连接非常重要,因为由于整个算法中需要多次加密,数据会参照时钟进行频繁的迭代,因此S-box与其他逻辑单元之间的级联连接是必须的。

Fig. 6

图 6 PRESENT-80双轨S-box电路框图 Fig. 6 Block diagram of PRESENT-80 dual-rail S-box circuit

图 6 PRESENT-80双轨S-box电路框图 Fig. 6 Block diagram of PRESENT-80 dual-rail S-box circuit 表 3

MTJ0 1 1 0 0

MTJ1 0 1 0 1

MTJ2 0 1 1 0

MTJ3 1 0 1 1

MTJ4 1 0 0 1

MTJ5 0 0 0 0

MTJ6 1 0 1 0

MTJ7 1 1 0 1

MTJ8 0 0 1 1

MTJ9 1 1 1 0

MTJ10 1 1 1 1

MTJ11 1 0 0 0

MTJ12 0 1 0 0

MTJ13 0 1 1 1

MTJ14 0 0 0 1

MTJ15 0 0 1 0

表 3 查找表电路中各MTJ存储数据 Tab. 3 MTJ stored data in look-up table circuit

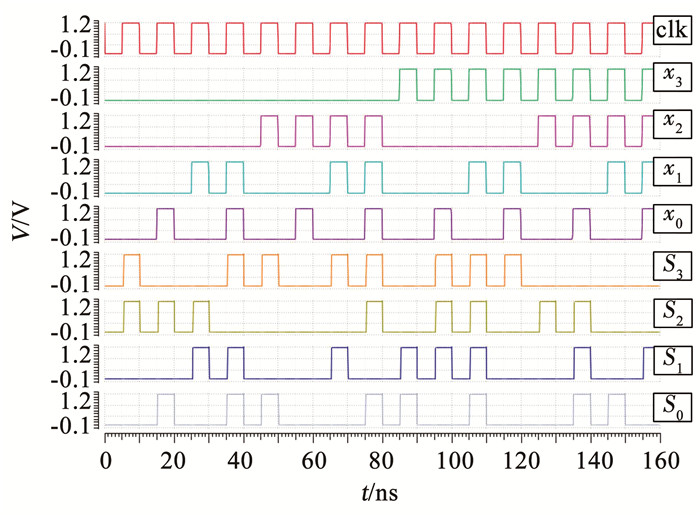

参考文献[15]中的结构用本文提出的查找表电路设计了S-box电路。基于SMIC 40 nm CMOS工艺和MTJ仿真模型在Cadence Spectre模拟器中对S-box电路进行功能仿真。在仿真过程中,从选择信号端输入由0x0到0xF的多米诺机制激励,最终获得的仿真结果如图 7所示。分析图像可以看出当时钟为“0”时,所有信号均被驱动为“0”。相反,当时钟为“1”时,信号代表的逻辑值对应关系与表 2完全一致,证明所设计的电路功能是完全正确的。

Fig. 7

图 7 MTJ/CMOS S-box电路仿真结果 Fig. 7 MTJ/CMOS S-box circuit simulation results

图 7 MTJ/CMOS S-box电路仿真结果 Fig. 7 MTJ/CMOS S-box circuit simulation results 2.3 PRESENT-80加密电路的实现图 8显示了PRESENT-80的一轮加密过程,可以看出除了密钥输入部分和S-box(S15~S0)之外,算法的实现还需要大量异或门。标准PRESENT-80算法中的密钥每轮都会迭代更新,如果使用MTJ/CMOS结构电路实现这些异或门,则会带来额外的能量损失同时提高被功耗攻击的风险。因此最终选择使用满足多米诺机制SABL异或门来完成该部分的逻辑实现。

Fig. 8

图 8 一轮PRESENT-80加密过程框图 Fig. 8 Block diagram of a round of PRESENT-80 encryption process

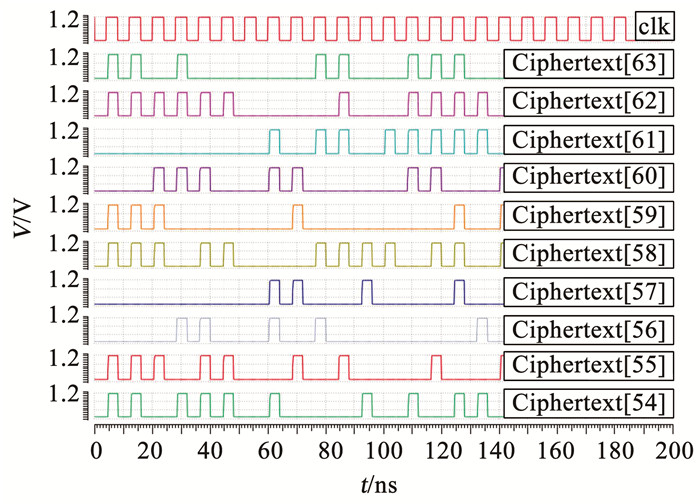

图 8 一轮PRESENT-80加密过程框图 Fig. 8 Block diagram of a round of PRESENT-80 encryption process 同样用Cadence Spectre模拟器来模拟PRESENT-80电路的完整工作过程。在仿真过程中为了节省仿真资源,算法中除去关键的轮加密部分电路外的执行其他数据处理任务的电路使用硬件描述语言建立功能模型的方式代替。在仿真中, 原始的明文设置为0x0044003300220011,原始密钥设置为x0123456789ABCDEF0123。图 9显示了32轮加密过程中部分密文输出信号的仿真波形。经过检查该结果与相同输入情况下标准算法的处理结果完全一致,由此可以证明本文设计的电路可以正确实现PRESENT-80加密算法电路的功能。

Fig. 9

图 9 32轮加密过程中部分密文信号的波形 Fig. 9 Waveform of part of ciphertext signal during 32 rounds of encryption

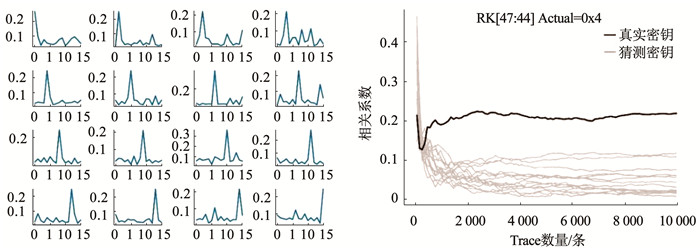

图 9 32轮加密过程中部分密文信号的波形 Fig. 9 Waveform of part of ciphertext signal during 32 rounds of encryption 3 电路性能评估和分析要验证本文所设计的电路结构是否具备良好的抗攻击特性,需要对电路进行功耗攻击分析测试。学者Kocher[18]最早提出了差分功耗攻击(Differential power analysis,DPA)的概念。DPA攻击利用了电路中由晶体管功耗变化引起的功耗波动来分析加密电路信息。通过跟踪这些波动并分析电路特定部分的功耗就可以获得加密信息(例如密钥),同时不会影响设备的任何物理特性[19]。本文选取了一种改进型的差分功耗攻击模型,即相关性功耗分析攻击(Correlation power attack, CPA)模型[20],该模型在使用中需要选择合适的攻击点测量得到功耗信息矩阵,与假设功耗矩阵进行对比得到它们之间的相关系数,相关系数最高的便是密钥值。基于10 000条功耗迹对传统CMOS单轨PRESENT-80电路进行CPA攻击,设定的攻击目标为首轮加密的64 bit密钥,其真实值为0x0123456789ABCDEF。攻击过程分16组,每组攻击4 bit,攻击的结果如图 10所示,其中左侧为攻击每组密钥的相关系数曲线,右侧为攻击第47~44位密钥过程中相关系数与功耗迹条数的关系曲线,其中深色曲线为真实密钥的相关系数曲线。结果显示,真实密钥被成功破解,且确保攻击成功所需要的功耗迹条数在1 000条左右。

Fig. 10

图 10 PRESENT-80单轨电路CPA攻击结果 Fig. 10 CPA attack results of PRESENT-80 single-rail circuit

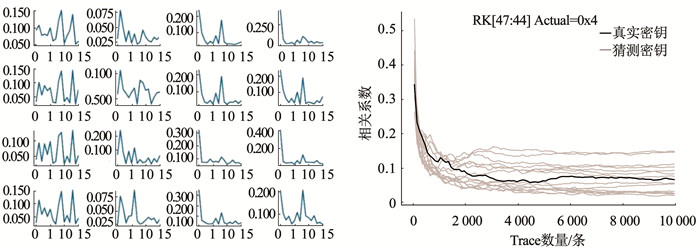

图 10 PRESENT-80单轨电路CPA攻击结果 Fig. 10 CPA attack results of PRESENT-80 single-rail circuit 使用相同的攻击模型对本文中所设计的密码算法电路进行CPA攻击,其攻击结果如图 11所示,攻击得到的首轮密钥值为0xD1009B00D6009100,攻击未成功,同时可以看出真实密钥的相关性一直被很好的隐藏与各猜测密钥之中且随着功耗迹数目的增加相关性变化趋于稳定。对比上述结果,可以证明本文中设计的电路结构具有良好的抗攻击性能。

Fig. 11

图 11 MTJ/CMOS PRESENT-80电路CPA攻击结果 Fig. 11 CPA attack results of MTJ/CMOS PRESENT-80 circuit

图 11 MTJ/CMOS PRESENT-80电路CPA攻击结果 Fig. 11 CPA attack results of MTJ/CMOS PRESENT-80 circuit 为了便于对逻辑单元的抗功耗攻击性能进行量化分析,需要统一的衡量指标。目前普遍使用的评估标准主要有如下几种[5]:

1) 归一化功耗差(Normalized energy deviation, NED)。

${\rm{NED}} = \frac{{{E_{\max }} - {E_{\min }}}}{{{E_{\max }}}}$ (1)

式中, Emax、Emin分别为电路在电路单个周期内的功耗的最高值和最低值,定义如下:

$E = {V_{{\rm{DD}}}} \cdot \bar I \cdot {T_{{\rm{CLK}}}} = {V_{{\rm{DD}}}} \cdot \int_0^{\rm{T}} {{I_{{\rm{DD}}}}} (t){\rm{d}}t$

2) 归一化标准差(Normalized standard deviation, NSD)。

${\rm{NSD}} = \frac{{{\sigma _{\rm{E}}}}}{{\bar E}}$ (2)

3) 归一化电流差(Normalized current deviation, NCD)。

${\rm{NCD}} = \frac{{{C_{\max }} - {C_{\min }}}}{{{C_{\max }}}}$ (3)

式中, Cmax、Cmin分别为每个参考周期的峰值电流的最高值和最低值。

根据功耗攻击的原理可以发现,目标电路的NED,NSD和NCD数值越低,抗攻击的特性就越好。对PRESENT-80加密电路的工作过程进行仿真可以提取加密算法电路的工作电流,并以此计算出相应的NED,NSD和NCD。为了便于进行比较和分析,本文在相同的仿真环境下建立了另外两套基于40 nm CMOS工艺的PRESENT加密电路模型,分别使用了传统的单轨CMOS逻辑单元和SABL逻辑单元在相同的实验条件下设计了加密电路模型并完成了仿真。所有电路仿真后得到的电流数据如图 12所示,基于此计算出的抗攻击评估指标和E见表 4。

Fig. 12

图 12 不同电路的工作电流仿真结果 Fig. 12 Simulation results of power supply current of different circuits

图 12 不同电路的工作电流仿真结果 Fig. 12 Simulation results of power supply current of different circuits 表 4

CMOS 33.060 1.907 44.910 2.42

SABL 0.110 0.007 0.050 12.59

MTJ/CMOS 0.390 0.004 0.030 5.64

表 4 PRESENT-80的CMOS、SABL和MTJ/CMOS电路的评估指标 Tab. 4 Evaluation indicators of CMOS, SABL, and MTJ/CMOS circuits for PRESENT-80

从3种电路仿真计算得出的NED、NSD和NCD比较中可以看出,使用MTJ/CMOS结构S-box电路设计的电路的抗攻击特性与SABL标准单元加密电路相近,且明显优于传统的CMOS电路。同时,含MTJ/CMOS结构的加密电路的平均功耗E高于传统的单轨CMOS电路,但是其功耗要显著低于SABL结构电路。综上所述,本文提出的基于MTJ/CMOS LUT结构和改进后SABL单元设计的PRESENT加密算法电路可以在不增加过多功耗的前提下显著提高电路的抗攻击能力,具有一定的性能优势。

4 结论1) 本文提出的混合MTJ/CMOS结构的LUT电路能够正确实现密码算法中S-box的功能,并且可以与符合多米诺级联机制的SABL电路进行级联电路设计。

2) 混合MTJ/CMOS结构LUT电路具有良好的电路级防护性能,使用其设计的密码算法电路能够抵御10 000条功耗迹的CPA攻击。

3) 在同等工艺条件下,使用混合MTJ/CMOS结构设计的密码电路相较于传统的SABL结构电路功耗会有显著的降低。

参考文献

[1] SHEBLI H M Z A, BEHESHTI B D. Light weight cryptography for resource constrained IoT devices[J]. Advances in Intelligent Systems and Computing, 2019(880): 196. DOI:10.1007/978-3-030-02686-8_16

[2] NIKOVA S, RIJMEN V, SCHL?FFER M. Secure hardware implementation of nonlinear functions in the presence of glitches[J]. Journal of Cryptology, 2011, 24(2): 292. DOI:10.1007/s00145-010-9085-7

[3] BILGIN B, NIKOVA S, NIKOV V, et al. Threshold implementations of small S-boxes[J]. Cryptography and Communications, 2015, 7(1): 3. DOI:10.1007/s12095-014-0104-7

[4] TIRI K, VERBAUWHEDE I. A logic level design methodology for a secure DPA resistant ASIC or FPGA implementation[C]//Proceedings Design, Automation and Test in Europe Conference and Exhibition. Paris, France: IEEE, 2004: 246. DOI: 10.1109/DATE.2004.1268856

[5] 吴静. 抗DPA攻击的标准单元库及密码算法的研究与实现[D]. 长沙: 国防科学技术大学, 2010

WU Jing. The research and implementation of DPA-resistant standard cells and encryption arithmetic[D]. Changsha: National University of Defense Technology, 2010

[6] YUASA S, NAGAHAMA T, FUKUSHIMA A, et al. Giant room-temperature magnetoresistance in single-crystal Fe/MgO/Fe magnetic tunnel junctions[J]. Nature Materials, 2004, 3(12): 868. DOI:10.1038/nmat1257

[7] WANG Kang, ZHANG Yue, WANG Zhaohao, et al. Spintronics: Emerging Ultra-Low-Power circuits and systems beyond MOS technology[J]. ACM Journal on Emerging Technologies in Computing Systems, 2015, 12(2): 1. DOI:10.1145/2663351

[8] MOODERA J S, KINDER L R, WONG T M, et al. Large magnetoresistance at room temperature in ferromagnetic thin film tunnel junctions[J]. Physical Review Letters, 1995, 74(16): 3273. DOI:10.1103/PhysRevLett.74.3273

[9] WANG You, CAI Hao, NAVINER L A D B, et al. Compact model of dielectric breakdown in spin transfer torque magnetic tunnel junction[J]. IEEE Transactions on Electron Devices, 2016, 63(4): 1762. DOI:10.1109/TED.2016.2533438

[10] TIRI K, VERBAUWHEDE I. Design method for constant power consumption of differential logic circuits[C]//Design, Automation & Test in Europe. Munich, Germany: IEEE, 2005: 628. DOI: 10.1109/DATE.2005.113

[11] TIRI K, AKMAL M, VERBAUWHEDE I. A dynamic and differential CMOS logic with signal independent power consumption to withstand differential power analysis on smart cards[C]//Proceedings of the 28th European Solid-State Circuits Conference. Florence, Italy: IEEE, 2002: 403

[12] KIM J C, JANG Y C, PARK H J. CMOS sense amplifier-based flip-flop with two N-(CMOS)-M-2 output latches[J]. Electronics Letters, 2000, 36(6): 498. DOI:10.1049/el:20000409

[13] TIRI K, VERBAUWHEDE I. Charge recycling sense amplifier based logic: Securing low power security IC's against DPA[C]//Proceedings of the 30th European Solid-State Circuits Conference. Leuven, Belgium: IEEE, 2004: 179. DOI: 10.1109/ESSCIR.2004.1356647

[14] BOGDANOV A, KNUDSEN L R, LEANDER G, et al. PRESENT: An Ultra-Lightweight block cipher[C]//Proceedings of the 9th International Workshop on Cryptographic Hardware and Embedded Systems. Berlin, Heidelberg: Springer, 2007: 450. DOI: 10.1007/978-3-540-74735-2_31

[15] KUMAR S D, THAPLIYAL H. Exploration of non-volatile MTJ/CMOS circuits for DPA-resistant embedded hardware[J]. IEEE Transactions on Magnetics, 2019, 55(12): 1. DOI:10.1109/TMAG.2019.2943053

[16] MANGARD S, OSWALD E, POPP T. Power analysis attacks-revealing the secrets of smart cards[M]. Berlin, Heidelberg: Springer Publishing Company, 2010.

[17] ZHAO Weisheng, Moreau M, DENG E, et al. Synchronous non-volatile logic gate design based on resistive switching memories[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2014, 61(2): 443. DOI:10.1109/TCSI.2013.2278332

[18] KOCHER P, JAFFE J, JUN B. Differential power analysis[C]//Proceedings of the Annual International Cryptology Conference. Berlin Heidelberg: Springer, 1999: 388. DOI: 10.1007/3-540-48405-1_25

[19] WINOGRAD T, SALMANI H, MAHMOODI H, et al. Hybrid STT-CMOS designs for reverse-engineering prevention[C]//Proceedings of the 53nd ACM/EDAC/IEEE Design Automation Conference(DAC). Austin, TX: IEEE, 2016: 5. DOI: 10.1145/2897937.2898099

[20] DUAN Xiaoyi, CU Qi, WANG Sixiang, et al. Differential power analysis attack and efficient countermeasures on PRESENT[C]//Proceedings of 2016 8th IEEE International Conference on Communication Software and Networks. Beijing: IEEE, 2016: 8. DOI: 10.1109/ICCSN.2016.7586627

[21] 王晨旭, 赵占锋, 喻明艳, 等. Piccolo相关性功耗分析攻击技术研究[J]. 哈尔滨工业大学学报, 2013, 45(9): 17.

WANG Chenxu, ZHAO Zhanfeng, YU Mingyan, et al. Research on correlation power analysis attack against Piccolo[J]. Journal of Harbin Institute of Technology, 2013, 45(9): 17. DOI:10.11918/j.issn.0367-6234.2013.09.004