中国科学院半导体研究所半导体超晶格国家重点实验室的张钊研究员研制出一款极低电压极低功耗的锁相环时钟生成器(Phase Locked Loop),首次实现了工作电压低至0.25-V且频率超过100 MHz的PLL,并且功耗效率首次达到9.5 μW/GHz。相关研究成果以题目为 “A 0.25–0.4-V, Sub-0.11-mW/GHz, 0.15–1.6-GHz PLL Using an Offset Dual-Path Architecture With Dynamic Charge Pumps”的论文发表在集成电路芯片设计领域的顶级学术期刊IEEE Journal of Solid-State Circuits (JSSC)上。该论文由中国科学院半导体研究所与香港科技大学合作发表,张钊是这篇论文的第一作者和通讯作者。

锁相环时钟生成器是各类片上系统(System-on-chip)中的关键模块/子系统,其主要目的为生成满足各类系统需求的高质量时钟信号,让SoC中的各个子系统能够正确协同工作。是各类SoC芯片中的“心脏”,其功耗通常较高。在无线传感器节点中,为了提高设备的电池待机时间,甚至为了满足环境能量收集这类自供电方式的需求,通常需要工作在极低电源电压下(<0.4 V),且消耗极低功耗。这对用于该类应用的PLL设计提出了新的挑战。

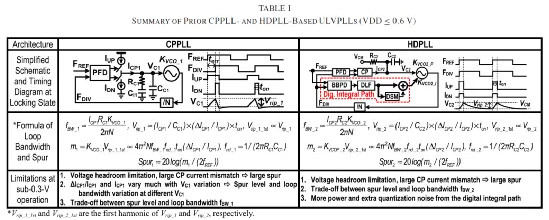

传统PLL中的关键模块电荷泵(Charge Pump, CP)需要有较好的电流匹配度来降低输出时钟杂散,而较好的CP电流匹配度需要较高的CP输出阻抗来保证;这通常需要通过提高电源电压来保证足够高的MOS管漏源电压(VDS)来实现;因此,传统PLL所需工作电压较高(之前已报道的PLL工作电压≥0.4 V),需要用到升压变换器来生成PLL所需电源电压,不仅PLL功耗大,而且升压变换器会引入额外的能量损耗。

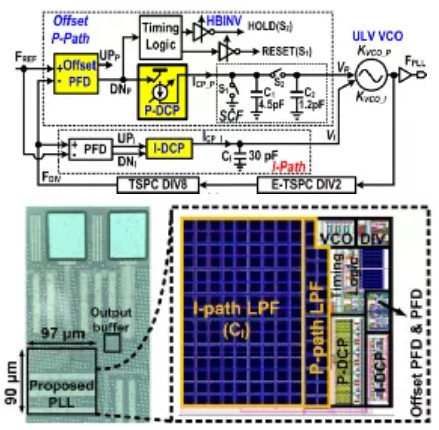

而本文提出的静态相位差容忍型双环路PLL结构(Offset Dual-Path Loop Architecture),可以降低PLL对其CP电流匹配度要求,让PLL在CP电流严重失配的前提下依然能够生成参考杂散(reference spur)满足需求的时钟,从而降低CP的设计难度,进而降低CP以及整个PLL的所需电压至0.4 V以下(最低达到0.25 V),且避免使用升压变化器,并最终达到降低PLL工作电压与功耗的目的。此外,还提出了动态CP(Dynamic Charge Pump)电路技术,去掉传统CP中所有消耗静态功耗的电路,进一步降低PLL的功耗。

该工作为用于无线传感器节点的SoC芯片提供了极低电压极低功耗时钟/无线载波生成器解决方案,能有效满足无线传感器节点超长待机时间或自供电需求。

图1. 传统PLL优缺点总结

图2. 提出的极低电压及低功耗的锁相环时钟生成器框图及其芯片照片

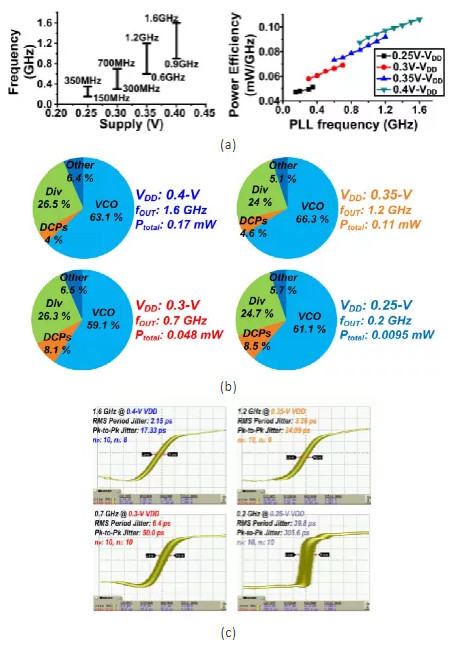

图3. 芯片主要测试结果:(a)工作电压、频率范围与功耗效率;(b)不同电压下功耗值;(c)不同电源电压下输出时钟抖动。

论文链接:https://ieeexplore.ieee.org/document/9226441