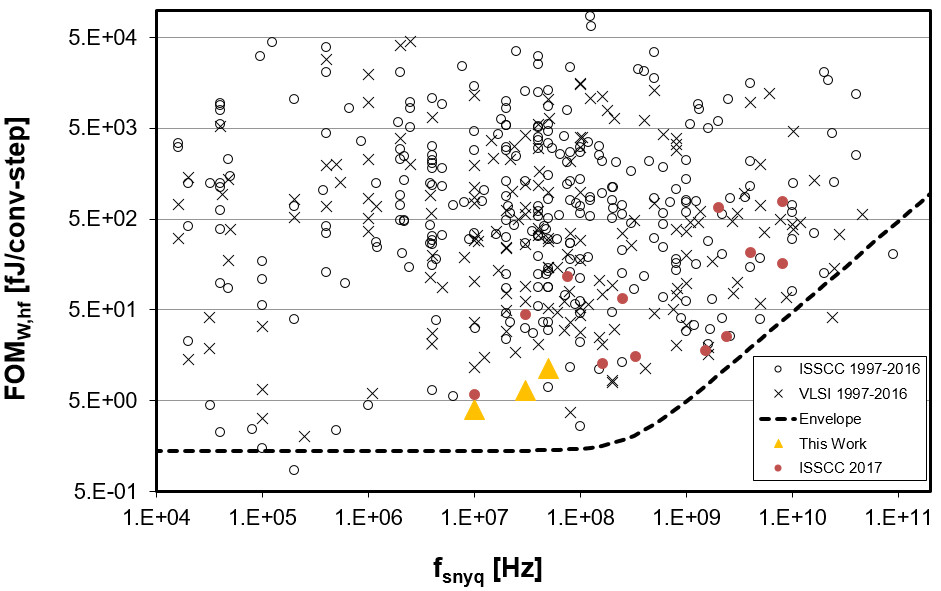

该款ADC采用了基于量程辅助、逐次逼近、流水线等技术的混合型架构,在国际上首次提出高增益(32倍)PVT不敏感的时间域放大器,显著降低了ADC的功耗及校准算法复杂度,提出了量程辅助的悬空电容阵列开关算法及预开窗异步控制逻辑,提高了ADC的转换速率。该ADC在130nm CMOS工艺下流片成功,有效核心面积0.22 mm2。测试结果表明,在1.2 V供电、50 MS/s转换速率下,输入信号为2 MHz时,ADC的信噪失真比(SNDR)达71.6 dB,无杂散动态范围(SFDR)达84.6 dB。该ADC支持可变电源电压与转换速率,当电源电压从0.8 V变化到1.2 V时,ADC的转换速率为10-50 MS/s,Walden FOM值为4.0-11.3 fJ/conversion-step。

此项工作主要由樊晓华研究员、张明磊博士完成,得到了美国德克萨斯农工大学 Edgar Sánchez-Sinencio教授的支持。该款ADC可满足当前高速发展的片上集成系统对低功耗、高速度以及高精度等特性的严格要求,可运用于多种便携式通信系统的应用场景。相关研究成果已被国际顶级期刊 IEEE Journal of Solid State Circuits 接收。

图1. ADC芯片照片

图2. 不同模式下SFDR/SNDR随输入频率的变化

图3. FOM值与国际顶级会议(ISSCC/VLSI)的比较