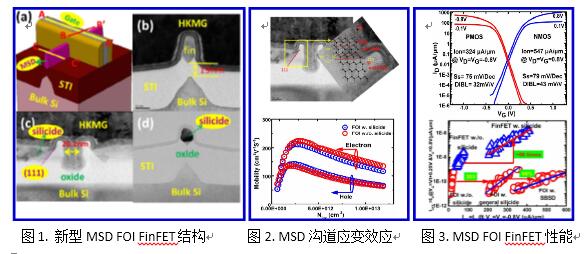

随着主流FinFET器件工艺的持续微缩,其在栅控与性能提升上面临越来越大的技术挑战。微电子所殷华湘研究员的课题组相继提出S-FinFET、后栅纳米线及体硅绝缘Fin-on-insulator(FOI)FinFET等创新技术(图1-3),探索采用新型器件结构来突破未来主流集成电路工艺微缩限制的可能技术方法。然而这些新器件结构虽然栅控更为优秀却面临性能不足,弱于主流FinFET工艺的巨大挑战。针对这些挑战,研究小组利用低温低阻NiPt硅化物在新型FOI FinFET上实现了全金属化源漏(MSD),显著降低源漏寄生电阻,从而将N/PMOS器件性能提高大约30倍,使得驱动性能达到了国际先进水平。基于本研究成果的论文“FOI FinFET with Ultra-low Parasitic Resistance Enabled by Fully Metallic Source and Drain Formation on Isolated Bulk-fin”(通讯作者:殷华湘、张青竹,Session 17.3)被2016年IEEE国际电子器件大会(IEDM)接收,并在IEDM的关键分会场之一——硅基先导CMOS 工艺和制造技术(PMT)上由第一作者张青竹作了学术报告。约700名来自全球集成电路逻辑器件与工艺技术领域的知名专家聆听了该报告,报告内容得到IBM、意法半导体和海思半导体等国际知名主流集成电路公司的热切关注,并在会后进行了充分的交流。该技术成果同时得到IBM公司主管先进集成电路技术研发的经理H. Bu的高度评价和充分的认可,意法半导体的高级技术专家P. Morin也高度赞扬该文所提出的技术方案。

当前主流FinFET(Tri-gate)器件工艺是16/14nm以及10nm节点集成电路制造的关键技术。预计在7-5nm及以下技术代漏电流控制和源漏寄生电阻问题面临严重的技术挑战。SOI器件具有天然的介质隔离,漏电流和寄生电容更小、速度快,但是面临高昂的衬底成本和驱动性能差等难题。兼容主流体硅FinFET工艺,通过体硅衬底形成介质隔离的类SOI器件,即FOI FinFET已经成为重要的研究方向,但是该类器件由于介质隔离的硅fin更小,源漏寄生电阻已经成为限制其驱动性能最大的制约因素。采用基于低温低阻NiPt硅化物的全金属化源漏在介质隔离上可以有效消除常规体fin上的漏电影响,并大幅降低源漏寄生电阻,使实际物理栅长为20nm的FOI FinFET的源漏接触电阻和方块电阻分别减小10倍和1.1倍,从而将N/P型FOI FinFET器件性能提高大约30倍,并且维持新结构的优异短沟道抑制特性。此外,由NiPt全金属源漏与Si界面的晶格失配在沟道中产生了附加张应力,有效地增强了电子迁移率,为N型 FOI FinFET的沟道迁移率增强技术提供新的集成方案。同时通过肖特基源漏(SBSD)技术使源漏寄生电阻进一步降低,有效地提升了P型 FOI FinFET器件驱动性能(大于50%)。研究结果表明,全金属化源漏FOI FinFET相比类似工艺的常规FinFET漏电降低1个数量级,驱动电流增大2倍,驱动性能在低电源电压下达到国际先进水平。由于替代了传统的源漏SiGe外延技术,与极小pitch的大规模FinFET器件的兼容性更好,有助于降低制造成本,提高良品率,具有很高的技术价值。