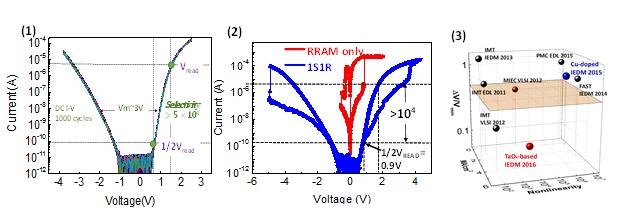

交叉阵列中的漏电流问题是存储器高密度集成的主要障碍。在1T1R结构中,晶体管作为选通管隔绝了旁路漏电,但晶体管不适用于三维堆叠。因此,开发具有高均一性、高选择比、高电流密度、可三维堆叠的选通器件是实现RRAM的三维集成的关键。现有的选通管器件很难同时满足上述几个要求。针对该问题,刘明团队提出了利用梯形能带结构的构建选通管器件的思路,开发了一种具有高度均一性,同时具有较高选择比和电流密度的选通器件,其漏电流<10 pA,非线性比>50000,开态电流密度>1MA/cm2以及超高耐久性(>1010)。

IEEE国际电子器件大会始创于1954年,是报道半导体及电子领域最新的科技、研发设计、制造、物理学及建模技术的主要论坛,为产学研界的研究****提供关于电子器件最新研究进展和研究成果的国际交流平台。

(1)高均一性高选择比的选择器的典型I-V特性。(2)1RRRAM和集成选通器1S1R结构的I-V特性。(3)各类选通管器件性能参数对比。