随着深度神经网络(DNN)研究的不断发展,神经网络模型推理智能物联网设备得到广泛应用,涵盖图像识别、视频处理、自然语言处理等多个任务。然而,随着DNN模型的发展,网络参数和计算量快速增加给计算和存储受限的边缘设备带来新的挑战。随机计算(SC)作为一种基于概率计算的计算方法被提出,其通过使用比特流代替传统二进制编码进行计算,有望实现高面积效率的算术电路和很好的容错性,非常适合用于边缘计算的神经网络加速。

随机计算(SC)用于网络加速的相关研究已经有许多,研究者们通过优化乘法器或整体电路使SC网络加速的性能显著提升。即便如此,之前的工作仍然面临着推理效率和准确率的本征矛盾:算术运算精度的提高虽然能够提升推理准确率,但会导致硬件计算代价指数级增长;相反,降低算术运算精度能提升计算效率,但会直接降低推理的准确率。

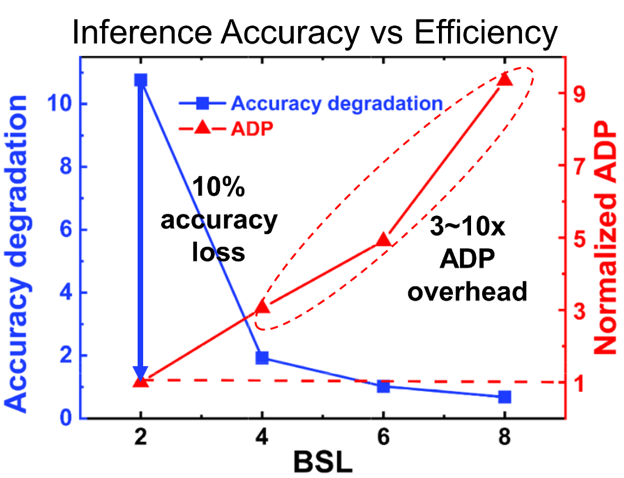

如图1所示,用短比特流(例如2比特)的低精度随机计算电路非常高效,但造成了10%准确率降低;而更长的比特流可以提高精度,却需要承担3到10倍的硬件开销代价。

图1. 随机计算(SC)推理准确率与电路效率随比特流长度的变化趋势

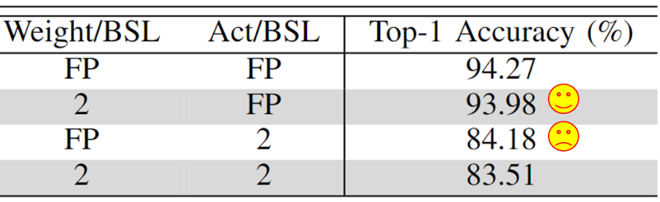

针对以上SC电路面临的无法兼顾神经网络推断准确率和电路效率的问题,本文所述工作对CIFAR10上ResNet18的权重和激活分别进行量化并深入探究。结果发现,对激活值的量化更显著地影响了网络准确率,因而低精度的激活值是准确率的主要瓶颈。因此,该工作从神经网络模型结构和电路方面进行协同优化,提出一种准确且高效的随机计算神经网络加速设计方案。

图2. 分别量化模型参数和激活值找出低精度网络准确率的瓶颈,即低精度的激活值

在神经网络模型结构方面,该工作提出将高精度残差与低精度数据通路相结合的新架构:通过将神经网络推断运算中占据最多运算量的卷积操作保持在较低的精度,保障整体电路的硬件效率;同时引入高精度的残差连接,大幅提升网络推断的准确性。该架构还将批归一化(BN)与激活函数融合,以进一步提高SC推理效率。

在电路方面,该工作分析了不同精度比特流的累加逻辑,并提出对残差比特流缩放因子做匹配处理的高精度残差模块,以及能够一次性实现BN、ReLU激活和输出重量化的融合激活函数模块。

图3. 所提出的SC友好的低精度量化神经网络及其所需电路支持

基于上述创新技术,课题组对提出的高精度残差设计与对照加速器进行了比较。比较结果表明,本研究的设计相比于侧重电路效率的原始设计,以1.3%的硬件代价,提高了9.4%推断准确率。而与侧重准确率的原始设计相比,所提出的高精度残差设计提高了3倍电路效率,同时保持准确率相当。

图4. 基于神经网络-SC电路协同优化,兼顾推理准确性和效率

总的来说,李萌与王润声研究团队提出了一种新的神经网络-SC电路协同优化设计,该设计在保持电路硬件效率的同时提高网络精度,这对于随机计算在边缘计算神经网络加速器中的应用具有重要意义。

北京大学集成电路学院博士研究生胡逸轩为第一作者,李萌与王润声为指导老师。